#### **PVT-aware Self-tuning Circuits**

#### Presented by: Navid Toosizadeh

### Supervised by: Prof. Safwat G. Zaky

Connections 2009

#### Process, Voltage, Temperature (PVT) Variations

Process variations make the quality of fabricated chips less predictable. How to deal with it? Use more & more conservative delay estimations (assume worst-case PVT) Resulting products? Large and leaky circuits (sub-100nm)

#### Process, Voltage, Temperature Variations

### **Undesired Over-engineering?**

### Is there any better way to design?

# **Self-tuning Circuits**

- They produce the best-possible results, given the **PRESENT** process, voltage, temperature.

- Don't worry about variations, design for TYPICAL conditions (not worst case)

- What if the chip is actually exposed to the worst conditions?

- An on-chip circuitry auto-corrects for a poor performance due to variations

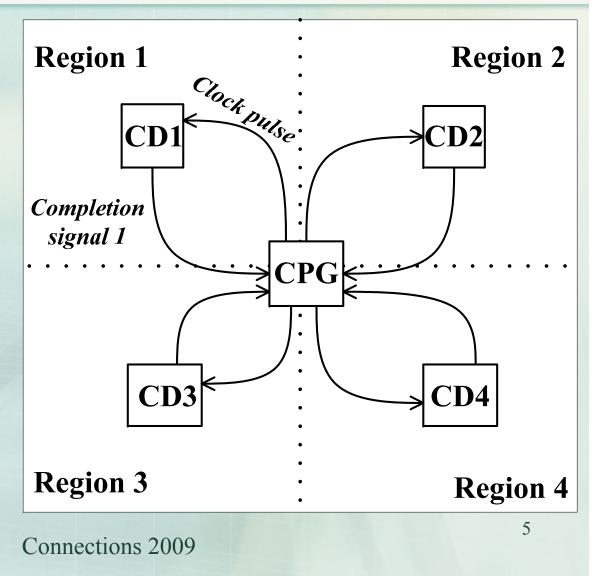

### **Self-tuning Mechanism**

<u>CD:</u> Composed of delay elements that match the critical path delay.

<u>CPG:</u> Creates a new clock pulse when all regions sent their completion signal.

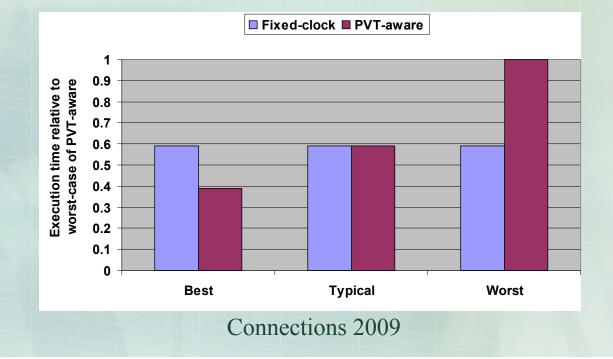

#### **Post-layout Results: Typical corner**

- Two DLX microprocessors, implemented in 90nm: one traditional (fixed-clock) and one PVT-aware.

- Results under TYPICAL PVT conditions (temp=25° C):

| Design           | Av. Leakage<br>(mW) | Av. Total<br>power (mW) | Total Ex.<br>Time (mS) |  |  |

|------------------|---------------------|-------------------------|------------------------|--|--|

| Traditional      | 1.242               | 38.402                  | 6.492                  |  |  |

| <b>PVT-aware</b> | 0.125               | 30.223                  | 6.492                  |  |  |

| Change           | 10X<br>Reduction    | 21%<br>Reduction        | Similar                |  |  |

| Connections 2009 |                     |                         |                        |  |  |

#### **Post-layout Results: Worst corner**

Results under WORST PVT conditions (temp=125° C):

| Design        | Av.<br>Leakage<br>(mW) | Av. Total<br>power<br>(mW) | Total Ex.<br>Time<br>(mS) | Power×<br>delay<br>(µ J) |

|---------------|------------------------|----------------------------|---------------------------|--------------------------|

| Trad.         | 59.193                 | 87.216                     | 6.502                     | 567.08                   |

| PVT-<br>aware | 8.092                  | 22.344                     | 11.023                    | 246.30                   |

#### Resilience to PVT variations, Amenability to voltage scaling

- Simulations verified that the PVT-aware processor produces the best-possible results with the interand intra-chip variations.

- The processor is amenable to voltage scaling.

### Conclusion

PVT-aware self-tuning circuits are viable solutions for today's shrinking technologies to:

- Deliver the required performance under typical conditions.

- Lower power consumption.

Help in handling process variations.

Reduce CAD and Design complexity.

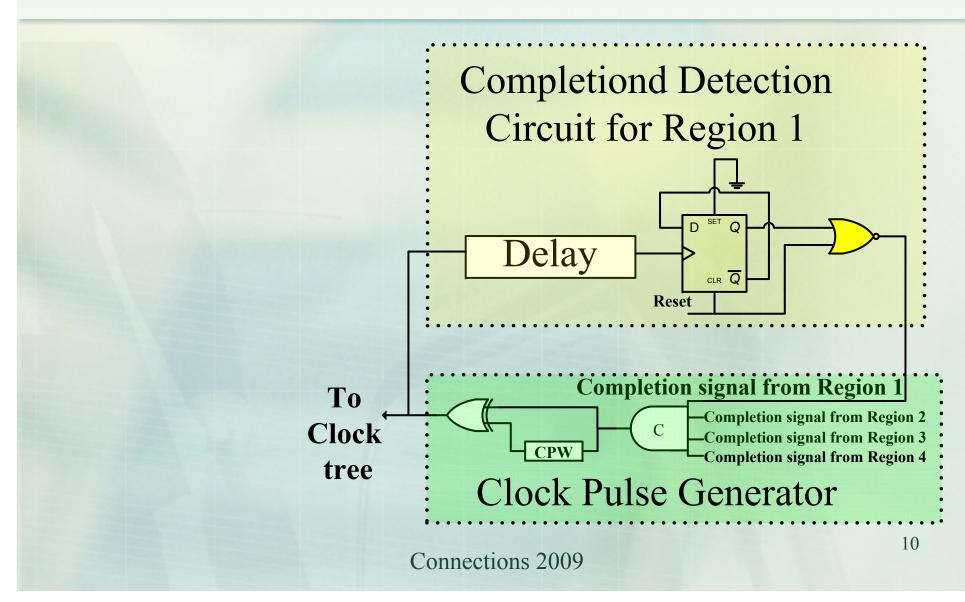

### **Clock Generation Schematic**

## **Clock Generation Schematic**

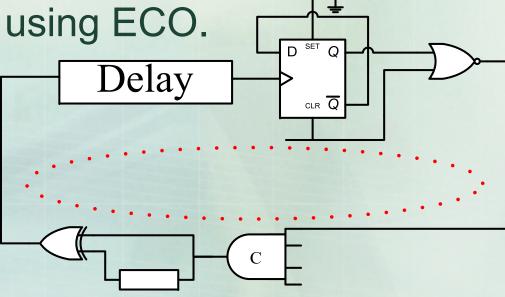

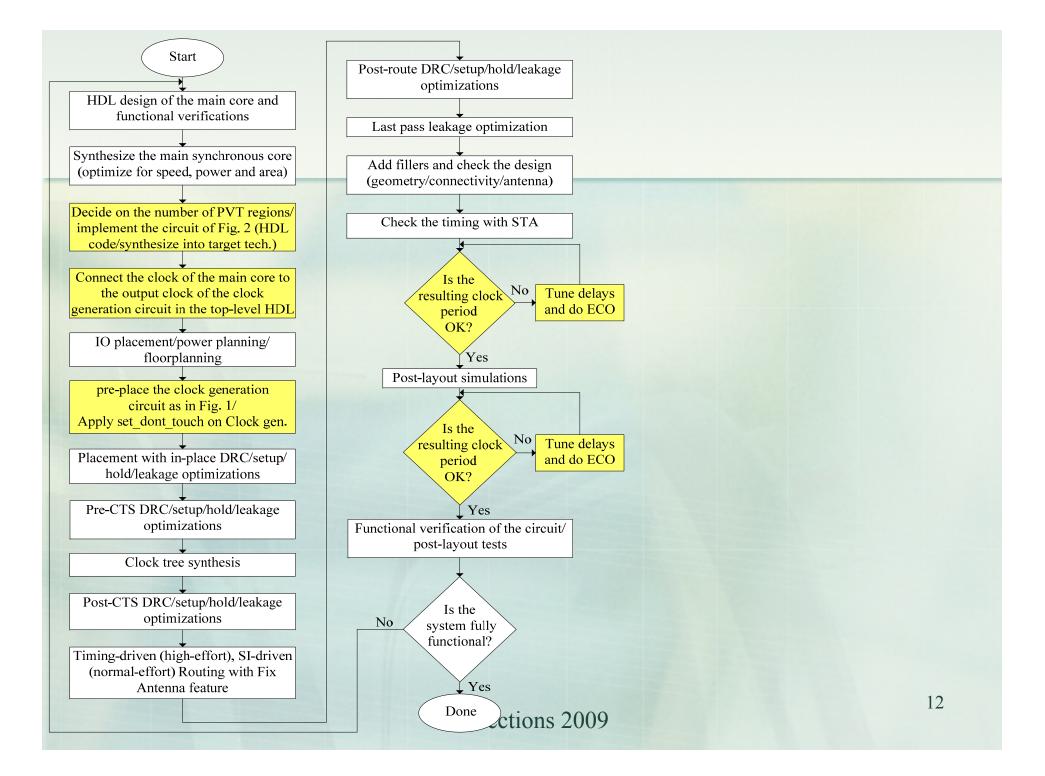

- The delay of the loop is tuned for the desired clock period.

- Fine-tune delays at the post-layout netlist using ECO.

#### How to connect to the environment?

Multiflop synchronizers

Multiplexer recirculation techniques

Use of first-in-first-out buffers between different clock domains

Handshake techniques