## University of Toronto Faculty of Applied Science and Engineering Midterm Examination

ECE 241S - Digital Systems Examiner: Belinda Wang, Jianwen Zhu

> 6:00 - 7:00pm, March 03, 2003 Duration: 60 minutes

ANSWER QUESTIONS ON THESE SHEETS, USING THE BACKS IF NECESSARY.

1. No calculator is allowed.

2. Weight for each question is indicated in []. Attempt all questions, since a blank sheet will certainly get a zero.

| Last Name:       |                  |    |

|------------------|------------------|----|

| First Name:      |                  |    |

| Student Number:  |                  |    |

| Lecture Section: |                  |    |

|                  | Section 01 (Zhu) | [] |

Section 02 (Wang) [ ]

## Maximum grade = 60

| Question | Mark |

|----------|------|

| 1        |      |

| 2        |      |

| 3        |      |

| 4        |      |

| 5        |      |

| 6        |      |

| 7        |      |

| 8        |      |

| Total    |      |

| Name: |  |

|-------|--|

|       |  |

**Problem 1** [5] Find all the decimal equivalents of the following binary numbers represented in two's complement scheme.

- 1. 1010101

- 2. 1111010

- 3. 0000001

- 4. 100000

- 5. 000000

**Problem 2** [6] For the logic expression  $f = x \oplus y \oplus z$ ,

1. Express f in canonical SOP form using boolean algebraic manipulation.

2. Draw the corresponding K-map for the logic function f.

| $\backslash$ |      |      |

|--------------|------|------|

|              |      |      |

|              | <br> | <br> |

|              |      |      |

3. Write f in canonical POS form.

Problem 3 [13] Given the canonical SOP form of a function

$$f = \overline{x_1} \, \overline{x_2} \, x_3 + \overline{x_1} \, x_2 \, \overline{x_3} + \overline{x_1} \, x_2 \, x_3 + x_1 \, x_2 \, \overline{x_3} + x_1 \, x_2 \, x_3$$

1. Represent the function f in a timing diagram

|                | : | : | : | : | • | : | : | : | : |

|----------------|---|---|---|---|---|---|---|---|---|

| v              | : | : | : | : | : | : | : | : | : |

| х <sub>1</sub> | : | : | : | : | : | : | : | : | : |

|                | : | : | : | : | : | : | : | : | : |

|                | : | : | • | : | : | : | : | : | : |

| x <sub>2</sub> | : | : | • | : |   | : |   |   | : |

| 2              | : | : | : | : | : | : | : | : | : |

|                | : | : | : | : | : | : | : | : | : |

| x <sub>3</sub> | : | : | : | : | : | : | : | : | : |

| - 3            | : | : | • | : | : | : | : | : | : |

|                | : |   | • | : | : | : |   | : | : |

|                | : | : | : | : | : | : | : | : | : |

| f              | : | : | : | : | : | : | : | : | : |

| •              | : | : | : | : | : | : | : | : | : |

|                | • | • | • | • | • | • | • | • | • |

|                | : | : | : | : | : | : | : | : | : |

2. Use algebraic manipulation to find the minimum-cost SOP for f.

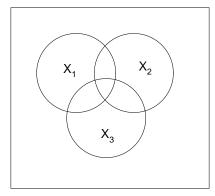

3. Show in the following Venn diagram where all five minterms (in the canonical SOP form of f) are located.

4. Write the minimum-cost POS form for the function f.

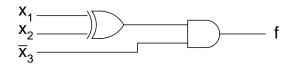

**Problem 4** [3] Draw an equivalent logic circuit as the one shown below using only NAND gates. (as fewer gates as possible, assuming that both the variables and their complements are available as primary inputs.)

**Problem 5** [8] Draw a CMOS implementation of the logic function  $f = (x_1 \oplus x_2) \overline{x_3}$  using as fewer transistors as possible.

Name: \_\_\_\_\_

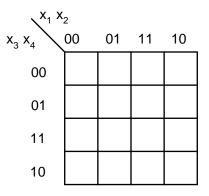

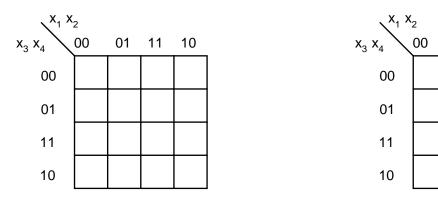

1. Generate a K-map for the function f.

2. Write the minimum-cost expression for f.

3. Evaluate the cost of implementing the function f assuming that both  $x_i$  and  $\overline{x_i}$  are available as inputs.

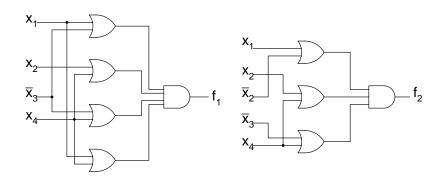

**Problem 7** [13] One of your classmates designed the following circuits. Your task is to make improvements in order to reduce overall cost of implementing both logic functions  $f_1$  and  $f_2$ .

01

11

10

1. Determine the total cost of implementing both  $f_1$  and  $f_2$ .

- 2. Write the logic expression for  $f_1$  and  $f_2$ .  $f_1 =$

- $f_2 =$

3. Draw the K-maps representing  $f_1$  and  $f_2$ .

4. Determine the minimum cost expressions for both  $f_1$  and  $f_2$ .

$f_1 =$

$f_2 =$

5. Draw the improved logic circuits for  $f_1$  and  $f_2$  and find the overall costs

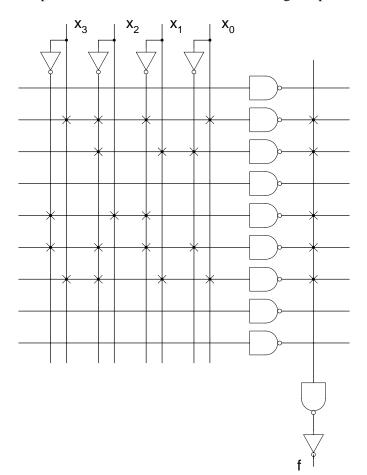

**Problem 8** [5] For the circuit implemented on the PLA below, write the logic expression for the output f.