# **University of Toronto**

# Faculty of Applied Science and Engineering

# **Department of Electrical and Computer Engineering**

# Midterm Examination

ECE 241F - Digital Systems Tuesday October 11, 2005, 6:00 – 7:30 pm

## **Duration: 90 minutes**

Examiners: S Brown, J. Rose, K. Truong and B. Wang

ANSWER ALL QUESTIONS ON THESE SHEETS, USING THE BACK SIDE IF NECESSARY.

1. No calculators and no cellphones are allowed.

2. The number of marks available for each question is indicated in the square brackets []; each portion of a question also shows how many marks are allocated to it.

3. There are two extra blank pages at the end of the test for rough work.

AID ALLOWED: The Course Textbook, Fundamentals of Digital Logic with Verilog Design.

| Last Name:       |                                                                          |  |

|------------------|--------------------------------------------------------------------------|--|

| First Name:      |                                                                          |  |

| Student Number:  |                                                                          |  |

| Lecture Section: | Section 01 (Rose) [ ]<br>Section 02 (Wang) [ ]<br>Section 03 (Brown) [ ] |  |

Section 04 (Truong) [ ]

**Total Available Marks:**

| Question           | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | Total |

|--------------------|---|---|---|---|---|---|---|---|-------|

| Marks<br>Available | 5 | 6 | 9 | 8 | 6 | 8 | 5 | 6 | 53    |

| Marks<br>Achieved  |   |   |   |   |   |   |   |   |       |

[5] Q1. Circuit analysis.

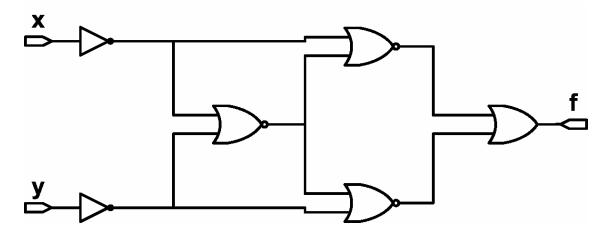

[2] (a) For the following circuit, give the truth table.

| Х | у | f |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

## Q1, continued.

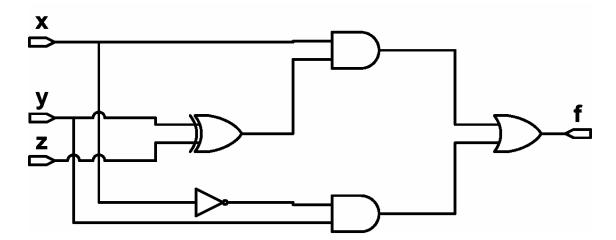

[3] (b) For the following circuit, give the truth table.

| х | у | z | f |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

Last Name

Student Number

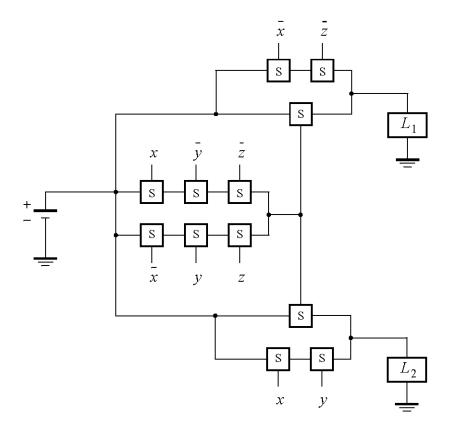

[6] Q2 In Section 2.1 of the textbook, circuits that turn a simple light, L, on or off are used to illustrate some basic logic functions. This questions involves some similar circuits with switches controlled by inputs x, y, or z.

[3] (a) Consider the circuit diagram shown below. You are to write logic expressions, in **sum-of-products** (SOP) form, for the functions  $L_1$  and  $L_2$  where each of these functions is 1 when the light is on and 0 when the light is off. Higher marks will be given for determining the simplest SOP expression possible.

**ANSWER** (it is **not necessary** to show the steps used to derive your answer):

Q2, continued.

[3] (b) Assume now that we need to implement a circuit that drives only light  $L_1$  from part (a). Draw the simplest circuit you can with switches like those shown in part (a) that implements only L<sub>1</sub> Higher marks will be given for a circuit that uses as few switches as possible.

**ANSWER** (it is **not necessary** to show the steps used to derive your answer):

Last Name

Student Number

[9] Q3. For this question you are to use algebraic manipulation to produce minimal cost sum-of-products (SOP) or product-of-sums (POS) expressions. You need to show your work and the steps that are being used in your solution. Higher marks will be given for solutions that apply the theorems and identities of Boolean algebra in as few steps as possible. So, you are to show all of your steps, but don't use more steps than needed.

[3] (a) Use Boolean algebra to minimize the following expression. Your final answer should be the minimal cost **sum-of-products** (SOP) form for this function.

$f = y\overline{z} + (\overline{x} + \overline{z})(x + y + \overline{z})$

Q3, continued.

[3] (b) Use Boolean algebra to minimize the following expression. Your final answer should be the minimal cost **sum-of-products** (SOP) form for this function.

$f = x \cdot \overline{z} + x \cdot y + \overline{x} \cdot \overline{y} + \overline{y} \cdot z$

Last Name\_\_\_\_\_Student Number\_\_\_\_\_

Q3, continued.

[3] (c) Use Boolean algebra to minimize the following expression. Your final answer should be the minimal cost **product-of-sums** (POS) form for this function.

$f = y + xz + \overline{x}\overline{z}$

Last Name\_\_\_\_\_Student Number\_\_\_\_\_

## [8] Q4. Karnaugh maps.

[2] (a) For the Karnaugh map shown below, derive the minimal cost sum-of-products (SOP) form for the logic function f(x,y,z).

|   | xy | 00 | 01 | 11 | 10 |

|---|----|----|----|----|----|

| Z | 0  | 1  | 0  | 1  | 0  |

|   | 1  | 1  | 1  | 0  | 1  |

#### **ANSWER**:

[2] (b) Derive the minimal cost product-of-sums (POS) form for the logic function f (a,b,c,d).

|    | ab | 00 | 01 | 11 | 10 |

|----|----|----|----|----|----|

| cd | 00 | 0  | 0  | 0  | 1  |

|    | 01 | 1  | 0  | 0  | 1  |

|    | 11 | 0  | 0  | 1  | 1  |

|    | 10 | 0  | 1  | 0  | 0  |

**ANSWER**:

[4] (c) Derive the minimal cost sum-of-products (SOP) form for the logic function f (a,b,c,d,e). Note that '×' is a don't care output.

| e=0 |    |    |    |    |    |    | e= | =1 |    |    |    |

|-----|----|----|----|----|----|----|----|----|----|----|----|

|     | ab | 00 | 01 | 11 | 10 |    | ab | 00 | 01 | 11 | 10 |

| cd  | 00 | 1  | 0  | ×  | 1  | cd | 00 | 1  | 0  | 1  | ×  |

|     | 01 | 0  | ×  | 0  | 0  |    | 01 | 1  | ×  | 0  | ×  |

|     | 11 | 0  | 0  | 1  | 0  |    | 11 | 1  | 0  | 0  | ×  |

|     | 10 | ×  | 0  | 0  | 1  |    | 10 | 1  | 1  | 1  | ×  |

#### Last Name\_

Student Number

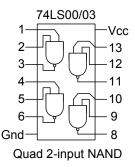

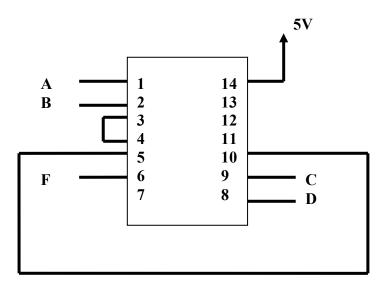

[6] Q5. A student in ECE 241 has been asked to wire up a single TTL 74LS00 QUAD 2-input NAND gate chip (the pin-out of which is given below) to implement the logic function  $\mathbf{F} = \mathbf{AB} + \mathbf{CD}$ . Below you will see the wiring diagram that student has created. The circuit doesn't work because it has **exactly three** errors or omissions. Your answer, on the next page, should be the <u>changes</u> that need to be made to the circuit to make it function correctly. For example, a change could be "connect pin 3 to pin 12."

Pin-out Diagram for the 74LS00:

Below is the wiring diagram of the student's circuit;

(question continues on next page)

Last Name\_\_\_\_\_Student Number\_\_\_\_\_

Q5, continued.

Working space:

**ANSWER**:

Correction #1:

Correction #2:

Correction #3:

### Last Name\_\_\_\_

## [8] Q6. Word problem

[3] (a) A museum has three rooms, each with a motion sensor  $(m_1, m_2, and m_3)$  that outputs 1 when motion is detected. At night, the only person in the museum is one security guard who walks (i.e. no standing still, or sitting, or sleeping) from room to room. Give a truth table for the security system that sounds an alarm (by setting an output *A* to 1) if motion is ever detected in more than one room at a time. (*Hint: be sure to include any don't care in the output.*)

| $m_1$ | m <sub>2</sub> | m <sub>3</sub> | А |

|-------|----------------|----------------|---|

| 0     | 0              | 0              |   |

| 0     | 0              | 1              |   |

| 0     | 1              | 0              |   |

| 0     | 1              | 1              |   |

| 1     | 0              | 0              |   |

| 1     | 0              | 1              |   |

| 1     | 1              | 0              |   |

| 1     | 1              | 1              |   |

[5] (b) Now consider a museum with 7 rooms. A truth table is not a good choice (it has too many rows), nor is an equation describing when the alarm should sound (it has too many terms). However, the inverse of the alarm function can be straightforwardly captured as a logic equation, and then the desired circuit (*A*) can be achieved by adding an inverter to the inverse function ( $\overline{A}$ ). Design the 7-room security system by expressing the inverse of the alarm function,  $\overline{A}$  (m<sub>1</sub>, m<sub>2</sub>, m<sub>3</sub>, m<sub>4</sub>, m<sub>5</sub>, m<sub>6</sub>, m<sub>7</sub>).

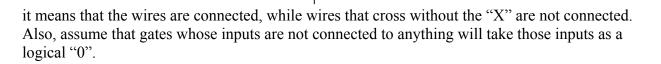

[5] Q7. The following schematic represents a programmable logic device that has been programmed. Assume that when two wires that cross are annotated as follows:

✻

(question continues on next page)

Q7, continued.

[2] (a) Redraw the circuit in the simplest form you can.

[3] (b) What is this circuit?

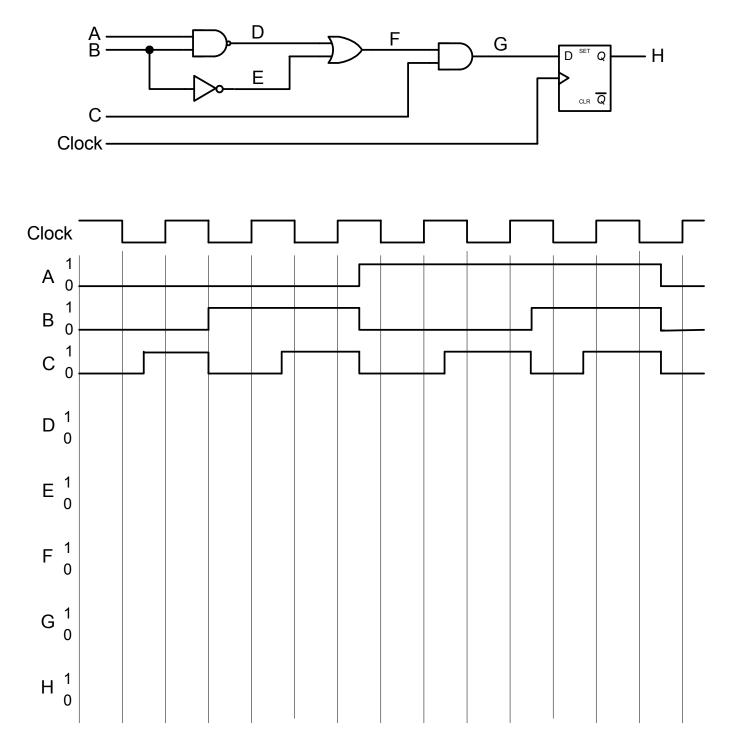

[6] Q8. Consider the circuit shown below. Assume there are no propagation delays in the gates and in the D flip-flop. Draw the timing diagram showing D, E, F, G and H.