# Lab 4: Operational Amplifier

## Introduction

The operational amplifier (opamp) is a device that performs amplification of its two input voltages. Opamps are often used as means of detecting and amplifying error in feedback systems. Noninverting and inverting amplifiers based on an opamp are good examples of applications of an opamp in feedback systems.

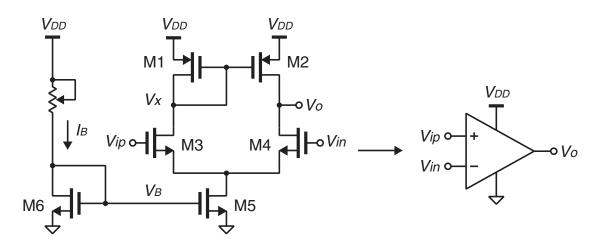

In this lab, you are to analyze, simulate, and test the basic CMOS opamp shown in Figure 1. The supply voltage  $(V_{DD})$  is 5 V in this lab.

## Preparation

Go through the following preparation steps for the opamp in Figure 1.

1. For this opamp: Differential gain  $(A_d) = -g_{m4}(r_{o4}||r_{o2})$

Common-mode gain  $(A_c) = -g_{m4}r_{o4}\frac{1/g_{m2}}{2g_{me4}r_{o4}r_{o5}+1/g_{m2}} \approx -1/2g_{m2}r_{o5}$

Common-mode rejection ratio (CMRR) =  $A_d/A_c = 2g_{m2}g_{m4}r_{o5}(r_{o4}||r_{o2})$

and the bandwidth  $(f_{3dB}) = 1/2\pi (r_{o4}||r_{o2})C_L$

- 2. Find the numerical values for  $A_d$ ,  $A_c$ , CMRR, and  $f_{3dB}$  for  $I_B = 1$  mA and  $C_L = 1$  nF.

- 3. Find the input common-mode voltage that maximize the output swing.

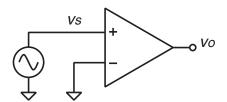

- 4. For Figure 2, if the opamp input is decomposed into differential and common-mode components, they can be expressed as:

$$v_d = v_{ip} - v_{in} = v_s - 0 = v_s$$

$v_c = (v_{ip} + v_{in})/2 = (v_s + 0)/2 = v_s/2$

5. Run AC simulations to show  $A_d$ ,  $A_c$  and CMRR at low frequencies. Also run a DC simulation to show the output swing with a differential input with the common-mode voltage found in 3. Label and comment on the plots to clearly show the results.

Figure 2: An opamp with a single-ended input.

|         | Table 1: Minimum parts list            |          |

|---------|----------------------------------------|----------|

| Part    | Description                            | Quantity |

| ALD1101 | NMOS transistor pair                   | 2        |

| ALD1102 | PMOS transistor pair                   | 1        |

| -       | 10-k $\Omega$ multi-turn potentiometer | 3        |

### Lab

#### **1.** SPICE simulation challenge

The first part of this lab will be an LTSpice simulation challenge that will be announced at the beginning of the lab session by your TA. You will work in groups of two and have 50 minutes to finish. Completing the preparation part of the lab and general knowledge of the course should be enough to finalize this part.

#### 2. Experiments

A minimum parts list for this lab is shown in Table 1. This is the absolute minimum. You may bring more parts for your convenience and backup.

- 1. Assemble the opamp shown in Figure 1 on the breadboard

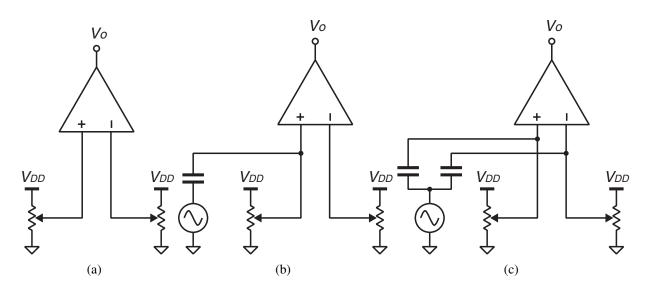

- 2. Adjust the bias current  $(I_B)$  to 1 mA, and set the opamp inputs to the common-mode voltage found in preparation using two multi-turn potentiometers as shown in Figure 3(a).

- 3. Adjust one of the opamp input for  $V_o = V_x$  (see Figure 1) where the opamp is at equilibrium. The opamp differential input at the equilibrium is the offset voltage of the opamp. Do not turn the potentiometers from this point.

- 4. Connect one of the opamp inputs to a signal generator via a large capacitor as shown in Figure 3(b) and find the differential gain  $(A_d)$  of the opamp.

- 5. Connect both of the opamp inputs to a signal generator via separate capacitors as shown in Figure 3(c) and find the common-mode gain  $(A_c)$  of the opamp. Calculate the CMRR.

- 6. Insert a 1-nF load capacitor at the opamp output and find the  $f_{3dB}$ .

- 7. Compare the experimental results with simulation. Explain and justify any discrepancy.

Figure 3: (a) Circuit configurations for offset cancellation, (b) differential gain  $(A_d)$  measurement, and (c) common-mode gain  $(A_c)$  measurement.