# **University of Toronto**

### **Final Exam**

Date - Apr 28, 2009

Duration: 2.5 hrs

ECE334 — Digital Electronics Lecturer - D. Johns

#### ANSWER QUESTIONS ON THESE SHEETS USING BACKS IF NECESSARY

- 1. Assume the parameters on the parameter sheet (last page) unless otherwise stated (mosfets are from a 0.25um CMOS technology)

- 2. Single handwritten aid sheet allowed.

- 3. Only tests written in pen will be considered for a re-mark.

- 4. Grading indicated by []. Attempt all questions since a blank answer will certainly get 0.

| Student #:           | (max grade = | (max grade = 41) |  |  |

|----------------------|--------------|------------------|--|--|

| First Name:          | Total        |                  |  |  |

|                      | 7            |                  |  |  |

| Last Name: SULUTIONS | . 6          |                  |  |  |

| (1)/11/2/16          | 5            |                  |  |  |

|                      | 4            |                  |  |  |

|                      | 3            |                  |  |  |

|                      | 2            |                  |  |  |

|                      |              |                  |  |  |

Question

Mark

- [5] Question 1: Answer the True [T] or False [F] questions below by circling the correct answer. Each correct answer is worth 0.5 marks.

- T F Trench capacitors in DRAM memory arrays are implemented differentially to reduce noise effects.

- T F In clock distribution using both grid and H-trees, a grid is used for global clocking while H-trees are used for local clock distribution.

- T Bond wires used in IC packaging connect the bond pad to the lead frame of the package.

- T F Although through-hole pin packages result in less PCB density than SMT packages, through-hole pin packages are good for high speed due to less inductance.

- T Phase-locked-loops are commonly used to build clock multipliers through the use of a clock divider in the feedback portion of the PLL.

- T (F) NOR flash memory is generally more dense than NAND flash memory.

- T F DRAM memory is normally built in standard CMOS technology.

- (T) F SRAM memory is normally built in standard CMOS technology.

- T F When the clock is routed in the same direction as data signals in sequential logic, race conditions are more likely than when the clock is routed in the opposite direction.

- The purpose of using  $V_{DD}/2$  for the trench capacitors back bias is to reduce voltage stress on the trench capacitors.

Last Name: \_\_\_\_\_

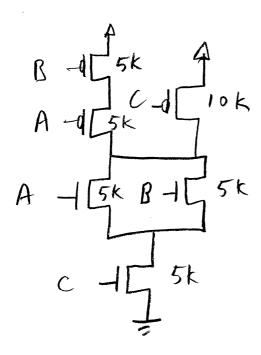

[6] Question 2: Implement the equation  $X = (\overline{A} \bullet \overline{B}) + \overline{C}$  using CMOS logic assuming that A, B, C are all available as inputs. Assume that the transistors have been sized to give an output resistance of 10k for the worst-case input pattern (in both the high output and low output cases). Find the input pattern, ABC, that gives the lowest output resistance when the output is low. Also find the value of that resistance,  $R_{\text{out}}$ .

$$X = (\bar{A} \cdot \bar{B}) + \bar{c}$$

$$= (\bar{A} \cdot \bar{B}) + \bar{c}$$

$$= (\bar{A} + \bar{B}) c$$

$$R_{\rm out} = 7.5k$$

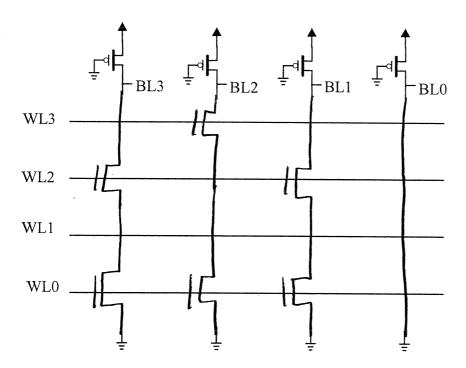

[6] Question 3: a) Add the NMOS transistors in the shown 4x4 MOS NAND ROM to store the following data:

| BL3 | BL2   | BL1 | BL0 |  |

|-----|-------|-----|-----|--|

| 0   | 0 1 0 |     | 0   |  |

| 1   | 0 1   |     | 0   |  |

| 0   | 0 0 0 |     | 0   |  |

| 1   | 1     | 1   | 0   |  |

b) What is the main advantage of a MOS NAND ROM over a MOS NOR ROM and why does it occur?

-NAND IS MORE DEME, OR IN STHER WURDS, LESS AREA FOR SAME NUMBER OF BITS

-NO POWER SUPPLIES NEED TO BE ROUTED WITHIN MEMORY CORE AREA

[6] Question 4: Find the propogation delay of each inverter  $(t_{p1}, t_{p2}, t_{p3})$  in the ring oscillator below (only account for gate capacitance  $(WLC_{ox})$ ) and the shown 5pF capacitance. Also find the oscillation frequency,  $f_{osc}$ . Assume n-channel transistors are sized 0.5um/0.25um while p-channel transistors are sized 1.5um/0.25um.

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6) + (1.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(6)(0.25)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(6)(6)(2.5)(6)$$

$$C_{1} = C_{2} = C_{3} = (0.5)(6$$

[6] Question 5:

a) Explain the mechanism of Fowler-Nordheim tunneling.

A HIGH ELECTRIC FIELD ACROSS A THIN LAYER OF S: 02 CAUSES ELECTRONS TO TUNNEL THROUGH S: 02

b) Explain the mechanism of hot carrier injection.

A HIGH VELOCITY DRAIN SOURCE CURRENT (DUE TO LARGE ELECTRIC FIELD FROM DRAIN-) SOURCE CAUSES SOME ELECTRONS TO TUMP ACROSS GATE OXIBE

c) Which mechanism causes more damage to the oxide and therefore limits the number of programs/erase cycles of non-volatile memories?

HOT CARRIER INJECTION CAUSES MURE DANAGE TO THE OXIDE

d) What mechanism is used to erase EPROM memory? (not EEPROM or Flash but only EPROM).

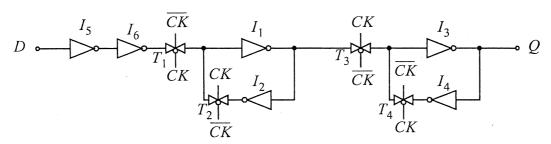

PHOTO ELECTRIC EFFECT. BY SHINING UV LIGHT ON CHIP DISCHARGHES ANY FLOATING CHARGES. [6] Question 6: Consider the "d" register shown below.

Assuming that CK and  $\overline{CK}$  occur at the same time, and defining the following delays:

$T_{I_i}$  is the delay through the *i* 'th inverter

$T_{G_i}$  is the delay through the i 'thT-gate from its clock input to its output

$T_{T_i}$  is the delay through the *i* 'thT-gate from its "data" input to its output

a) Find  $T_{\text{setup}}$  in terms of  $T_{I_i}$ ,  $T_{G_i}$  and  $T_{T_i}$  (be specific in terms of i).

b) Find  $T_{\mathrm{pcq}}$  in terms of  $T_{I_i}$ ,  $T_{G_i}$  and  $T_{T_i}$  (be specific in terms of i).

$$Tpcq = T_{T_3} + T_{I_3}$$

$$f$$

$$\begin{pmatrix} 0R \\ T_{G_3} \end{pmatrix}$$

$$T_{\text{peq}} = T_{T_3} + T_{I_3}$$

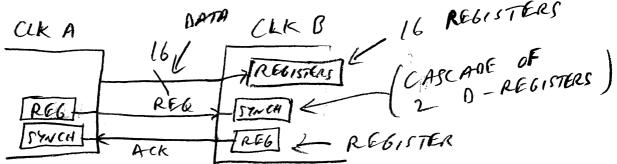

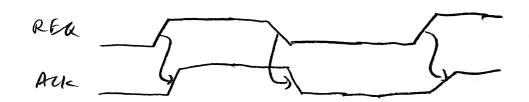

[6] Question 7: It is required to transfer a 16 bit bus across 2 asynchronous clock domains. Show how this is achieved using a 2 phase handshake. (Draw block diagrams, clock timing diagrams and words to make it clear).

- REG CHANGES LOGIC LEVEL INDICATES

STABLE

INDICATES - ACK CHANGE LOGIC LEVEL

READ

- REG LINE REGULES SYNCHRONIZER

- ACK LINE REGULES SYNCHRONIZER

- DATA DUES NOT AS IT WILL BE STABLE BY USING ABOVE HAND SHAKE

Last Name.

(blank sheet for scratch calculations)

#### ECE334F

# **Digital Electronics**

**Parameter Sheet**

**Physical Constants**;

$$\phi_T = kT/q = 26 \text{mV (at 300K)}; \ k = 1.38 \times 10^{-23} \text{ J/K}; \ T = 300 \text{ K (at 27°C)}; \ q = 1.6 \times 10^{-19} \text{ C};$$

$\varepsilon_O = 8.854 \times 10^{-12} F/\text{ m}; \ k_{OX} = 3.9; \ \phi_S = 2|\phi_F| = 0.6 V$

MOS Transistor: CMOS basic parameters. Channel length =  $0.25 \,\mu m$ ,  $m_j = 0.5$ ,  $\phi_o = 0.9 \,\mathrm{V}$

|      | V <sub>T0</sub> (V) | γ<br>( ν <sup>0.5</sup> ) | $\mu C_{ox}$ $(\mu A / V^2)$ | λ<br>( v <sup>-1</sup> ) | $C_{ox}$ $(fF/ \mu m^2)$ | C <sub>o</sub><br>(fF/ μm) | $C_j$ $(fF/\mu m^2)$ | C <sub>jsw</sub><br>[fF/ μm] |

|------|---------------------|---------------------------|------------------------------|--------------------------|--------------------------|----------------------------|----------------------|------------------------------|

| NMOS | 0.4                 | 0.4                       | 120                          | 0.06                     | 6                        | 0.3                        | 2                    | (see<br>below)               |

| PMOS | -0.4                | 0.4                       | 30                           | 0.1                      | 6                        | 0.3                        | 2                    | (see<br>below)               |

$V_{T0}$  is the threshold voltage with zero bulk-source voltage.

γ is used to account for non-zero bulk-source voltage.

$\mu C_{ox}$  is the transistor current gain parameter.

$\boldsymbol{\lambda}$  is to account for the transistor finite output impedance (channel length modulation).

$C_{ox}$  is the gate capacitance per unit area.

$C_o$  is the gate overlap capacitance per unit length.

$C_i$  is the drain/source junction capacitance per unit area.

$C_{jsw}$  is the drain/source junction capacitance per unit length to account for drain/source perimeter capacitance. Assume this value is the same for all perimeters **except under the gate**.

$C_{isw} = 0.3 fF/ \mu m$  for both NMOS and PMOS

$C_{jswg}$  is the drain/sourc junction capacitance per unit length under the gate.

$C_{jswg} = 0.15 \, fF/ \, \mu m$  for both NMOS and PMOS