# UTDSP: A VLIW Programmable DSP Processor

by

### Sean Hsien-en Peng

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto

© Copyright by Sean Hsien-en Peng 1999

### **UTDSP: A VLIW Programmable DSP Processor**

Sean Hsien-en Peng

Master of Applied Science, 1999

Graduate Department of Electrical and Computer Engineering

University of Toronto

### **Abstract**

VLIW architectures are well-suited for implementing application-specific programmable processors because of their great scalability and modularity. VLIW architectures take advantage of not only temporal parallelism found in RISC architectures but also spatial parallelism by using multiple functional units. However, the large instruction storage and bandwidth requirements have prevented VLIW architectures from being used in cost-sensitive systems.

This thesis describes a VLIW DSP processor called UTDSP, which incorporates a novel and flexible instruction packing and fetching mechanism to reduce the code size and bandwidth problems plaguing other VLIW architectures. With this scheme it is possible to actually achieve some code compression while attaining significant performance speedup over a traditional architecture. The UTDSP is flexible in that additional functional units with application-specific instructions can be easily added when required for performance with little impact on its compiler.

The VLSI design and implementation of the UTDSP is presented. This implementation, consisting of five pipeline stages, is capable of executing seven instructions per cycle and provides zero-overhead hardware loops that are nestable and interruptable. A GUI-based assembly debugger and architecture simulator were implemented. The UTDSP adopts a synthesis-based design methodology and a novel hierarchical CAD flow that can significantly reduce its area.

To Hsiao-ching, Hsien-yuan, and Yu-liang

# Acknowledgements

This thesis could not have been completed without the help of many individuals and organizations, to whom I am extremely grateful.

I want to thank my supervisor, Professor Paul Chow, for his precious suggestions, friendly advice, and considerable amount of time that was spent to reading the many drafts of my thesis. Most of all, however, for his patience and encouragement.

I would like to thank Natural Sciences and Engineering Research Council for their funding in the past two years. I could not have had the chance to carry out my research at U of T without the financial support from NSERC.

I offer thanks to Louis Zhang, Jianghong Hu, Brent Beacham, Nirmal Sohi, Deshanand Singh, Warren Gross, Andy Ye, and Tor Aamodt for all the good times and numerous technical discussions from which I have learned much. Thanks to Dr. Mazen Saghir for defining a clear framework in this research project and for his technical help. Thanks also to An Wei, Jin Heng, Jianhui, Michael, Franklin, Edward, and Shuo for all the fun times in the lab.

I am extremely grateful to my family for all their support and ever-lasting love. Last, but certainly not least, I would like to thank my wife Hsien-yuan for her love, understanding, and sacrifice of countless weekends and holidays in the past years. This thesis involved a lot of hard work and months struggling with CAD tools. I could not have done it without her support.

# **Table of Contents**

| CHAP  | TER 1 Introduction                                                                         | 1  |

|-------|--------------------------------------------------------------------------------------------|----|

| 1.1   | Motivation                                                                                 | 1  |

| 1.2   | Objective and Contributions                                                                |    |

|       | 1.2.1 Design and Implementation of a Long-instruction Packer                               |    |

|       | 1.2.2 Design and Implementation of Architecture Simulator and GUI-based Assably Debugger 2 |    |

|       | 1.2.3 Design and VLSI Implementation of the UTDSP                                          | 2  |

| 1.3   | Thesis Organization                                                                        | 3  |

| CHAP' | TER 2 Background                                                                           | 4  |

| 2.1   | Application-Driven Design Methodology                                                      | 4  |

| 2.2   | The Model Architecture                                                                     |    |

| 2.3   | C Compiler and Post-Optimizer                                                              |    |

| 2.4   | TI VelociTI and Philips R.E.A.L DSP Architectures                                          |    |

|       | 2.4.1 TI VelociTI Architecture                                                             |    |

|       | 2.4.2 Philips R.E.A.L. DSP Architecture                                                    |    |

| 2.5   | Summary                                                                                    | 16 |

| CHAP' | TER 3 Long-Instruction Packing and Fetching for the UTDSP                                  | 17 |

| 3.1   | Storing and Decoding Long Instructions                                                     | 17 |

|       | 3.1.1 Reducing the Size of Decoder Memory                                                  |    |

| 3.2   | Achieving Denser Instruction Packing                                                       |    |

|       | 3.2.1 Field Clustering Method                                                              |    |

|       | 3.2.2 Sharing Packing Slots                                                                |    |

|       | 3.2.3 Choosing the Number of Clusters in the UTDSP                                         | 25 |

|       | 3.2.4 The UTDSP Packing Algorithm                                                          | 26 |

| 3.3   | Implementation of the UTDSP Packing Software System                                        |    |

|       | 3.3.1 Implementing the UTDSP Packer Using C++ Template Technology                          | 28 |

| 3.4   | Results and Analysis                                                                       | 31 |

|       | 3.4.1 Packing Mechanism used for TI VelociTI architecture                                  |    |

|       | 3.4.2 Benchmark Results for the UTDSP Packer and the VelociTI Algorithm                    |    |

|       | 3.4.3 Impact of the Two-Cluster Packing and Fetching on Execution Performan 36             | ce |

| 3.5   | Summary                                                                                    | 37 |

| <b>CHAP</b> | ΓER 4 Development Tools                                       | 38 |

|-------------|---------------------------------------------------------------|----|

| 4.1         | Behavioural Modelling Methods for the UTDSP                   | 39 |

|             | 4.1.1 Choosing the Correct Modelling Language                 |    |

|             | 4.1.2 Digital Systems Modelling Techniques for the UTDSP      |    |

| 4.2         | Design and Implementation of the UTDSP Architecture Simulator | 42 |

|             | 4.2.1 Creating the Object Model of the UTDSP                  | 43 |

|             | 4.2.2 Simulating the UTDSP Object Model                       | 44 |

| 4.3         | The GUI-Based Assembly Language Debugger                      | 46 |

|             | 4.3.1 The Features of the Assembly Language Debugger          |    |

|             | 4.3.2 Adding Self-Displaying and Event-Listening Abilities    | 46 |

| 4.4         | Summary                                                       | 50 |

| CHAP        | ΓER 5 System Design and VLSI Implementation of the UTDSP      | 51 |

| 5.1         | The UTDSP Hardware Architecture                               | 51 |

| 5.2         | Instruction Set                                               | 53 |

| 5.3         | The Pipeline Architecture                                     | 54 |

|             | 5.3.1 Data Hazards and Bypassing                              | 54 |

|             | 5.3.2 Control Hazards and Zero-Overhead Looping Instructions  |    |

|             | 5.3.3 Interrupt Effects                                       | 57 |

| 5.4         | The PC Unit                                                   | 58 |

| 5.5         | The Register Files                                            | 60 |

| 5.6         | The Datapath Components                                       | 62 |

|             | 5.6.1 The 1.15 Fixed-Point Format                             | 62 |

|             | 5.6.2 The Modulo Address Generator                            | 63 |

| 5.7         | VLSI Implementation Issues                                    | 64 |

|             | 5.7.1 Design Capture and Synthesis                            | 65 |

|             | 5.7.2 Floorplanning                                           | 68 |

| 5.8         | Kernel Benchmarks                                             | 70 |

| 5.9         | Summary                                                       | 75 |

| CHAP'       | ΓER 6 Conclusions and Future Work                             | 76 |

| 6.1         | Conclusion                                                    | 76 |

| 6.2         | Future Work                                                   |    |

|             |                                                               |    |

| Appen       | dix A: UTDSP Instruction Set                                  | 78 |

| Bibliog     | raphy                                                         | 81 |

# **List of Figures**

| Figure 2.1: | Application-driven design methodology                                                                                                                                | 5  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2: | Example long instruction for a VLIW with 5 functional units                                                                                                          | 8  |

| Figure 2.3: | VLIW Model Architecture                                                                                                                                              | 8  |

| Figure 2.4: | Basic Structure of Instruction Decoder                                                                                                                               | 10 |

| Figure 2.5: | Two-phase compilation: C Compiler and Post-Optimizer                                                                                                                 | 12 |

| Figure 2.6: | The TI VelociTI Architecture                                                                                                                                         | 13 |

| Figure 2.7: | The Philips R.E.A.L DSP architecture                                                                                                                                 | 15 |

| Figure 3.1: | Block diagram of the UTDSP memory system                                                                                                                             | 18 |

| Figure 3.2: | (A) Multi-op instructions stored in an arbitrary manner (B) Multi-op instructions stored according to field priorities                                               |    |

| Figure 3.3: | (A) Storing multi-op instructions in their original format (B) Storing multi-op instructions in a packed format                                                      |    |

| Figure 3.4: | Field clustering packing method                                                                                                                                      | 21 |

| Figure 3.5: | Combining the two-cluster packing and slot-sharing methods                                                                                                           | 23 |

| Figure 3.6: | The UTDSP packing algorithm                                                                                                                                          | 27 |

| Figure 3.7: | The UTDSP packer and software system                                                                                                                                 | 29 |

| Figure 3.8: | Generic linked list in C                                                                                                                                             | 30 |

| Figure 3.9: | Container template class List <t> in C++</t>                                                                                                                         | 31 |

| Figure 3.10 | : Packing mechanism in the TI VelociTI architecture                                                                                                                  | 32 |

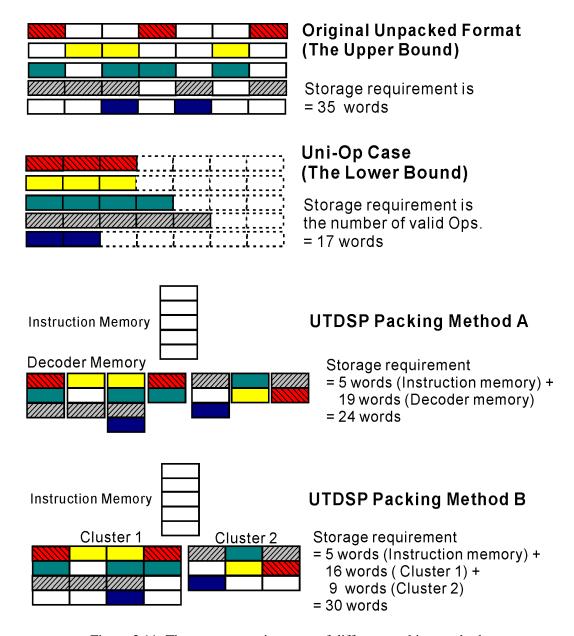

| Figure 3.11 | : The storage requirements of different packing methods                                                                                                              | 34 |

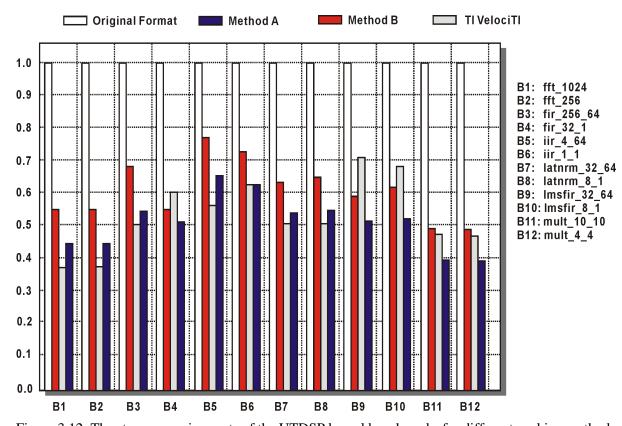

|             | : The storage requirements of the UTDSP kernel benchmarks for different packin methods                                                                               | ıg |

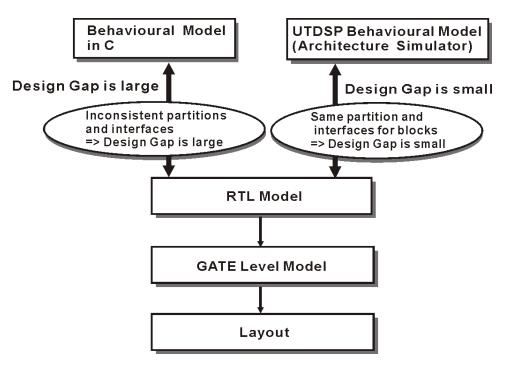

| Figure 4.1: | Design Gap between behavioural and RTL models                                                                                                                        | 39 |

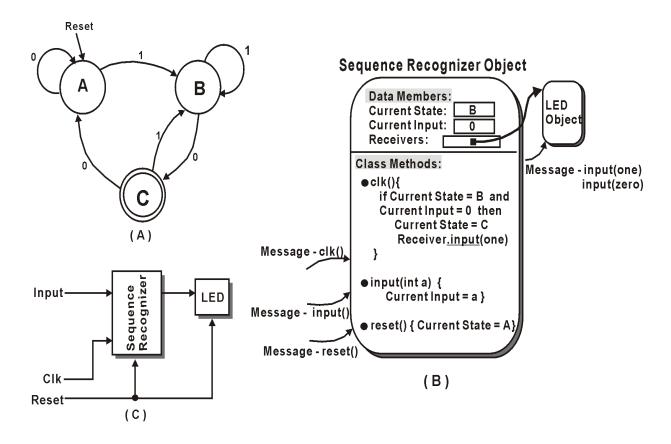

| Figure 4.2: | (A) An FSM that accepts input sequence "10". (B) The FSM's equivalent object me el. (C) The resulting digital system blocks converted directly from the object mo 41 |    |

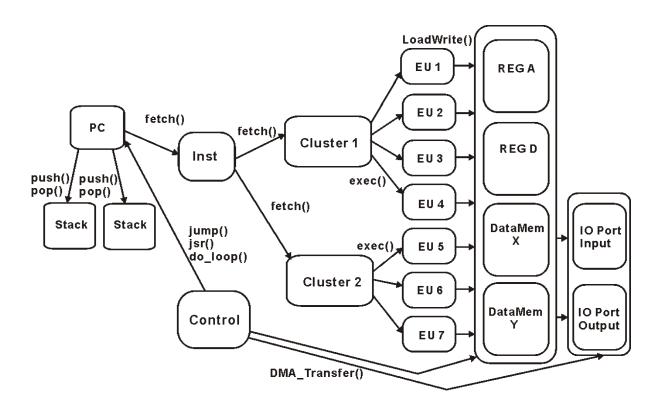

| Figure 4.3: | The object model of the UTDSP                                                                                                                                        | 44 |

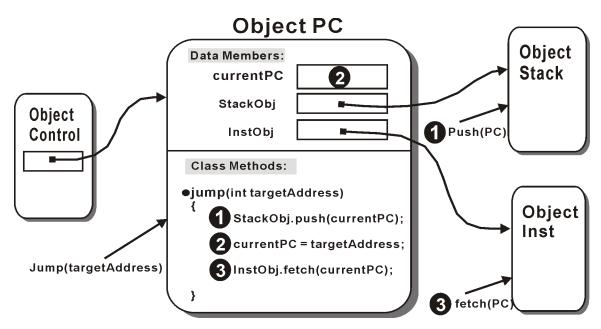

| Figure 4.4: | Connecting and simulating the objects in the UTDSP model                                                                                                             | 45 |

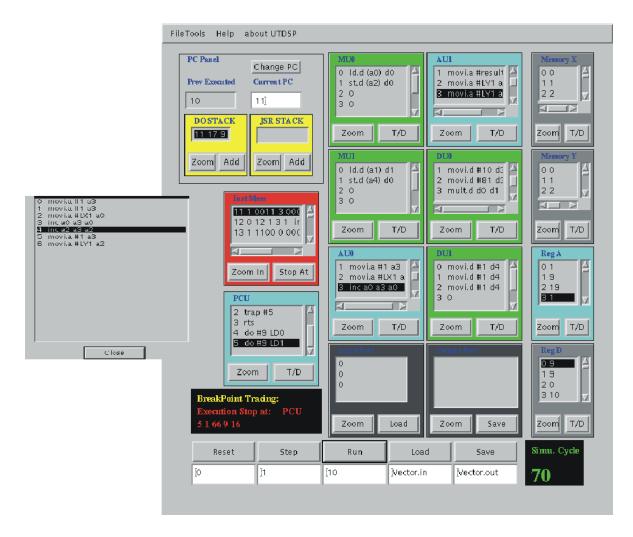

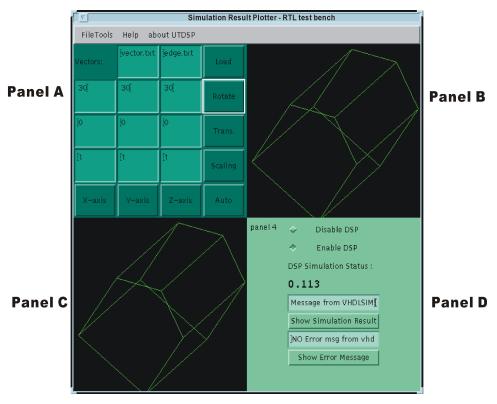

| Figure 4.5: | The UTDSP assembly language debugger                                                                                                                                 | 47 |

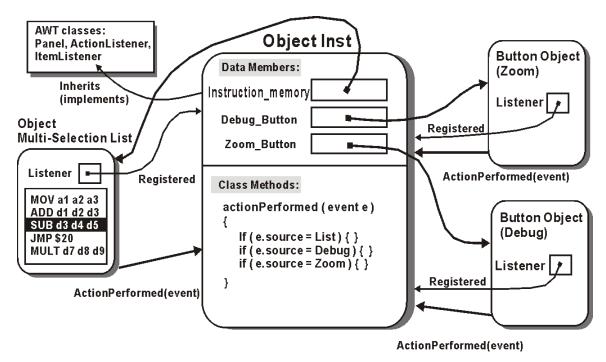

| Figure 4.6: | The Inst object with self-displaying and event-listening abilities                                                                                                   | 48 |

| Figure 4.7:  | A simulation result plotter and a test bench for RTL model                               | .49 |

|--------------|------------------------------------------------------------------------------------------|-----|

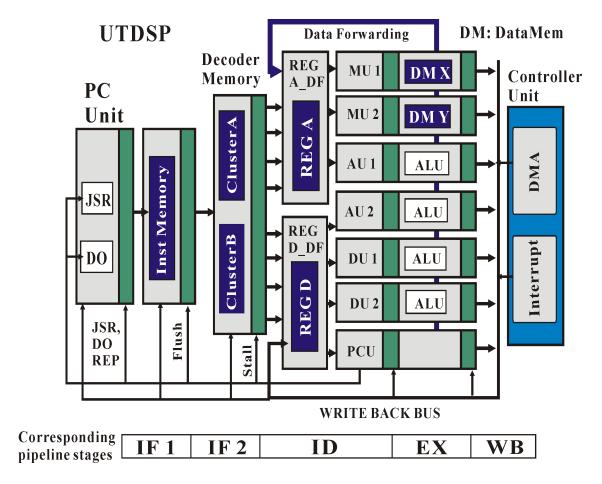

| Figure 5.1:  | The UTDSP hardware blocks                                                                | .52 |

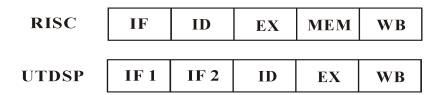

| Figure 5.2:  | The pipeline architectures of RISC and the UTDSP                                         | .54 |

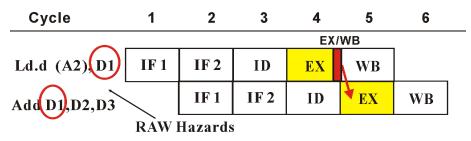

| Figure 5.3:  | RAW hazards and bypassing path                                                           | .55 |

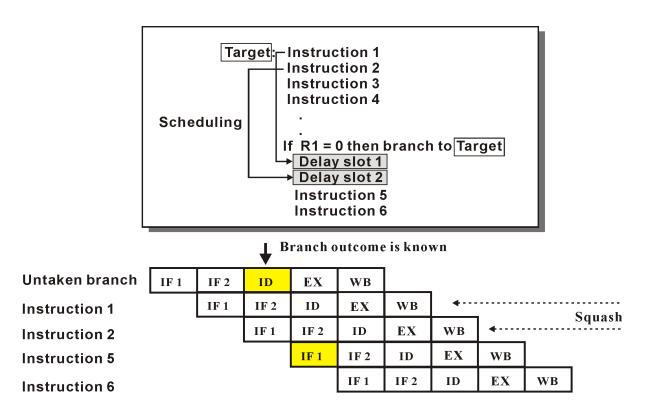

| Figure 5.4:  | The UTDSP instruction pipeline when predict-taken scheme is used                         | .56 |

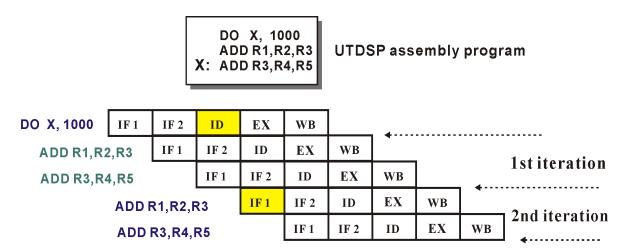

| Figure 5.5:  | The UTDSP zero-overhead hardware loop                                                    | .57 |

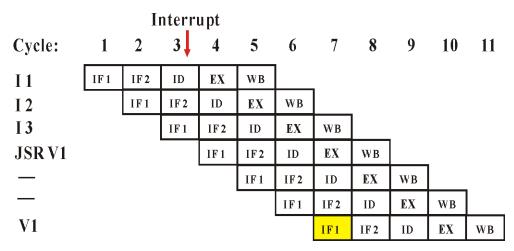

| Figure 5.6:  | The UTDSP instruction pipeline when handling an interrupt                                | .58 |

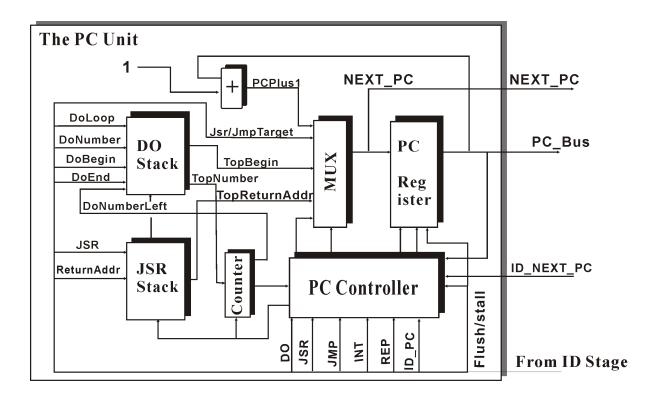

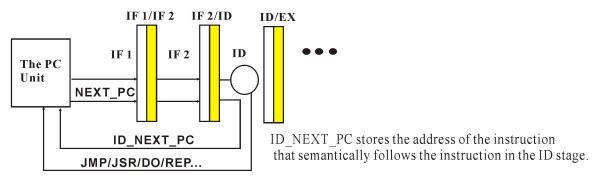

| Figure 5.7:  | The block diagram of the PC Unit                                                         | .59 |

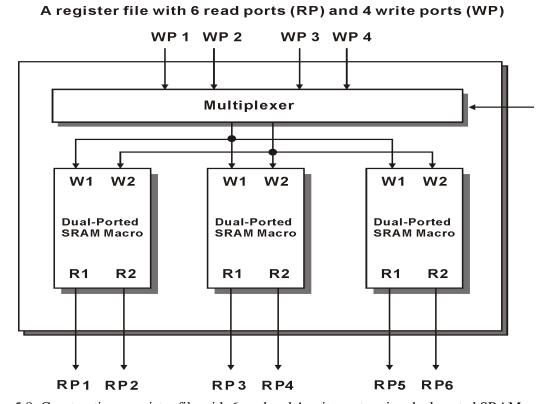

| Figure 5.8:  | Constructing a register file with 6 read and 4 write ports using dual-ported SRAM macros |     |

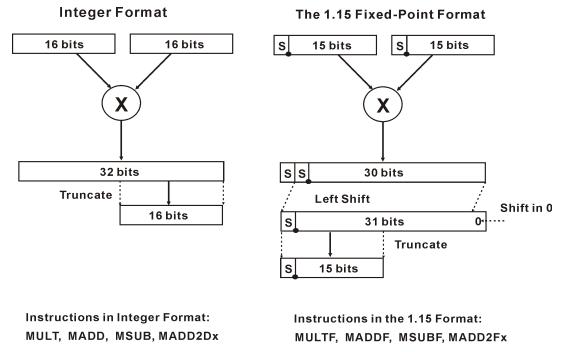

| Figure 5.9:  | The data formats that are used in the UTDSP instructions                                 | .63 |

| Figure 5.10: | The UTDSP modulo instruction format vs. the typical format                               | .64 |

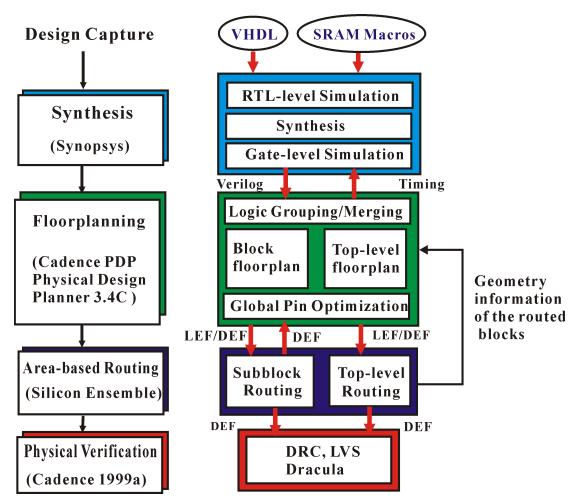

| Figure 5.11: | The UTDSP CAD methodology                                                                | .65 |

| Figure 5.12: | Before and after logic merging                                                           | .71 |

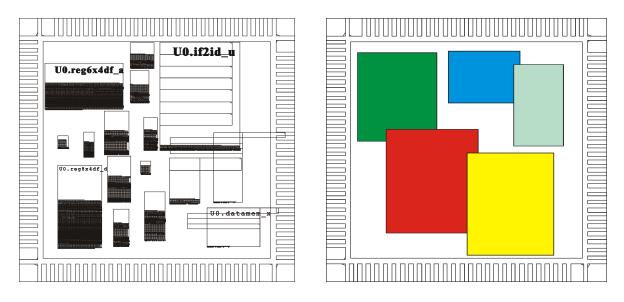

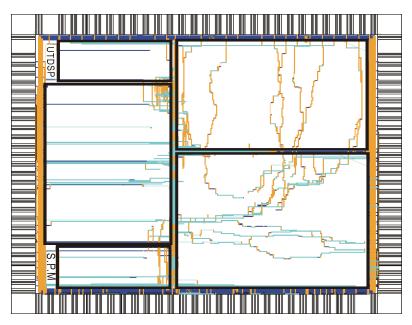

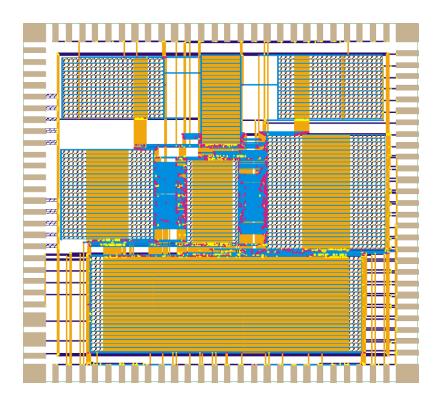

| Figure 5.13: | Group connectivity analysis and the final floorplan                                      | .71 |

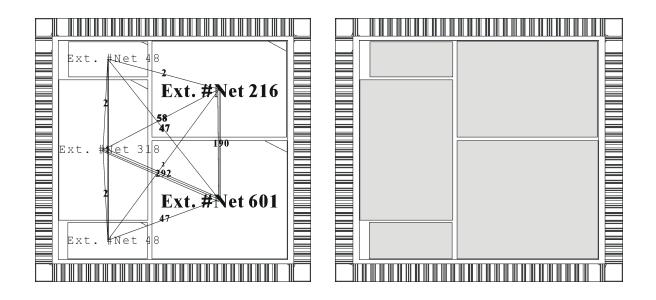

| Figure 5.14: | Block interconnect without using global-pin-optimization                                 | .72 |

|              | Block interconnect after global-pin-optimization                                         |     |

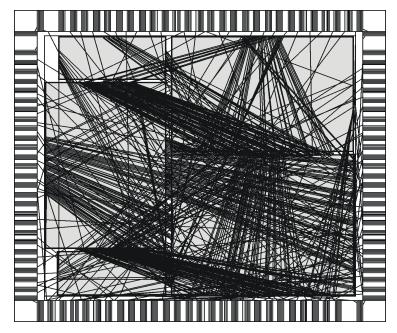

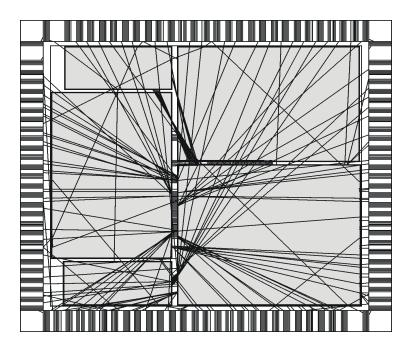

| Figure 5.16: | The final top-level routing (5.5 mm x 6.0 mm)                                            | .73 |

|              | One of the previous top-level routing with a poor floorplan (7.2 mm x 7.2 mm).           |     |

| Figure 5.18: | The UTDSP assembly code for the inner loop of FIR benchmark                              | 75  |

# **List of Tables**

| Table 2.1: | DSP kernel benchmarks                                                         | 6  |

|------------|-------------------------------------------------------------------------------|----|

| Table 2.2: | DSP application benchmarks                                                    | 7  |

| Table 3.1: | Impact of subset packing on decoder-memory requirements                       | 24 |

| Table 3.2: | Maximum addressable space of different clustering configurations              | 25 |

| Table 3.3: | Average storage requirements of the results in Figure 3.12                    | 35 |

| Table 3.4: | Trade-off between storage requirements and execution performance              | 36 |

| Table 5.1: | The value of NEXT_PC and its associated conditions                            | 60 |

| Table 5.2: | The two instructions that are removed from the original UTDSP instruction set | 62 |

| Table 5.3: | The delay of the first three critical path groups                             | 67 |

| Table 5.4: | Gate counts and areas of the components in the UTDSP                          | 67 |

| Table 5.5: | UTDSP benchmark results for compiler-generated kernel code                    | 70 |

| Table 5.6: | Comparison between UTDSP and two VLIW DSPs                                    | 74 |

| Table 5.7: | The MAC instruction for block processing                                      | 75 |

| Table A.1: | Memory Instructions                                                           | 78 |

| Table A.2: | Addressing Instructions                                                       | 78 |

| Table A.3: | Integer Instructions                                                          | 79 |

| Table A.4: | Control Instructions                                                          | 80 |

# Chapter 1

### Introduction

#### 1.1 Motivation

Digital signal processors (DSPs) are specialized microprocessors designed to execute the computationally-intensive operations commonly found in the inner loops of digital signal processing algorithms. Having been used extensively in embedded systems, DSPs are required to offer high performance while reducing cost. To fulfill this goal, traditional DSPs use tightly-encoded instruction sets to reduce instruction memory requirements, and hence cost. Using tightly-encoded instruction sets reduces not only storage requirements but also instruction memory bandwidth, which is a major concern when off-chip instruction memory needs to be used.

However, tightly-encoded instruction-set architectures (ISAs) are not well-suited for high-level languages (HLL) compilers to exploit parallelism because most of the instructions are accumulator based, limiting the number of registers that can be specified in an operation. As a result, DSP compilers generate relatively poor code compared with their counterparts for general-purpose microprocessors. Therefore, more compiler-friendly DSP architectures that combine high performance with low cost are definitely needed. One alternative to the tightly-encoded instruction architectures is the very long instruction word (VLIW) architecture.

VLIW architectures offer high performance by using multiple, independent functional units, enabling multiple instruction issue while reducing cost by eliminating dynamic scheduling logic. Unlike superscalar processors, where data hazards are handled using dynamic scheduling, VLIW architectures rely on compilers to create a package of instructions that can be simultaneously issued. VLIW architectures are very well-suited for exploiting a high level of parallelism because they are easy targets for HLL compilers to generate efficient code.

However, VLIW architectures have several limitations that are not favorable in cost-sensitive DSP processors. First, instruction-memory size is increased substantially due to the unused encoding slots in long instructions and the extra instructions created using loop unrolling to exploit parallelism. Second, fetching long instructions from off-chip instruction memory requires a high bandwidth, which can be a severe problem when pin-count and packaging options are major constraints.

#### 1.2 Objective and Contributions

The objective of this thesis is to design and implement a VLIW programmable DSP processor — UTDSP. The UTDSP eliminates the limitations mentioned above by incorporating a two-level instruction fetching and packing mechanism. The VLSI implementation of the UTDSP, along with associated software development tools, is presented in this thesis. The following details three major contributions of this thesis.

#### 1.2.1 Design and Implementation of a Long-instruction Packer

The UTDSP instruction packer was implemented based on a two-level instruction fetching mechanism proposed by Mazen Saghir [2]. The UTDSP packer not only packs long instructions to reduce storage requirements but also serves as an assembler. Benchmark results indicate that the UTDSP instruction packer outperforms the new TI VelociTI packing algorithm, while solving the fetching bandwidth problems mentioned previously.

#### 1.2.2 Design and Implementation of Architecture Simulator and GUI-based Assembly Debugger

The UTDSP architecture was designed using an application-driven design methodology where architectures are designed according to the performance and cost requirements of their target applications. Being written in a high-level language, the architecture simulator, which also serves as a behavioural model of the UTDSP, can be easily modified to experiment with design trade-offs, enabling the application-driven design methodology. An GUI-based assembly debugger was also implemented to allow programmers to perform interactive debugging features such as memory probing and breakpoint tracing.

#### 1.2.3 Design and VLSI Implementation of the UTDSP

The UTDSP, which has five pipeline stages, was implemented using a synthesis-based design methodology. The UTDSP provides not only a set of highly orthogonal, RISC-like instructions but also DSP-specific features such as zero-overhead hardware loops. The zero-overhead hardware loops can be nested up to five levels. Also, interrupts and branches are allowed in the inner loop. A novel hierarchical CAD flow that significantly reduces the resulting area and interconnect delay of the UTDSP was defined in this thesis.

#### 1.3 Thesis Organization

This thesis is divided into six chapters. Chapter 2 provides the reader with background information on the UTDSP, focusing on a VLIW model architecture and its compiler system. Chapter 3 introduces the design and implementation of the UTDSP packer. Benchmark comparison between the UTDSP packer and TI's VelociTI memory packer will be analyzed in this chapter. Chapter 4 describes the design and implementation of the architecture simulator and GUI-based assembly debugger. Chapter 5 presents the design and VLSI implementation of the UTDSP. Related CAD issues will be illustrated in this chapter. Chapter 6 concludes this thesis and offers recommendations for future work.

# Chapter 2

# **Background**

The rapid growth in the consumer electronics market has increased the demand for high-performance, low-cost processors for use in embedded systems. Although off-the-shelf DSP processors can be used to meet these demands, application-specific programmable processors (ASPPs) — processors that are designed for specific applications — are more desirable for use in cost-sensitive systems because their architectures and instruction set can be tuned for their specific performance and cost requirements. The UTDSP processor, an ASPP aimed at embedded DSP applications, incorporates an application-driven design methodology, where architectures are designed according to the requirements of the target applications.

This chapter provides an overview to the UTDSP project and describes background information upon which this thesis is built. Section 2.1 explains the application-driven design methodology and how it is used to generate architectures that are easy targets for high-level language (HLL) compilers. Section 2.2 introduces a flexible model architecture that can be easily modified according to the performance and cost requirements of the target applications. Section 2.3 describes an optimizing C compiler and its role in tuning the model architecture. Section 2.4 describes two commercially available DSP processors that have VLIW architectures. Section 2.5 summarizes this chapter.

### 2.1 Application-Driven Design Methodology

Conventional embedded DSP processors are designed without fully appreciating the features and limitations of their HLL compilers. Moreover, many DSP processors are developed using a methodology where compiler construction starts after functional silicon is obtained [3][4][5]. This usually results in a design that is a difficult target for HLL compilers; therefore, the compilers nei-

ther take maximum advantage of the hardware resources in the architecture nor generate efficient assembly code compared with hand-crafted versions.

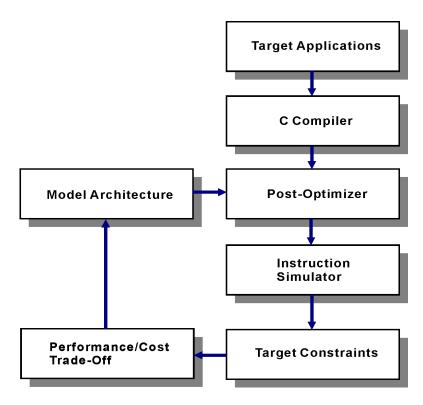

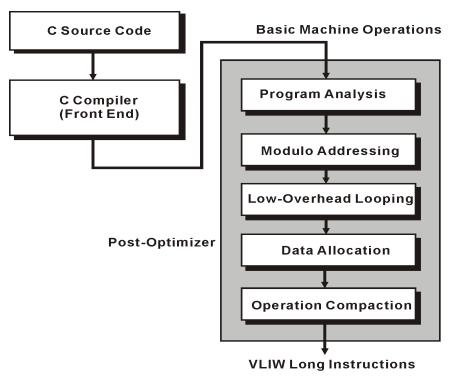

Figure 2.1: Application-driven design methodology

In contrast, the UTDSP project uses an application-driven design methodology [1] where architectures are designed according to the performance and cost requirements of their target applications. Figure 2.1 shows the flow used in the application-driven design methodology. The design starts with a flexible model architecture as a template; a suite of benchmarks is used to evaluate the performance of the model architecture. The model architecture is iteratively modified until it meets the performance and cost requirements of the target applications. The key component in this design methodology is the flexible model architecture, which is easy to configure and is able to exploit parallelism. A flexible, RISC-like instruction set is also provided to make the model architecture an easy target for HLL compilers.

As the complexity of DSP applications increases, writing a DSP application entirely in assembly language is no longer feasible although kernels and inner loop code are still often hand-optimized to achieve a better throughput. Therefore, the benchmark suite was developed in the C

programming language and a C compiler is used to translate the target applications into the machine operations that can be executed by the model architecture. The C compiler generates sequential code and performs register allocation based on the instruction set and the number of registers defined for the model architecture. A post-optimizer is then used to exploit the DSP-specific features of the model architecture. The post-optimizer also exploits parallelism in the sequential code and creates executable code that runs on the model architecture. The executable code is then simulated using an instruction-set simulator to obtain the cost and performance information of the model architecture.

When the performance requirements are not fulfilled, the architecture, compiler, and post-optimizer can be modified to exploit more parallelism. Similarly, when the cost requirements are not fulfilled, the hardware components that are under-utilized can be removed to reduce system cost. This process is repeated until the model architecture meets both the cost and the performance requirements of the target applications.

The benchmark suite used in this study consists of six kernels and ten applications. Table 2.1 shows the kernel benchmarks, which consists of simple algorithms commonly used in DSP applications. The kernels usually constitute the inner loop of DSP applications; therefore the effectiveness of exploiting parallelism in kernels dominates the overall performance. In other words, the compiler must generate efficient code for kernels to maximize the utilization of the hardware resources in the model architecture. Table 2.2 shows the DSP application benchmarks, which are commonly used in embedded systems. Using the suite of benchmarks with the application-driven design methodology thus makes the resulting model architecture an ideal design for embedded DSP processors.

|          | Kernels                | Description                                                  |

|----------|------------------------|--------------------------------------------------------------|

| k1<br>k2 | fft_1024<br>fft_256    | Radix-2, in-place, decimation-in-time fast Fourier transform |

| k3<br>k4 | fir_256_64<br>fir_32_1 | Finite impulse response (FIR) filter                         |

| k5<br>k6 | iir_4_64<br>iir_1_1    | Infinite impulse response (IIR) filter                       |

Table 2.1: DSP kernel benchmarks

|            | Kernels                    | Description                                  |  |

|------------|----------------------------|----------------------------------------------|--|

| k7<br>k8   | latnrm_32_64<br>latnrm_8_1 | Normalized lattice filter                    |  |

| k9<br>k10  | lmsfir_32_64<br>lmsfir_8_1 | Least-mean-squared (LMS) adaptive FIR filter |  |

| k11<br>k12 | mult_10_10<br>mult_4_4     | Matrix Multiplication                        |  |

Table 2.1: DSP kernel benchmarks

|          | Applications     | Description                                                 |  |

|----------|------------------|-------------------------------------------------------------|--|

| a1<br>a2 | G721_A<br>G721_B | Two implementations of the ITU G.721 ADPCM speech encoder   |  |

| a3       | V32.modem        | V.32 modem encoder/decoder                                  |  |

| a4       | adpcm            | Adaptive differential pulse-coded modulation speech encoder |  |

| a5       | compress         | Image compression using discrete cosine transform (DCT)     |  |

| a6       | edge_detect      | Edge detection using 2D convolution and Sobel operators     |  |

| a7       | histogram        | Image enhancement using histogram equalization              |  |

| a8       | lpc              | Linear predictive coding speech encoder                     |  |

| a9       | spectral         | Spectral analysis using periodogram averaging               |  |

| a10      | trellis          | Trellis decoder                                             |  |

Table 2.2: DSP application benchmarks

#### 2.2 The Model Architecture

Flexibility and compiler programmability are two important requirements for the model architecture used in the application-driven design methodology. Flexibility enables the model architecture to be easily configured to meet the performance and cost constraints of an application, while compiler programmability requires the architecture to be an easy target for HLL compilers. A model architecture that is based on a very long instruction word (VLIW) architecture was chosen to meet both requirements [2].

A VLIW architecture consists of multiple functional units each of which can execute independent instructions simultaneously. Unlike CISC instructions, which are vertically encoded, VLIW

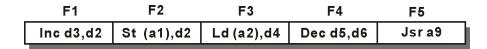

Figure 2.2: Example long instruction for a VLIW with 5 functional units

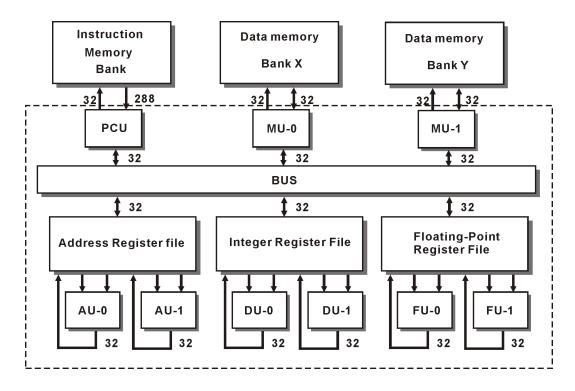

Figure 2.3: VLIW Model Architecture

long instructions are horizontally encoded. Each long instruction contains N fields, where N is the number of operations that can be executed concurrently; each field controls a corresponding functional unit. Figure 2.2 shows an example VLIW long instruction. An optimizing compiler is used to exploit parallelism and schedule parallel operations into the fields of a long instruction. Moreover, using a highly orthogonal, RISC-like instruction set helps the compiler generate efficient code for the target architecture. The VLIW architecture is flexible in that additional functional units can be easily added when required for performance with little impact on the compiler.

Figure 2.3 shows the VLIW model architecture used for the UTDSP. The model contains nine functional units: two memory units (MU0 and MU1), two address units (AU0 and AU1), two integer units (DU0 and DU1), two floating-point units (FU0 and FU1), and one control unit

(PCU). MU0 and MU1 execute memory operations. Each memory unit connects to a single-ported, data-memory bank. AU0 and AU1 execute address operations. DU0 and DU1 execute integer operations. FU0 and FU1 execute floating-point operations. PCU executes control operations. Because the model has nine functional units, up to nine parallel operations can be specified in a long instruction and execute concurrently. Unlike superscalar architectures, where instruction scheduling is handled dynamically in hardware, VLIWs adopt static scheduling, which requires compilers to resolve data hazards. Eliminating the dynamic scheduling logic gives VLIWs a faster execution speed and a smaller silicon area. Because the long instructions consisting of RISC-like operations can still fit in a pipeline scheme, VLIWs can exploit not only spatial parallelism using multiple functional units, but also temporal parallelism by introducing the pipeline scheme.

A Harvard memory architecture, where instruction memory is separated from data memory, is used to increase memory bandwidth and enable the concurrent fetching of instructions and data. Because the model architecture is a load-store design — all operands must be first loaded from data memory to register files through the two MUs, dual data-memory banks are introduced to reduce the possibility of starving for operands in DSP kernels. To take advantage of the dual data-memory banks, the compiler must distribute program data among them. More details about exploiting dual data-memory banks are given in [2][42].

The model has three register files to store address, integer, and floating-point operands, respectively. Specifically, the integer functional units only operate on registers in the integer register file; the address units only operate on registers in the address register file. Similarly, the floating-point units can only access the registers in the floating-point register file. All register files are connected to the memory units so that data can be loaded from data-memory banks to any one of the register files. The program-control unit is also connected to all register files to allow data transfers between them.

However, one major drawback that prevents VLIWs from being used in cost-sensitive systems is their high instruction bandwidth. As shown in Figure 2.3, the model architecture needs a 288-bit bus for instruction fetching. Because a long instruction must be fetched from memory on every clock cycle, the performance will be severely degraded when off-chip instruction memory is used and the number of available pins is not enough for implementing a full fetch bus. Another drawback is the large instruction storage when compilers cannot exploit enough parallelism to sched-

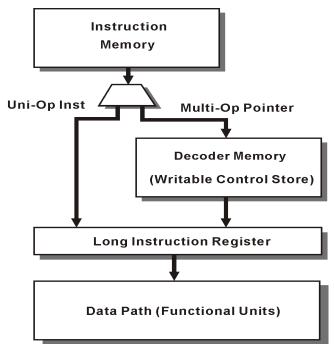

Figure 2.4: Basic Structure of Instruction Decoder

ule operations into long instructions. Storing the long instructions that have many unused fields in their original format is therefore very wasteful, and results in increased system costs.

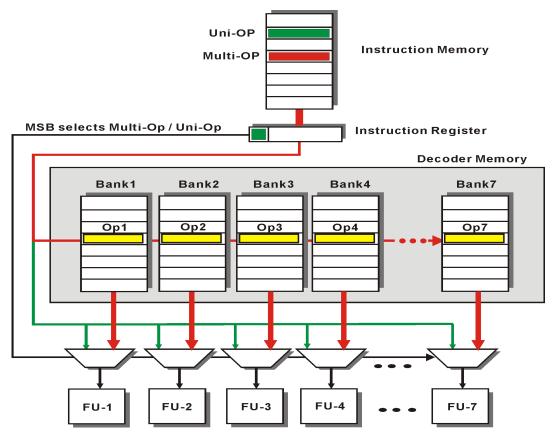

To solve the bandwidth and storage problems mentioned above, Mazen Saghir proposed a long instruction fetching and packing mechanism [2] based on writable control stores [6][7]. The writable control stores can be found in a microprogrammed computer where an instruction contains a pointer to horizontal microcode stored in the control store. Similarly, long instructions can be stored in the control store and their pointers are stored in the instruction memory. When a pointer is fetched from the instruction memory, it is used to fetch its associated long instruction from the control store (decoder memory). Figure 2.4 shows a block diagram of the instruction and decoder memory. The instruction memory stores single operations or pointers to long instructions. The operations stored in the instruction memory are called *uni-op* instructions — long instructions that contain only one operation. In contrast, the pointers stored in the instruction memory are called *multi-op* pointers, which point to the actual long instructions stored in the decoder memory. The instruction fetching and packing mechanism used in the UTDSP processor was implemented

based on this two-level fetching model. More details will be given in Chapter 3 where the design and implementation of the UTDSP Packer is explained.

### 2.3 C Compiler and Post-Optimizer

A C compiler translates a program written in C into a functionally equivalent program taking the form of the machine language of the target architecture; it uses machine-independent optimizations to increase the run-time performance of the resulting machine code. These optimizations usually include loop unrolling, common sub-expression elimination, strength reduction, and constant propagation [8]. Furthermore, the compiler can perform specific machine-dependent optimizations to take maximum advantage of the hardware resources in the target architecture. For instance, the machine-dependent optimizations include instruction scheduling, software pipelining, register renaming, data prefetching, and branch prediction when the target architecture is a general-purpose RISC processor.

Originally, the C compiler for the model architecture was based on the GNU C compiler (Gcc) because it is public-domain software; it uses a good suite of scalar optimizations; and it is easy to retarget to different architectures. However, the intermediate form Gcc uses provides too little information about the source program to implement machine-dependent optimizations. To implement DSP-specific optimizations without modifying Gcc, a post-optimizing pass was developed to perform the machine-dependent optimizations for the model architecture. Figure 2.5 shows the resulting two-phase compilation process. In the first phase, the C compiler translates C programs into sequential assembly language operations that can be executed on the model architecture. In the second phase, the post-optimizer back-end performs the architecture-specific optimization. The initial work on Gcc and the post-optimizer was done by Vijaya Singh [9]. The post-optimizer was later augmented by Mazen Saghir [2][43] and Mark Stoodley [10]. The Gcc front-end was later again replaced by the SUIF compiler [11] to enable the use of a more natural coding style for applications. The SUIF compiler was ported to the model architecture by Sanjay Pujare [12].

The post-optimizer optimizes the execution performance of a program by taking maximum advantage of the underlying hardware resources in the model architecture; it applies five optimi-

Figure 2.5: Two-phase compilation: C Compiler and Post-Optimizer

zation passes to the sequential machine operations generated by the front-end C compiler and creates long instructions that can execute on the model architecture. The five passes include the program analysis pass, the modulo addressing pass, the low-overhead looping pass, the data allocation pass, and the operation compaction pass, as shown in Figure 2.5.

First, the program analysis pass constructs a control-flow graph for the code generated by the front-end compiler. It then extracts information about its data-flow, control-flow, and aliasing characteristics, which are needed in the other phases. Second, the modulo addressing pass converts all arrays in the original code to circular buffers so that the elements in the arrays are accessed in a modulo manner. Third, the low-overhead looping pass tries to replace conditional branch instructions in a loop with a single low-overhead looping operation that specifies the iteration count and the addresses of the first and last instruction in the loop body. Fourth, the data allocation pass takes advantage of the dual data-memory banks of the model architecture and exploits parallelism by distributing program data among the banks. Finally, the operation compaction pass packs machine operations into long instructions using a list scheduling algorithm [13].

#### 2.4 TI VelociTI and Philips R.E.A.L DSP Architectures

This section describes VLIW architectures that are used in two commercially available DSP processors — TI TMS320C62xx and Philips R.E.A.L DSP.

#### 2.4.1 TI VelociTI Architecture

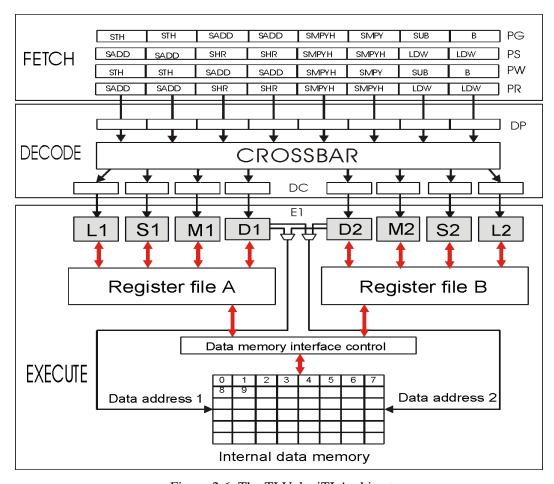

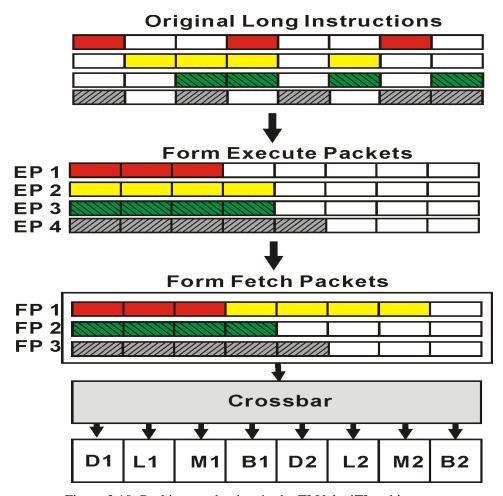

The VelociTI architecture is used in the TMS320C62xx, which is the latest in the TMS320 family of DSPs. The VelociTI architecture is an advanced VLIW design that has a long-instruction packing scheme to reduce storage requirements. The VelociTI uses a deep pipeline to eliminate traditional pipeline bottlenecks including memory access and multiply-accumulate operations. Figure 2.6 shows the block diagram of the VelociTI architecture.

Figure 2.6: The TI VelociTI Architecture

There are eight functional units in the VelociTI architecture. They are divided into two data paths. Each data path has four functional units and a register file. The data in the two register files can be exchanged via a crosspath. Each functional unit can execute only a subset of the VelociTI instruction set. The VelociTI has a highly orthogonal, RISC-like instruction set and a load-store architecture — memory accesses are performed using explicit load or store instructions.

As shown in Figure 2.6, the VelociTI has three pipeline phases: Fetch, Decode, and Execute. The Fetch phase consists of four pipeline stages. In the Fetch phase, a program address is generated and used to fetch a long instruction (Fetch Packet) from instruction memory. In the Decode phase, which consists of two pipeline stages, the operations in the fetched long instruction are dispatched to their corresponding functional units via a crossbar. The crossbar is used because the VelociTI has a long-instruction packing scheme to reduce storage requirements. The details of this packing scheme will be discussed in Section 3.4.1.

In the Execute phase, the dispatched operations are executed in their corresponding functional units. The Execute phase is divided into 5 pipeline stages because each instruction uses different number of pipeline stages. Most of the instructions use one pipeline stage, whereas some instructions such as branch require 5 pipeline stages to execute. More details can be found in [14][26].

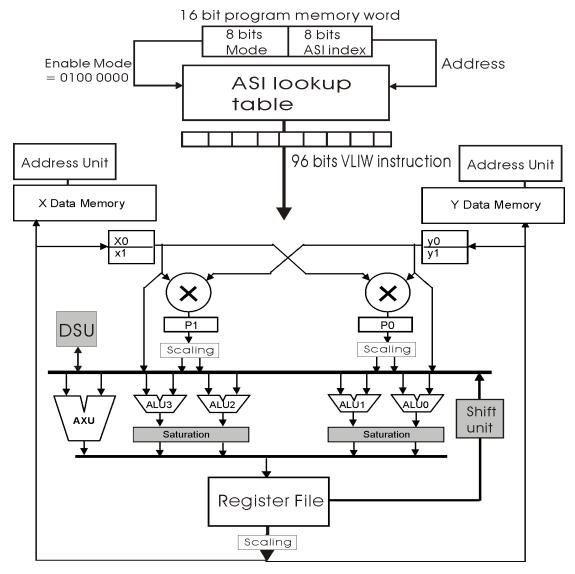

#### 2.4.2 Philips R.E.A.L. DSP Architecture

The R.E.A.L. DSP (Reconfigurable Embedded DSP Architecture at Low-power and Low-cost) is designed as a flexible embedded core to enable an application-specific tuning and fast turn-around time. The R.E.A.L. DSP is a VLIW design with a dual Harvard architecture and 3 pipeline stages. The R.E.A.L. uses a look-up table to store its VLIW instructions. Figure 2.7 shows the block diagram of the R.E.A.L. DSP core.

When a 16-bit word is fetched from program memory and if its first 8 bits equal to the specified enabling mode, the lower byte of the word will be used as an address to fetch its corresponding long instruction stored in the ASI look-up table. The VLIW instructions stored in the ASI look-up table are 96-bit long and can specify many operations to control not only functional units but also application specific execution units (AXU). The AXUs are designed to execute a special set of instructions that are tuned for target applications. Most importantly, they can be placed anywhere in the datapath or the address functional units.

The ASI look-up table can contain only 256 long instructions and it does not use any instruction packing scheme. Although it stores the duplicates of a long instruction in the same table entry to reduce its storage requirement, we believe that the storage requirement is unlikely to be reduced because the possibility of having exactly the same long instructions is rare. More details can be found in [3][45].

Figure 2.7: The Philips R.E.A.L DSP architecture

#### 2.5 Summary

This chapter introduced the compiler system and the model architecture developed for an application-driven design methodology. In the application-driven design framework, the compiler-generated code for a set of target applications is used to measure the performance of the flexible model architecture. The measurements are compared with the application-specific constraints and the model architecture is iteratively modified until all the constraints are met.

The model architecture is based on a VLIW model because it is very flexible and can easily be configured to meet the target constraints. Although the long-instruction scheme in VLIWs is an easy target for HLL compilers, its high bandwidth and storage requirements prevent VLIWs from being used in cost-sensitive embedded systems. A long-instruction packing and fetching scheme that is based on a control-store mechanism was proposed by Mazen Saghir to overcome these problems [2].

Compiling an application into the long-instruction format involves a two-phase process. The first phase is to translate the source code into basic machine operations using the GNU C compiler; the second phase performs architecture-specific optimizations using a post-optimizer and generates long instructions that can run on the model architecture.

Having covered the work done by previous researchers and two commercially available DSP architectures in this chapter, the following chapters will focus on the design and VLSI implementation of the UTDSP processor and associate development tools. The UTDSP processor is based on the model architecture and incorporates the long-instruction encoding mechanism to solve the instruction bandwidth and storage problems.

# Chapter 3

# **Long-Instruction Packing and Fetching for the UTDSP**

In the last chapter, the model architecture and the optimizing compiler systems were discussed. Although the optimizing compiler could exploit enough parallelism and generate efficient code with the flexible model architecture, the storage requirements of long instructions and the high instruction bandwidth required represent major obstacles in developing a feasible system. This chapter describes the UTDSP instruction fetching and packing mechanism, which solves the problems mentioned above.

The UTDSP instruction fetching and packing mechanism was designed based on the two-level instruction fetching scheme discussed in the last chapter. Section 3.1 describes the basic architecture of this mechanism and a simple packing algorithm that reduces the instruction storage requirements. Section 3.2 presents a two-cluster packing algorithm that achieves a denser packing result by dividing a long instruction into two sub-words and sharing memory locations.

Section 3.3 describes the software implementation of the UTDSP packer using the two-cluster packing algorithm. It also shows that data structures constructed using template techniques not only ease the implementation of the UTDSP packer and assembly tools, but also shorten the design time used to explore various packing algorithms. Section 3.4 examines the impact of the packing algorithms on the storage requirements and compares the benchmark results of the UTDSP packer with that of Texas Instruments' VelociTI packing [14]. Section 3.5 summarizes this chapter.

### 3.1 Storing and Decoding Long Instructions

Fig 3.1 shows the two-level instruction memory system used in the UTDSP to store the long-instructions. This architecture was proposed by Mazen Saghir [2]. The instruction memory sys-

Figure 3.1: Block diagram of the UTDSP memory system

that contain only one operation — uni-op operations — are stored in the instruction memory, while the other long instructions are stored in the decoder memory and their addresses — multi-op pointers — are stored in the instruction memory instead. The decoder memory contains seven banks, each of which is associated with a functional unit; therefore, the operations stored in a decoder-memory bank will be executed in its associated functional unit. Although the seven operations in a long-instruction word are distributed in the different banks of the decoder memory, they are stored in the memory locations that have the same physical address so that they can be fetched using their corresponding multi-op pointer stored in the instruction memory.

When a word is fetched from the instruction memory, its most-significant bit is examined to determine if the word is a uni-op operation or a multi-op pointer. If it is a uni-op operation, it is directly issued to an appropriate functional unit where it can be executed. In contrast, if a multi-op pointer is fetched, it is used to access the memory locations in the decoder-memory banks and the

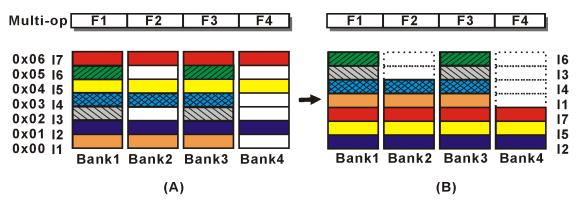

Figure 3.2: (A) Multi-op instructions stored in an arbitrary manner (B) Multi-op instructions stored according to field priorities

seven operations stored in the locations addressed by the multi-op pointer will be dispatched to their corresponding functional units.

#### 3.1.1 Reducing the Size of Decoder Memory

Storing long-instructions in their original formats illustrated in Figure 3.1 can be very wasteful because of NOPs — the no operation fields in the long instructions. One way to reduce the overall size of the decoder memory is to store instructions in a way that allows some of the memory for NOPs to be omitted. Let the priority of a field in a multi-op instruction be the number of NOPs stored in the decoder-memory bank associated with the field. Multi-op instructions with operations in the higher-priority fields are stored first, starting from address zero, while instructions with operations in the lower-priority fields are stored last. Figure 3.2 shows the impact of storing instructions according to field priorities on the decoder memory.

In Figure 3.2 (A) multi-op instructions are stored in an arbitrary manner. Observe that bank4 suffers the most from the poor ordering of the multi-op instructions because bank4 contains the most NOPs (white boxes). Therefore, field F4, associated with bank4, is assigned the highest priority and the multi-op instructions that have operations in field F4 are stored first. Figure 3.2 (B) shows that multi-op instructions are stored according to field priorities. In this case the storage requirement for bank4 can be reduced to three words by chopping off the four consecutive empty words.

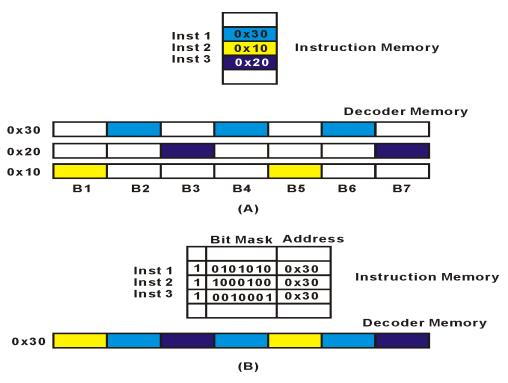

Moreover, the decoder-memory size can be further reduced by storing multi-op instructions with mutually exclusive operation fields into the same long-instruction word. Figure 3.3 (A)

Figure 3.3: (A) Storing multi-op instructions in their original format (B) Storing multi-op instructions in a packed format

shows that three multi-op instructions are stored as three, separate, long-instruction words. When stored in this format, the instructions occupy 21 words, of which 14, or approximately 67% are NOPs. In contrast, Figure 3.3 (B) shows that the three instructions are packed into a single long-instruction word because their operations use mutually exclusive fields. In this case, storing the long instructions needs only seven memory words. Therefore, packing multi-op instructions with mutually exclusive fields into a single long instruction reduces the size of the decoder memory significantly.

To fetch the original operations of a multi-op instruction from the packed long-instruction word, the multi-op pointer should store not only the address of the packed word, but also a bit mask that selects specific memory banks in the decoder memory. Figure 3.3 (B) shows the bit mask fields in the multi-op pointers stored in the instruction memory. Note that the number of bits in the bit mask is the same as the number of memory banks; each bit in the mask is used to select its corre-

Figure 3.4: Field clustering packing method

sponding memory bank. The decoder-memory banks that are not selected by the bit mask will return NOPs.

### 3.2 Achieving Denser Instruction Packing

The major drawback of the packing method described in Section 3.1 is that two instructions cannot be packed into a single decoder-memory word even if they share only one field. This section describes two methods that can be used to achieve a denser instruction packing result. The final implementation of the UTDSP packer incorporates these two methods.

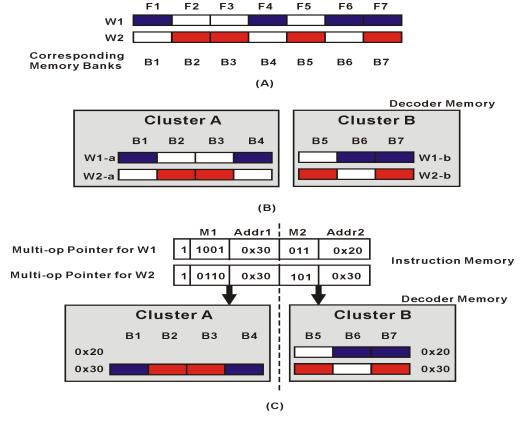

#### 3.2.1 Field Clustering Method

Figure 3.4 (a) illustrates the problem where two instructions cannot be packed into a single word because both instructions use field F7. Mazen Saghir proposed a field clustering method to solve this problem [2]. Observe that the remaining fields in both instructions are mutually exclu-

sive, and that they could have been packed into the same memory word if field F7 was ignored. This suggests that dividing the memory banks into clusters can achieve a denser packing result. Figure 3.4 (B) shows that the memory banks are grouped into two clusters: cluster A consisting of memory banks B1 to B4, and cluster B consisting of banks B5 to B7.

As a result, in this example, multi-op instruction word W1 is divided into subwords W1-a and W1-b; W2 is divided into subwords W2-a and W2-b. The packing method is then applied to each cluster separately. Applying the packing method to cluster A will pack W1-a and W1-b into one subword in the decoder memory because the operations in W1-a and W1-b use mutually exclusive fields. The subwords W2-a and W2-b remain the same because both instructions use field F7. The Figure 3.4 (c) shows the final packing result using this two-cluster grouping method. Note that another set of bit masks and address fields must be added into the multi-op pointers to extract operations from the two different clusters. Figure 3.4 (c) also shows the contents of the multi-op pointers, which are used to extract the original multi-op instructions W1 and W2 from the two clusters.

#### 3.2.2 Sharing Packing Slots

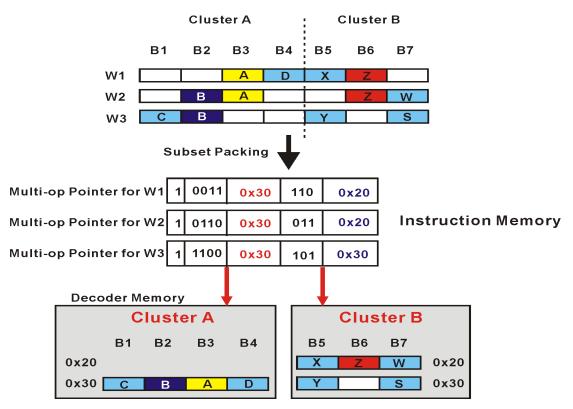

Clustering enables the exploitation of redundancy at the sub-instruction level, meaning that only one copy of the identical sub-instructions need to be stored in the decoder memory; however, the ideal packing result is still not achievable unless a seven-cluster configuration is used [2]. A further improvement to clustering can be achieved by making the following observation:

#### • Observation:

With the help of the bit mask fields in multi-op pointers, two instructions can be packed into the same decoder-memory word as long as one instruction is a *subset* of the other one.

• The **definition** of *subset* in a long instruction is described as follows:

A long instruction X is said to be a <u>subset</u> of the long instruction Y if and only if every operation in X can be found in the corresponding field in Y, or the corresponding field in Y is empty.

Figure 3.5: Combining the two-cluster packing and slot-sharing methods

Using the two-cluster packing method described in Section 3.2.1 increases the possibility of finding subset instructions to share the same decoder-memory word. Figure 3.5 shows that a denser packing result can be achieved by combining this subset sharing method with the two-cluster packing. In this example, the three subwords of long instructions W1, W2, and W3 in Cluster A can be packed into one subword in the decoder memory. The advantage of using the subset packing is that this mechanism needs no extra hardware.

Table 3.1 shows the impact of using the subset packing method on the decoder-memory requirements of the kernel and application benchmarks described in Chapter 2. The average decoder-memory requirements in the table are normalized to the ideal packing case, where ideal means that there are no NOPs in the decoder memory. Using the subset packing method reduces the decoder-memory requirements of the two-cluster packing by 10.16% and 10.25% on average in the kernel and application benchmarks respectively, achieving a packing result that is better than

the ideal packing case. It is even possible that with more clever register allocation, this result could be further improved.

| Kernel<br>Benchmarks | Decoder-memory<br>Requirement<br>(Ideal Packing<br>Case) | Decoder-memory<br>Requirement<br>(Two-cluster Pack-<br>ing) | Decoder-memory<br>Requirement<br>(Two-cluster &<br>Subset Packing) | Saving on<br>Decoder-memory<br>using Subset<br>Packing |

|----------------------|----------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------|

| FFT_1024             | 1                                                        | 1.10                                                        | 1.10                                                               | 0%                                                     |

| FFT_256              | 1                                                        | 1.10                                                        | 1.10                                                               | 0%                                                     |

| FIR_256_64           | 1                                                        | 1.16                                                        | 1.16                                                               | 0%                                                     |

| FIR_32_1             | 1                                                        | 1.13                                                        | 0.87                                                               | 23.53%                                                 |

| IIR_4_64             | 1                                                        | 1.11                                                        | 1.08                                                               | 2.5%                                                   |

| IIR_1_1              | 1                                                        | 1.13                                                        | 1.13                                                               | 0%                                                     |

| latnrm_32_64         | 1                                                        | 1.25                                                        | 1.13                                                               | 10%                                                    |

| latnrm_8_1           | 1                                                        | 1.12                                                        | 1                                                                  | 10.53%                                                 |

| lmsfir_32_64         | 1                                                        | 1.10                                                        | 0.86                                                               | 21.74%                                                 |

| lmsfir_8_1           | 1                                                        | 1.08                                                        | 0.8                                                                | 25.58%                                                 |

| mult_10_10           | 1                                                        | 1.13                                                        | 1.04                                                               | 7.41%                                                  |

| mult_4_4             | 1                                                        | 1.13                                                        | 1.04                                                               | 7.41%                                                  |

| all_kernels          | 1                                                        | 1.16                                                        | 0.89                                                               | 23.33%                                                 |

| Average              | 1                                                        | 1.13                                                        | 1.02                                                               | 10.16%                                                 |

| Application<br>Benchmarks | Decoder-memory<br>Requirement<br>(Ideal Packing<br>Case) | Decoder-memory<br>Requirement<br>(Two-cluster Pack-<br>ing) | Decoder-memory<br>Requirement<br>(Two-cluster &<br>Subset Packing) | Saving on<br>Decoder-memory<br>using Subset<br>Packing |

|---------------------------|----------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------|

| G721a                     | 1                                                        | 1.08                                                        | 0.95                                                               | 11.85%                                                 |

| G721b                     | 1                                                        | 1.13                                                        | 1.07                                                               | 5.77%                                                  |

| V32.modem                 | 1                                                        | 1.08                                                        | 0.89                                                               | 17.80%                                                 |

| adpcm                     | 1                                                        | 1.12                                                        | 1.09                                                               | 2.44%                                                  |

| compress                  | 1                                                        | 1.08                                                        | 0.98                                                               | 8.80%                                                  |

| edge_detect               | 1                                                        | 1.12                                                        | 0.95                                                               | 14.86%                                                 |

| histogram                 | 1                                                        | 1.06                                                        | 0.96                                                               | 9.30%                                                  |

| lpc                       | 1                                                        | 1.10                                                        | 1.05                                                               | 4.88%                                                  |

| spectral                  | 1                                                        | 1.07                                                        | 1                                                                  | 6.95%                                                  |

| trellis                   | 1                                                        | 1.06                                                        | 0.92                                                               | 12.63%                                                 |

| all_applications          | 1                                                        | 1.08                                                        | 0.89                                                               | 17.43%                                                 |

| Average                   | 1                                                        | 1.09                                                        | 0.98                                                               | 10.25%                                                 |

Table 3.1: Impact of subset packing on decoder-memory requirements

#### 3.2.3 Choosing the Number of Clusters in the UTDSP

In theory, there can be as many clusters as there are decoder-memory banks to achieve a denser packing result. In practice, however, the number of clusters that can be used is limited by the bandwidth of the instruction memory. Because one of the major reasons for using this two-level memory hierarchy is to reduce the off-chip instruction memory bandwidth, design decisions must be made based on a fixed instruction memory bandwidth.

The UTDSP model uses a 32-bit instruction word; therefore, the multi-op pointers should also be 32-bits long, so that both uni-op instructions and multi-op pointers can be stored in the instruction memory without wasting any bits. The bit mask fields in the multi-op pointer need seven bits in total to control the seven memory banks in the decoder memory. Also, the most-significant bit is used to identify itself as a uni-op or a multi-op pointer. As a result, 24 bits are left for encoding one or more address fields in a multi-op pointer.

Choosing the number of clusters to use in the decoder memory is a trade-off between the reduced cost achieved by a denser packing result, and the degraded performance resulting from a smaller size of decoder memory. Table 3.2 shows the maximum addressable decoder-memory space of different clustering configurations. On the basis of the data shown in the table, the two-cluster configuration was chosen for the UTDSP processor because the two-cluster case has a denser packing result than the ideal one (Table 3.1), while providing a much larger addressable space than the three-cluster configuration. For the three-cluster configuration, the total addressable decoder-memory space is only 2.2 K words, which is too small for most of the DSP applications.

| Number of<br>Clusters | Total<br>address<br>bits | Number of<br>bits in a<br>cluster address<br>pointer | Addressable<br>Memory space<br>in each bank | Total addressable<br>decoder memory<br>space |

|-----------------------|--------------------------|------------------------------------------------------|---------------------------------------------|----------------------------------------------|

| 1                     | 24                       | 24                                                   | 16 M words                                  | 112 M words                                  |

| 2                     | 24                       | 12                                                   | 4 K words                                   | 28 K words                                   |

| 3                     | 24                       | 8                                                    | 256 words                                   | 2.2k words                                   |

| 4                     | 24                       | 6                                                    | 64 words                                    | 448 words                                    |

Table 3.2: Maximum addressable space of different clustering configurations

To reduce the possibility of having NOPs in subwords, decoder-memory banks B1 to B4 were grouped into Cluster A and banks B5 to B7 were grouped into Cluster B. This configuration was chosen because the UTDSP compiler often schedules two memory load/store operations (associated with banks B1 and B2) and two address pointer operations (associated with banks B3 and B4) into one long instruction. Although further optimization might be achieved by using different grouping configurations, it was not attempted because using the subset packing method has already produced a result that is better than the ideal case according to Section 3.2.2.

#### 3.2.4 The UTDSP Packing Algorithm

The original pseudo-code for the UTDSP packing algorithm was proposed by Mazen Saghir [2] and was then modified by the author to incorporate the subset packing method. The modified UTDSP packing algorithm, which is based on the two-cluster configuration, is described in Figure 3.6. This algorithm starts with a given list of unpacked instructions and two empty lists that are used to store the packed long-instruction words for the two clusters. The main loop is executed as many times as there are active fields. An active field is a member operation that has not been packed into its corresponding decoder-memory bank. At the beginning of each loop iteration, the number of active fields for each decoder-memory bank is calculated to decide its rank and the target bank in the current iteration. The highest rank (rank 7) is assigned to the decoder-memory bank that has the least number of active fields, while the lowest rank (rank 1) is assigned to the one that has the most number of active fields. The target bank is the one that has the highest rank (rank 7). Recall the situation described in Figure 3.2, where the memory banks with fewer operations suffer the most from the poor instruction ordering. Therefore, the long instructions that have operations to be stored in the target bank should be processed first.

Once the target bank has been determined, the unpacked instructions are divided into two lists: a candidate list and a reserve list. The candidate list contains instructions that have member operations associated with the target bank; the reserve list contains the remaining instructions. The instruction with the highest cost — the sum of the ranks of the memory banks associated with the operations contained — is then removed from the candidate list. The removed instruction will be added into the decoder-memory list provided it is not a *subset* of any existing word in the decoder memory list. If it is a *subset* of an existing decoder-memory word, it will be packed into the existing word as opposed to being added into the decoder-memory list as a new entry.

```

Input: A list of multi-op instructions

Output: (1) A list of instruction memory words

(multi-op pointers and uni-op operations)

(2) Two lists of long instructions (Cluster A and Cluster B)

Assumptions and Definitions:

(1) Let S be the list of multi-op instructions

(2) Let X be the list of long instructions (decoder memory slots) in cluster A.

(3) Let Y be the list of long instructions (decoder memory slots) in cluster B.

(4) An active field is an operation in a multi-op instruction that is to be stored in its

corresponding bank.

(5) A target bank is the memory bank that has the lowest number of active fields.

(6) Candidate list is a list of instructions that has an active field; reserve list is a list

that has no active field.

1. While (there is an active field in cluster A banks) do

2. Count the number of active fields for each bank in cluster A)

3. Choose the target bank.

4. Divide S into candidate list and reserve list according to the target bank.

5. While (there is an instruction in candidate list) do

6. Inst <= remove the instruction with highest cost from candidate list.

(Please refer to Section 3.2.4 for the definition of cost.)

7. Search existing slots in X for a sharable slot.

8. If (sharable slot is found) then

9. Pack Inst into the sharable slot found in X.

Else

10. Fit_list <= find instructions that are a subset of Inst from reserve list.

11. While (there is an instruction in Fit list) do

13. Best fit <= remove the instruction with highest cost

from Fit list.

14. If (Best_fit is a subset of Inst) then

Inst <= Pack Best fit into Inst.</pre>

15. Add Inst to X.

16 Repeat step 1 to 15, replace all Xs by Ys and cluster A by cluster B.

```

**Algorithm**: Two-cluster packing and slot-sharing method for Decoder Memory

Figure 3.6: The UTDSP packing algorithm

To use the empty fields in the newly added decoder-memory word, the reserve instructions are next searched for the instruction with the highest cost that can be packed into the memory word. The search is continued until no more instructions in the reserve list can be packed into the current decoder-memory word. After all instructions in the candidate list are processed, a new iteration starts again until all the active fields are stored. Because the decoder memory has two clusters, this packing process, described above, will be repeated for the second cluster.

# 3.3 Implementation of the UTDSP Packing Software System

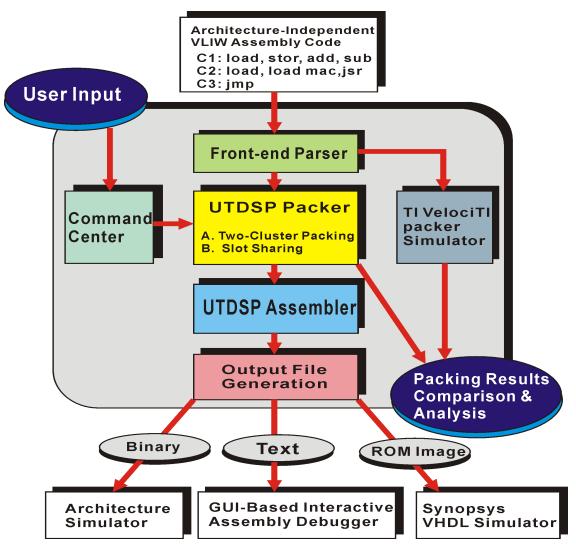

The UTDSP long-instruction packer, which was implemented based on the algorithm described in the previous section, not only performs the two-cluster packing, but also parses assembly code and generates associated files for instruction simulation, assembly debugging, and VHDL simulation. Figure 3.7 illustrates the software modules in the UTDSP packer and the data flow between the modules and other development tools.

The UTDSP packer consists of a front-end assembly parser, the two-cluster packing kernel, an assembler, a TI VelociTI packing simulator, an output file generator, and a command center. The command center takes the hardware configuration of the UTDSP as input and sets up corresponding packing constraints for the packing kernel. The front-end parser parses VLIW assembly code and generates appropriate error messages when a syntax error is found. The packing kernel performs the UTDSP packing algorithm and passes the results to the assembler, which calculates addresses and encodes instructions. Finally, the output file generation module converts the packing results into various formats for simulation purposes. The VelociTI packing module uses the algorithm adopted by the Texas Instruments' new VelociTI architecture to pack the long instructions; the packing result of this VelociTI packer are compared with that of the UTDSP packer for benchmarking purposes. Section 3.4 details the comparison results.

#### 3.3.1 Implementing the UTDSP Packer Using C++ Template Technology

As shown in Figure 3.7, the UTDSP packer needs not only a good packing algorithm, but also a powerful ability to handle the list-intensive processing in the software modules. Moreover, to ease the development and exploration of different packing algorithms, robust underlying data structures are needed to process the required computations. The most important data structure required

Figure 3.7: The UTDSP packer and software system

is a linked list that operates on many different data types — from both built-in and user-defined records — with associated functions such as insertion, deletion, merging, sorting, and binary search.

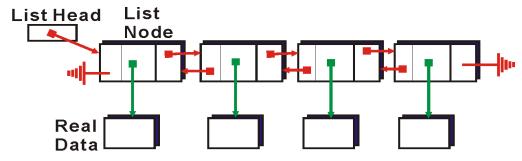

One way to build such a linked list is to use generic data structures. Figure 3.8 shows an internal representation of the generic linked list in C language. The list will have the same structure regardless of whether it stores strings, integers, floats, or user-defined data types. Note that the data items are not stored in the nodes of the list. Instead, each node contains a pointer to its data item. The fact that the data items don't reside in the nodes themselves leads to several drawbacks.

Figure 3.8: Generic linked list in C

First, pointer dereferencing is needed to get the actual value of a data item, rather then looking directly in the node. Second, a function pointer to the comparison function specific to its associated data type must be passed into procedures such as sorting and merging. This means that comparison functions must be explicitly constructed even for built-in data types such as integer and float.

C++ templates solve the problems mentioned above and provide several advantages over the generic data structures in C. First, neither constructing explicit comparison functions nor passing pointers to the sorting procedures is needed. By overloading the comparison operators such as ">", "<", and "=", comparisons of user-defined data types can be stated in the same format as that of built-in data types (ex. A > B). Second, a robust garbage collection mechanism can be encapsulated inside object destructors to completely eliminate memory leak problems, which often occur in the generic data structure implementations in C. For these advantages, the C++ template technique is used for the implementation of the UTDSP packer.

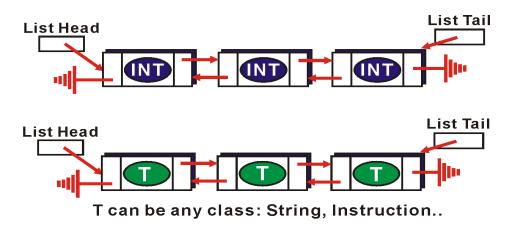

The most important part in the implementation of the UTDSP packer and assembler systems is List<T>— a C++ container template class that can store data items of any data type and perform various operations, such as insertion, deletion, sorting, and search, on its data items. Figure 3.9 shows the internal representation of List<T>. The argument class T represents all data types that are to be stored in the list container. Various user-defined classes that can be stored in List<T> were implemented to ease the development of the UTDSP packer. The user-defined classes include Token, DecoderMemory, and DataMemory, which are used to store parsed tokens, decoder-memory words, and data-memory words, respectively.