### ECE 1749H: Interconnection Networks for Parallel Computer Architectures:

### Flow Control

Prof. Natalie Enright Jerger

### Announcements

- Project Progress Reports

- Due March 9, submit by e-mail

- Worth 15% of project grade

- 1 page

- Discuss current status of project

- Any difficulties/problems encountered

- Anticipated changes from original project proposal

Winter 20

ECE 1749H: Interconnection Networks (Enright Jerger)

### Announcements (2)

- 2 presentations next week

- Elastic-Buffer Flow Control for On-Chip Networks

- Presenter: Islam

- Express Virtual Channels: Toward the ideal interconnection fabric

- Presenter Yu

- 1 Critique due

Winter 201

### Switching/Flow Control Overview

- Topology: determines connectivity of network

- Routing: determines paths through network

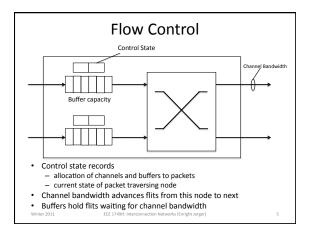

- Flow Control: determine allocation of resources to messages as they traverse network

- Buffers and links

- Significant impact on throughput and latency of network

Winter 20

ECE 1749H: Interconnection Networks (Enright Jerger)

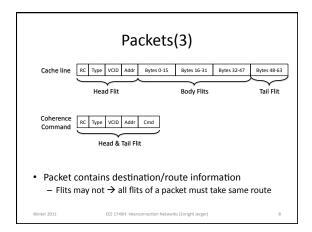

### **Packets**

- Messages: composed of one or more packets

- If message size is <= maximum packet size only one packet created

- Packets: composed of one or more flits

- Flit: flow control digit

- Phit: physical digit

- Subdivides flit into chunks = to link width

Winter 20:

# Packets (2) Message Header Payload Packet Route Seq# Head Flit Flit Type VCID Head, Body, Tail, Head & Tail Off-chip: channel width limited by pins Requires phits On-chip: abundant wiring means phit size == flit size Witter 2011 ECE 1749H: Inter connection Networks (Enright Jerger) 7

### Switching

- Different flow control techniques based on granularity

- Circuit-switching: operates at the granularity of messages

- Packet-based: allocation made to whole packets

- Flit-based: allocation made on a flit-by-flit basis

Vinter 2011 ECE 1749H: Interconnection Networks (Enright Jerger)

### Message-Based Flow Control

- · Coarsest granularity

- · Circuit-switching

- Pre-allocates resources across multiple hops

- Source to destination

- Resources = links

- · Buffers are not necessary

- Probe sent into network to reserve resources

Winter 20:

ECE 1749H: Interconnection Networks (Enright Jerger)

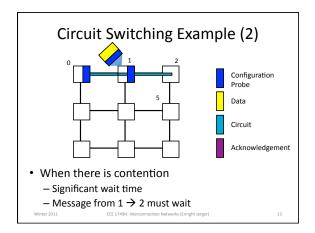

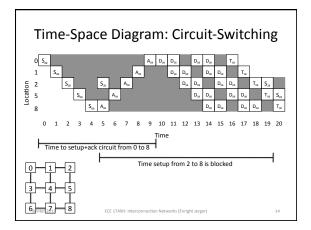

### **Circuit Switching**

- · Once probe sets up circuit

- Message does not need to perform any routing or allocation at each network hop

- Good for transferring large amounts of data

- Can amortize circuit setup cost by sending data with very low perhop overheads

- No other message can use those resources until transfer is complete

- Throughput can suffer due setup and hold time for circuits

- Links are idle until setup is complete

Winter 201

ECE 1749H: Interconnection Networks (Enright Jerger)

11

### Circuit Switching Example Configuration Probe Data Circuit Acknowledgement Significant latency overhead prior to data

- Significant latency overhead prior to data transfer

- Data transfer does not pay per-hop overhead for routing and allocation

ter 2011 ECE 1749H: Interconnection Networks (Enright Jerge

### Packet-based Flow Control

- Break messages into packets

- Interleave packets on links

- Better utilization

- Requires per-node buffering to store in-flight packets

- Two types of packet-based techniques

Winter 20:

### Store and Forward

- Links and buffers are allocated to entire packet

- Head flit waits at router until entire packet is received before being forwarded to the next hop

- Not suitable for on-chip

- Requires buffering at each router to hold entire packet

Packet cannot traverse link until buffering allocated to entire packet

- Incurs high latencies (pays serialization latency at each hop)

Winter 20

ECE 1749H: Interconnection Networks (Enright Jerger)

### Store and Forward Example Total delay = 4 cycles per hop x 3 hops = 12 cycles High per-hop latency - Serialization delay paid at each hop Larger buffering required EXELYTORE: Interconnection Networks (Enright Jarger)

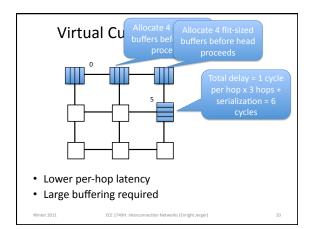

### Packet-based: Virtual Cut Through

- Links and Buffers allocated to entire packets

- Flits can proceed to next hop before tail flit has been received by current router

- But only if next router has enough buffer space for entire nacket

- Reduces the latency significantly compared to SAF

- But still requires large buffers

- Unsuitable for on-chip

Winter 2011

ECE 1749H: Interconnection Networks (Enright Jerger)

19

### Time-Space Diagram: VCT 0 Н В в в т ВВ В Н В В В 5 В В В $0 \quad 1 \quad 2 \quad 3 \quad 4 \quad 5 \quad 6 \quad 7 \quad 8$ Time

# Virtual Cut Through Cannot proceed because only 2 filt buffers available • Throughput suffers from inefficient buffer allocation Winter 2011 ECS 1749H: Interconnection Networks (Enright Jerger) 22

# Time-Space Diagram: VCT (2) O H B B B T 1 H B B B T 2 H B B B T 2 H B B B T 3 B B T 4 B B B T 4 B B B T 5 B B T 6 T B B B T 7 B B B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B T 8 B B B T 8 B B T 8 B B T 8 B B T 8 B B B T 8 B B B T 8 B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T 8 B B B T

### Flit Level Flow Control

- Help routers meet tight area/power constraints

- Flit can proceed to next router when there is buffer space available for that **flit**

- Improved over SAF and VCT by allocating buffers on a flit-basis

Winter 2011 ECE 1749H: Interconner

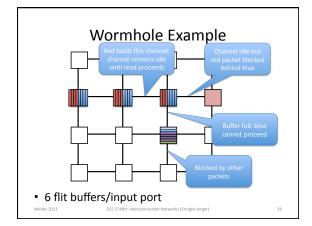

### **Wormhole Flow Control**

- Pros

- More efficient buffer utilization (good for on-chip)

- Low latency

- Cons

- Poor link utilization: if head flit becomes blocked, all links spanning length of packet are idle

- Cannot be re-allocated to different packet

- Suffers from head of line (HOL) blocking

....

ECE 1749H: Interconnection Networks (Enright Jerger)

25

### **Virtual Channels**

- First proposed for deadlock avoidance

- We'll come back to this

- Can be applied to any flow control

- First proposed with wormhole

Winter 2011

ECE 1749H: Interconnection Networks (Enright Jerger)

### Virtual Channel Flow Control

- Virtual channels used to combat HOL blocking in wormhole

- Virtual channels: multiple flit queues per input port

- Share same physical link (channel)

- Link utilization improved

- Flits on different VC can pass blocked packet

Winter 201

CE 1749H: Interconnection Networks (Enright Jerger)

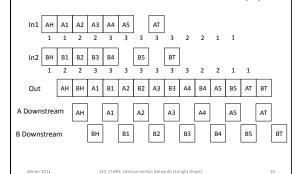

### Virtual Channel Flow Control (2)

### Virtual Channel Flow Control (3)

- Packets compete for VC on flit by flit basis

- Example: on downstream links, flits of each packet are available every other cycle

- Upstream links throttle because of limited buffers

- Does not mean links are idle

- May be used by packet allocated to other VCs

....

ECE 1749H: Interconnection Networks (Enright Jerger)

Virtual Channel Example

Buffer full: blue cannot proceed

• 6 flit buffers/input port

• 3 flit buffers/VC

Winter 2011 ECE 1749H: interconnection Networks (Enright Jarger) 32

### Summary of techniques Links Buffers N/A (buffer-Circuit-Setup & Ack Messages Switching Head flit waits Store and Packet Packet Forward for tail Virtual Cut Packet Packet Head can Through proceed Wormhole Flit HOL Packet Virtual Flit Flit Interleave flits of Channel different packets

ECE 1749H: Interconnection Networks (Enright Jerger)

### Deadlock

- Using flow control to guarantee deadlock freedom give more flexible routing

- Recall: routing restrictions needed for deadlock freedom

- If routing algorithm is not deadlock free

- VCs can break resource cycle

- Each VC is time-multiplexed onto physical link

- Holding VC implies holding associated buffer queue

- Not tying up physical link resource

- · Enforce order on VCs

....

ECE 1749H: Interconnection Networks (Enright Jerger)

34

### Deadlock: Enforce Order

- All message sent through VC 0 until cross dateline

- After dateline, assigned to VC 1

- Cannot be allocated to VC 0 again

inter 2011 ECE 1749H: Interconnection Networks (Enright Jerger)

---

### Deadlock: Escape VCs

- Enforcing order lowers VC utilization

- Previous example: VC 1 underutilized

- Escape Virtual Channels

- Have 1 VC that is deadlock free

- Example: VC 0 uses DOR, other VCs use arbitrary routing function

- Access to VCs arbitrated fairly: packet always has chance of landing on escape VC

- Assign different message classes to different VCs to prevent protocol level deadlock

- Prevent req-ack message cycles

Winter 201

ECE 1749H: Interconnection Networks (Enright Jerger)

### **Buffer Backpressure**

- · Need mechanism to prevent buffer overflow

- Avoid dropping packets

- Upstream nodes need to know buffer availability at downstream routers

- · Significant impact on throughput achieved by flow control

- · Two common mechanisms

- Credits

- On-off

### Credit-Based Flow Control

- Upstream router stores credit counts for each downstream VC

- · Upstream router

- When flit forwarded

- Decrement credit count

- Count == 0, buffer full, stop sending

- Downstream router

- When flit forwarded and buffer freed

- Send credit to upstream router

Upstream increments credit count

ECE 1749H: Interconnection Networks (Enright Jerger)

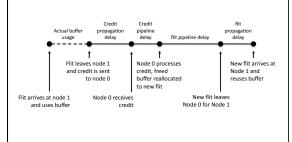

### **Credit Timeline** Flit departs redit round trip delay Process • Round-trip credit delay: - Time between when buffer empties and when next flit can be processed from that buffer entry - If only single entry buffer, would result in significant throughput degradation

- Important to size buffers to tolerate credit turn-around

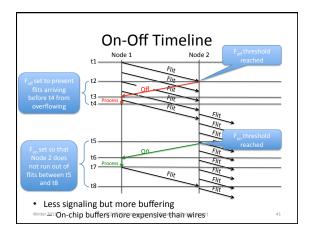

### On-Off Flow Control

- Credit: requires upstream signaling for every flit

- On-off: decreases upstream signaling

- · Off signal

- Sent when number of free buffers falls below threshold  $F_{off}$

- On signal

- Sent when number of free buffers rises above threshold  $F_{on}$

Winter 2011

| Buffer Utilization                                               |           |    |          |          |           |    |      |          |          |    |    |    |

|------------------------------------------------------------------|-----------|----|----------|----------|-----------|----|------|----------|----------|----|----|----|

| Cycle                                                            | 1         | 2  | 3        | 4        | 5         | 6  | 7    | 8        | 9        | 10 | 11 | 12 |

| Credit count                                                     | 2         | 1  | 0        | 0        | 0         | 0  | 0    | 1        | 2        | 1  | 0  | 0  |

| Head Flit                                                        | VA/<br>SA | ST | LT       | BW       | VA/<br>SA | ST |      |          |          |    |    |    |

| Body Flit 1                                                      |           | SA | ST       | LT       | BW        | SA | ST   |          |          |    |    |    |

| Credit (head)                                                    |           |    |          |          |           | С  | C-LT | C-<br>Up |          |    |    | ,  |

| Body Flit 2                                                      |           |    | <u> </u> | <u> </u> | <b>—</b>  | -  |      |          | SA       | ST | LT |    |

| Credit (body 1)                                                  |           |    |          |          |           |    | С    | C-LT     | C-<br>Up |    |    |    |

| Tail Flit                                                        |           |    |          | <u> </u> | -         |    |      |          |          | SA | ST | LT |

|                                                                  |           |    |          |          |           |    |      |          |          |    |    |    |

| Winter 2011 ECE 1749H: Interconnection Networks (Enright Jerger) |           |    |          |          |           |    | 42   |          |          |    |    |    |

### **Buffer Sizing**

- Prevent backpressure from limiting throughput

- Buffers must hold flits >= turnaround time

- Assume:

- 1 cycle propagation delay for data and credits

- 1 cycle credit processing delay

- 3 cycle router pipeline

- At least 6 flit buffers

Winter 20

ECE 1749H: Interconnection Networks (Enright Jerger)

### Actual Buffer Usage & Turnaround Delay

Winter 2011 ECE 1749H: Interconnection Networks (Enright Jerger) 44

### Flow Control and MPSoCs

- Wormhole flow control

- Real time performance requirements

- Quality of Service

- Guaranteed bandwidth allocated to each node

- Time division multiplexing

- Irregularity

- Different buffer sizes

Winter 20

ECE 1749H: Interconnection Networks (Enright Jerger)

### Flow Control Summary

- On-chip networks require techniques with lower buffering requirements

- Wormhole or Virtual Channel flow control

- Avoid dropping packets in on-chip environment

Requires buffer backpressure mechanism

- Complexity of flow control impacts router microarchitecture (next)

|  |  | <br> |

|--|--|------|