micromanipulator. Deposition of dots and lines with diameters and widths ranging from 80 nm to some tens of microns are achieved by the application of voltage pulses between 0.5 V and 20 V with 0.5  $\mu$ s to 1 ms length. An example is shown in Fig. 2. Control of ionic current is possible because

Fig. 2 Au line deposited on GaAs by electrolytic direct writing process

of the small size of the tip, the glass insulation and the short pulses applied. Deposition of dots is possible with single pulses, tip retraction, and discharging of the tip between pulses. Writing of lines is possible without retraction and discharging. The structure size is mainly influenced by the radius of the tip and the amount of transported charge depending on the pulses. Linewidth is additionally influenced by the tip movement between the pulses. The mechanism of deposition can be understood by a model, recently presented by Jacobs et al.<sup>9</sup> The GaAs surface in contact with the electrolyte is depleted and the application of voltage lowers the barrier for electrons so that Au<sup>+</sup> ions are deposited. Small nuclei, already deposited, lower the barrier compared to other parts of the surface and preferential deposition occurs at these nuclei. These effects allow direct writing of dots and lines. Other metals can of course be similarly deposited.<sup>10</sup>

Conclusion: New processes for etching and metallisation of GaAs in the submicron range have been presented. By the use of electrolytic solutions in pulsed operation, soft etching of GaAs towers with 300 nm diameter and deposition of Au-dots and lines down to 100 nm are easily established. Electrolytic etching appears to be promising for the fabrication of quantum dot or well structures with reduced surface damage compared to dry etching. Metal deposition can be used in split gate electrodes or lateral superlattice structures for electron confinement.

Acknowledgment: The authors wish to express their thanks to the Stiftung Volkswagenwerk for financial support of this work.

7th December 1990

A. GRÜB R. RICHTER H. L. HARTNAGEL Technische Hochschule Darmstadt Institut für Hochfrequenztechnik Merckstraße 25 6100 Darmstadt, Germany

## References

- SAKAKI, H.: 'Scattering suppression and high-mobility effect of size-quantized electrons in ultrafine semiconductor wire structures', Jap. J. Appl. Phys., 1980, 19, (12), pp. L735-L738

LEE, K. Y., HANSEN, W., SMITH, T. P., KNOEDLER, C. M., HONG, J. M., and

- 2 LEE, K. Y., HANSEN, W., SMITH, T. P., KNOEDLER, C. M., HONG, J. M., and KERN, D. P.: 'Fabrication of GaAs/GaAlAs transport devices using a deep submicron trench etching technique', J. Vac. Sci. Techn. B, 1989, 7, (6), pp. 1819–1822

- 3 ALLEE, D. R., CHOU, S. Y., HARRIS, J. S., and PEASE, R. F. W.: 'Engineering lateral quantum interference devices using electron beam lithography and molecular beam epitaxy', J. Vac. Sci. Techn. B, 1989, 7 (6), pp. 2015-2018.

- 7, (6), pp. 2015–2019

4 RANDALL, J. N., REED, M. A., and FRAZIER, G. A.: 'Nanoelectronics: Fanciful physics or real devices?', J. Vac. Sci. Techn. B, 1989, 7, (6), pp. 1398–1404

- 5 ISMAIL, K., SMITH, T. P., and MASSELINK, W. T.: 'Magnetic flux commensurability in coupled quantum dots', Appl. Phys. Lett., 1989, 55, pp. 2766-2768

- 6 PANG, S. W.: 'Surface damage on GaAs induced by reactive ion etching and sputtering etching', J. Electrochem. Soc., 1986, 133, (4), pp. 784-787

- 7 GOMEZ-RODRIGUEZ, J. M., VAZQUEZ, L., BARTOLOME, A., BARO, A. M., GRAMBOW, P., and HEITMANN, D.: Topographic imaging of GaAsmicrostructured samples by STM and SEM', *Ultramicroscopy*, 1989, 30, (3), pp. 355-358

- Au-lines on GaAs in an electrolyte', Int. J. Electronics, 1990, 69, (5), pp. 631-634

- 9 JACOBS, J. W. M., and RIKKEN, J. M. G.: 'Photoelectrochemically-induced gold deposition on p-GaAs electrodes', J. Electrochem. Soc., 1989, 136, (12), pp. 3633-3640

- 10 STREMSDÖRFER, G., MARTIN, J. R., CLECHET, P., and NGUYEN-DU: 'Use of Au-In-Pd and Pd-In electroless deposits for ohmic contacts on n-GaAs', J. Electrochem. Soc., 1990, 137, (1), pp. 256-259

## IIR FILTERING ON SIGMA-DELTA MODULATED SIGNALS

Indexing terms: Filters, Digital filters

A design methodology for realising IIR filters on sigma-delta modulated signals is proposed. It is shown that only 3N adders together with minor logic are required to implement an Nth order filter. This type of filtering should prove useful in VLSI technologies where interfaces to analogue signals are required.

Introduction: The use of sigma-delta  $(\Sigma-\Delta)$  modulation has been shown to be an effective method for building high resolution analogue-to-digital (A/D) and digital-to-analogue (D/A) convertors. 1.2 Thus, performing signal processing on  $\Sigma-\Delta$  modulated signals is desirable as this type of processing could be integrated with other systems in VLSI where interfaces to analogue signals are required. Towards this goal, a recent publication describes a method of realising finite-impulse-response (FIR) filters operating on such signals, however, there is presently no method for realising equivalent infinite-impulse-response (IIR) filters. The purpose of this Letter is to propose such an IIR filter design methodology. We will show that to realise an Nth order filter using second-order  $\Sigma-\Delta$  modulators, only 3N adders are required together with some minor logic. This IIR approach should result in smaller VLSI implementations than their FIR counterparts in applications where the oversampling ratio is high and a low-order IIR response can replace a high-order FIR response.

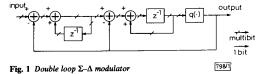

Design approach: The method proposed here makes use of standard IIR filter structures except that filter states exist as both multibit and 1 bit signals. The 1 bit signal is obtained by modulating the multibit signal using a fully digital  $\Sigma$ - $\Delta$  modulator. A digital second-order  $\Sigma$ - $\Delta$  modulator is shown in Fig. 1 where the input and output signals are multibit and 1 bit, respectively.<sup>4</sup> The block  $q(\cdot)$  is a 1 bit quantiser implemented by simply taking the most significant bit. The implementation complexity of this modulator can be simplified to two adders if 2's complement arithmetic is used. This low complexity is due to the first and third adders being realisable by simply changing the sign-bit of the multibit signal because the value

$q(\cdot)$  denotes the 1 bit nonlinear quantisation function

added is either the positive or negative maximum value. In terms of the transfer-function of this modulator within the baseband frequency of interest, the transfer-function appears to be simply  $z^{-1}$  (i.e. a single delay stage at the oversampled rate). This fact is used in the design of the IIR filters to be described.

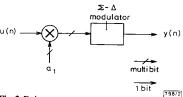

To illustrate the proposed approach, consider first the circuit shown in Fig. 2. A 1 bit input signal u(n) operating at

Fig. 2  $\Sigma$ - $\Delta$  attenuator

At baseband  $Y(z) = a_1 z^{-1} U(z)$

the oversampled rate is multiplied by a multibit fixed coefficient  $a_1$  and the resulting multibit signal is injected into a digital  $\Sigma$ - $\Delta$  modulator giving the output 1 bit signal y(n). In the baseband frequency of interest, it is clear that this circuit behaves as an attenuator circuit, although the modulator does add extra noise to the baseband signal. In terms of hardware complexity, because u(n) is a 1 bit signal, the multiplier can be efficiently realised as a 2-input multiplexer (simply changing the sign bit is not sufficient as 2's-complement arithmetic is assumed in order to realise efficient adders). This multiplexer approach results in the multiplier requiring about 4k transistors in CMOS technology for a k-bit coefficient. For comparison, a k-bit multiplier requires about 20k2 transistors. All multipliers shown in this Letter are of this multiplexer type, a critical requirement as they must operate at the oversampled

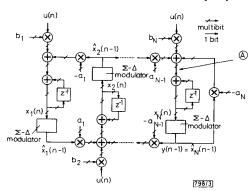

As mentioned above, the  $\Sigma$ - $\Delta$  IIR filtering proposed here can be applied to standard IIR filter structures. However, structures with good performance for oversampled transferfunctions should be used because these types of functions are a natural consequence of using  $\Sigma$ - $\Delta$  modulation. One such structure is a recently developed quasiorthonormal state-space structure.<sup>5</sup> Making use of this structure and the attenuator circuit, described above, results in the Nth-order IIR filter shown in Fig. 3. Each multibit state signal  $x_i(n)$  is applied to a  $\Sigma$ - $\Delta$  modulator resulting in a 1 bit signal  $\hat{x}(n-1)$  that closely approximates  $x_i(n-1)$  over the baseband frequency. Note

Fig. 3 Nth order  $\Sigma$ - $\Delta$  IIR filter using quasiorthonormal structure Note that all multiplications involve a single bit signal

that all the additions shown in Fig. 3 need not be realised as adders. For example, the signal at node A takes on only one of eight possible values and is therefore more efficiently realised as an eight-input multiplexer rather than two adders. In fact, the only adders required are the two in each modulator and one for each filter state. With these simplifications, it is clear that for an Nth order filter using second-order  $\Sigma$ - $\Delta$ modulators, only 3N adders are required together with some

minor logic. This low amount of complexity should make this type of filtering very economical in a VLSI technology.

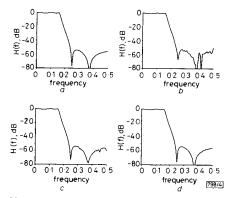

Simulation results: To demonstrate the validity of this approach, a fifth-order prototype filter was simulated for three different oversampling ratios, R = 32, 64, and 128. To measure the frequency response, sine waves at varying frequencies were first passed through a  $\Sigma$ - $\Delta$  modulator, then the filter, and finally an FFT and Hamming window of the resulting one-bit stream indicated the magnitude response at the sine wave's frequency. Although this method of measurement is much more computationally intensive than using an impulse response (as in Reference 3), it allows more power at each frequency and therefore gives a more realistic estimate of the signal-to-noise performance of the filter. The frequency responses for the three filters along with the ideal response are shown in Fig. 4. Here, we see that the signal-to-noise performance improves for higher oversampling ratios, as expected.

Fig. 4 Frequency responses of fifth-order lowpass filter for varying values of oversampling ratio R

- a ideal

- b R = 32

- d R = 128

Conclusions: A design methodology for realising IIR filters on  $\Sigma$ - $\Delta$  modulated signals was proposed. The method makes use of standard IIR filter structures except that multibit filter states also exist as one-bit signals obtained by modulating the multibit signals. It was shown that only 3N adders together with minor logic are required to implement an Nth order filter using second-order modulators. Future work involves performing a comprehensive noise analysis and investigating other filter structures. This type of filtering should prove useful in VLSI technologies where interfaces to analogue signals are required.

## D. A. JOHNS

D. M. LEWIS

17th December 1990

Department of Electrical Engineering University of Toronto Toronto, Ontario M5S 1A4, Canada

## References

- SIGNORE, B. P., KERTH, D. A., SOOCH, N. S., and SWANSON, E. J.: 'A monolithic 20-b delta-sigma A/D converter', IEEE J., 1990, SC-25, pp. 1311-1317

- MATSUYA, Y., UCHIMURA, K., IWATA, A., and KANEKO, T.: 'A 17-bit oversampling D-to-A conversion technology using multistage noise shaping', *IEEE J.*, 1989, SC-24, pp. 969-975

- WONG, P. W., and GRAY, R. M.: FIR filters with sigma-delta modulation encoding, *IEEE Trans.*, 1990, ASSP-38, pp. 979-990

- CANDY, J. C.: 'A use of double integration in sigma-delta modulation', IEEE Trans., 1985, COM-33, pp. 249-258

- JOHNS, D. A., SNELGROVE, W. M., and SEDRA, A. S.: 'Adaptive recursive state-space filters using a gradient-based algorithm', IEEE Trans., 1990, CAS-37, pp. 673-684