KCS PINT

PROCEEDINGS

(C Shith

# 1974 IEEE INTERNATIONAL SYMPOSIUM ON CIRCUITS AND SYSTEMS

San Francisco, California APRIL 22-25, 1974

IEEE CATALOG NO. 74CH0818-5 CAS LIBRARY OF CONGRESS CATALOG CARD NO. 73-86306 A LOW-DISTORTION OSCILLATOR WITH FAST AMPLITUDE STABILIZATION

Eric Vannerson and K.C. Smith Department of Electrical Engineering, University of Toronto Toronto, Canada

#### Abstract

An improved technique is proposed for stabilizing the output of a variable-frequency RC sine-wave oscillator. Very low harmonic distortion figures and fast amplitude settling are achieved together by sampling the peaks of the output waveform to produce a dc voltage having virtually no ripple content. A simplified analysis of the stabilization loop is included, and the effects of non-ideal sampling on distortion are considered.

#### INTRODUCTION

A practical sine-wave oscillator cannot be constructed entirely from linear elements, since some form of non-linearity is required to stabilize the output amplitude. This non-linearity usually contributes in some measure to harmonic distortion in the output waveform. When a lamp or thermistor is used to control the output level, for instance, as in the classical Wien bridge, harmonic distortion is considerable at low frequencies because the lamp or thermistor resistance changes significantly over one cycle of the output. Increasing the thermal time constant reduces the distortion, but increases the amplitude settling time. When more precise control of the output level is required than can be obtained with a lamp or thermistor, some form of ac-to-dc converter is generally used with a voltage-controlled attenuator to regulate the output amplitude by adjusting a feedback gain within the oscillator [1]. Just as is the case for the lamp or thermistor, however, it is found that a compromise must be made between harmonic distortion and the response time of the amplitude stabilization mechanism. The problem in this case is to convert amplitude information instantaneously into a dc voltage. This dc voltage must have as little superimposed ripple as possible, since this ripple, when multiplied by a sinusoid at the fundamental frequency in the voltage-controlled attenuator, will introduce harmonic components into the oscillator output. A low-pass filter can be used following the rectifier, but this results in slower amplitude transient response. If the ac-to-dc converter is a simple half-wave rectifier, for instance, .1% distortion corresponds to an amplitude settling time of several hundred cycles. In an earlier paper [2], a method was proposed for reducing the product of settling time and total harmonic distortion by a factor of about thirty by using an improved rectifier having less ripple in its output. Although this is certainly a considerable improvement, a still better method of amplitude regulation is required if quick settling is to be had in combination with distortion limited only by the capabilities of the operational amplifiers used, rather than by the amplitude stabilization system.

One fairly straightforward solution is to replace the rectifier by a sample/hold which samples the oscillator output over some interval around its peak [3]. The amplitude regulation system is then a hybrid of discrete-time and continuous-time elements which can be optimized by z-transform methods. The effects of non-ideal behaviour in the sample/hold (such as finite sampling time and decay between samples) on harmonic distortion can be determined by Fourier analysis.

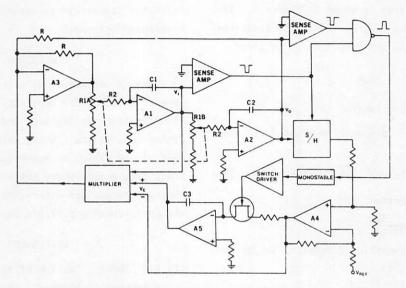

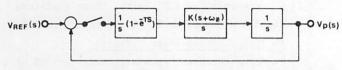

Figure 1 is a simplified schematic diagram showing this method of amplitude regulation. Figure 2 is block diagram of the stabilization system. The oscillator itself is a cascade of two integrators Al and A2 with an inverter A3. This arrangement can be looked upon as a state-variable filter [4] in which the Q-controlling resistor has been replaced by a current-output analogue multiplier. Dual potentiometer Rl varies the frequency of oscillation over slightly more than a decade. The output voltage  $V_0$  is sampled at the positive-going zero crossings of  $V_1$ , which are concident with the positive peaks of V<sub>0</sub>. Since V<sub>0</sub> and V<sub>1</sub> are in accurate quadrature, the samples are always well centered around the peaks of  $V_0$ . The output of amplifier A4 is proportional to the difference between the sampled peak  $\rm V_{p}$  and a reference voltage  $\rm V_{REF}.$ This error signal is applied to the multiplier along with its integral from A5. For optimum performance over a decade of frequency, the integrator gain must be changed in proportion to the oscillator frequency. This can be done conveniently by switching the input resistor into the circuit four times per oscillator period, with a variable duty cycle. The switching waveform is obtained from a monostable multivibrator which is triggered at the zero crossings of the quadrature outputs of the oscillator. Since the switch "on" time is fixed, duty cycle is proportional to frequency. If the maximum duty cycle is limited to about 50%, the effect is almost that of an integrator input resistor which is inversely proportional to frequency, as required. An exact analysis of the switched integrator is quite tedious. The interested reader should consult Jury [5], Tou [6], or Liou [7].

Duty-cycle control of the integrator is particularly convenient, since pulses at the zero crossings of one output waveform are required to control the sample/hold. The zero crossings of both outputs can be obtained with very little additional hardware.

## ANALYSIS OF THE STABILIZATION LOOP

An exact analysis of the amplitude stabilization loop can be avoided if only small deviations in output voltage from its steady-state peak value  $V_{po}$  are to be considered. It can be shown [2] that for small disturbances the response of peak output  $V_p$  to a control voltage applied to the multiplier is that of an integrator with transfer function

$$\frac{V_p(s)}{V_c(s)} = \frac{K_m R \omega_0 V_{po}}{2s}$$

(1)

where  $K_{\rm m}$  is the multiplier scale factor relating the output current to the input voltages, R is as shown in Figure 1, and  $\omega_0$  is the frequency of oscillation. This result can be derived by approximating exponential changes in output by linear functions.

The sample/hold is equivalent to a sampling switch followed by a zero-order hold, whose transfer function is  $(1 - e^{-sT})/s$ , where T is the sampling interval. Note that T can be assumed fixed and equal to the oscillator period, since, if the oscillator poles are near the imaginary axis, the multiplier causes them to move almost horizontally in the s plane. That is, the oscillator frequency remains nearly constant as the amplitude changes. The overall transfer function is then

$$G(s) = \left[\frac{1 - e^{-sT}}{s}\right] \left[\frac{K_a(s + \omega_z)}{s}\right] \left[\frac{V_{po}K_mR\omega_0}{2s}\right] \quad (2)$$

where  $K_a$  is a gain constant associated with the error amplifier. In terms of z, the transfer function is

$$G^{*}(z) = \frac{(2KT + K\omega_{z}T^{2})}{2} \left[ \frac{z - \frac{2KT - K\omega_{z}T^{2}}{2KT + K\omega_{z}T^{2}}}{(z-1)^{2}} \right]$$

(3)

.. .. .. .

where

$$K = \frac{K_a v_{po} K_m R \omega_0}{2}$$

(4)

The z-plane root locus is a circle which is centered on the z-plane zero and which passes through the double pole at (1,0). Fast settling will result if the closed-loop poles are placed at the origin, in which case the root locus must be tangent to the imaginary axis. The zero must be positioned at z = .5, hence

$$\frac{2KT - K\omega_Z T^2}{2KT + K\omega_Z T^2} = .5$$

(5)

By conventional root locus techniques, it is apparent that the gain required to place the poles at the origin is given by

$$\frac{2KT + K\omega_Z T^2}{2} = 2 \tag{6}$$

Solving (5) and (6) for KT and  $\omega_z T$  gives

$$KT = 3/2$$

(7a)

$w_{r}T = 2/3$  (7b)

$$\omega_z I = 2/3$$

Combining (4) and (7) yields

$$K_a K_m = \frac{3}{2\pi V_{po} R}$$

(8)

The response at the sampling instants to a unit step added to  $V_{\text{REF}}$  is given by

$$C(z) = \frac{G(z)R(z)}{1 + G(z)} = \frac{2z-1}{z(z-1)} = 2z^{-1} + z^{-2} + z^{-3} + \dots$$

(9)

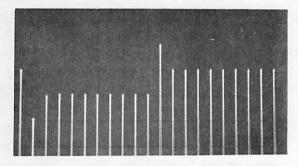

This response is illustrated in Figure 3. The transient response is almost as predicted over the entire frequency range from 100 Hz to 1 kHz.

### HARMONIC DISTORTION DUE TO NON-IDEAL SAMPLING

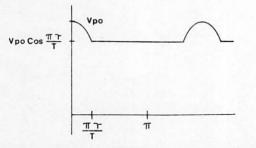

Using the loop parameters given by (7), harmonic distortion due to non-ideal properties of the sample/hold can now be assessed. First consider the effect of sampling the oscillator output over a finite interval. Clearly it is desirable to make this interval as long as possible, to improve sampling accuracy and to reduce the bandwidth requirement of the sample/hold. Long sampling times, however, cause the output of the sample/ hold to appear as shown in Figure 4. The sinewave tip superimposed on the dc hold output is injected into the multiplier and causes harmonic components to appear in the oscillator output.

The sample/hold output of Figure 4 is given by

$$V_{SH} = \begin{cases} V_p \cos \omega_0 t & [0 < \omega_0 t \le (\pi \tau/T)] \\ V_p \cos (\pi \tau/T) & [(\pi \tau/T) < \omega_0 t \le \pi] \end{cases}$$

(10)

where  $\tau$  is the interval over which the output is sampled. The harmonic-frequency components of the multiplier control voltage are derived almost entirely from the proportional, rather than from the integral, feedback, since, from equation (7),  $\omega_z$  is much smaller than  $\omega_0$ . Therefore the multiplier output current is given approximately by

$I_{0} = \begin{cases} K_{a}K_{m}V_{p}^{2} \sin \omega_{0}t \cos \omega_{0}t & [0 < \omega_{0}t \le (\pi\tau/T)] \\ K_{a}K_{m}V_{p}^{2} \sin \omega_{0}t \cos (\pi\tau/T) & [(\pi\tau/T) < \omega_{0}t \le \pi] \end{cases}$ (11)

These functions are odd, hence the Fourier series consists only of sine terms. The coefficients are given by

$$b_{2} = \frac{K_{a}K_{m}V_{p2}}{24\pi} (12m\pi - 8 \sin 2m\pi + \sin 4m\pi)$$

$$b_{n} = \frac{K_{a}K_{m}V_{p2}}{2\pi} \left[ \frac{\sin (n-2)m\pi}{(n-2)(n-1)} - \frac{2 \sin nm\pi}{(n-1)(n+1)} + \frac{\sin (n+2)m\pi}{(n+1)(n+2)} \right]$$

(12)

where m is the fraction of a cycle over which the output is sampled. The harmonic distortion components are given, in per cent, by

$$D_{n} = \frac{100 \ b_{n} \left| \frac{V_{on}}{I_{on}} \right|}{V_{po}}$$

(13)

Combining equations 10, 11, and 13,

$$D_{2} = \frac{25}{12\pi^{2}} (12m\pi - 8 \sin 2m\pi + \sin 4m\pi)$$

$$D_{n} = \frac{75}{\pi^{2}(n^{2}-1)} \left[ \frac{\sin (n-2)m\pi}{(n-2)(n-1)} - \frac{2 \sin nm\pi}{(n-1)(n+1)} + \frac{\sin (n+2)m\pi}{(n+1)(n+2)} \right]$$

(14)

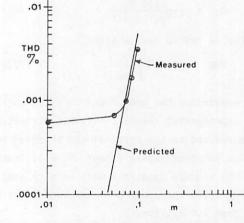

Total harmonic distortion can be computed by summing  $D_n$  over n and taking the square root of the result. The result, which is plotted against m in Figure 5, can be approximated quite well by

$$THD = 503 \text{ m}^5$$

(15)

Figure 5 also shows measured distortion, which agrees reasonably well with equation (14) so long as the predicted distortion is substantially greater than the distortion due to other causes, such as amplifier non-linearities. It may be surprising to note that the sampling pulse can be as wide as .05T without increasing the distortion greatly above its minimum value.

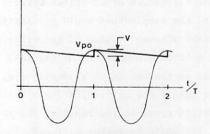

Another source of distortion is the decay of the sampled amplitude between samples. This decay can be reduced by increasing the size of the storage capacitor in the sample/hold, but this results in longer settling times in the sample mode. It is therefore desirable to know how much decay is tolerable. The sample/hold output is shown in Figure 6. If V is small compared to  $V_{po}$ , as it must be if distortion is to be small, the output decay is given approximately by

$$V_{\rm SH} = -\frac{V\omega_0 t}{2\pi}$$

(16)

The multiplier output current is

$$I_0(t) = \frac{K_a K_m V_{DO} V \omega_0 t}{2\pi} \quad \sin \omega_0 t \ [-\pi < \omega_0 t \le \pi] \quad (17)$$

Using (8).

$$I_{0}(t) = \frac{3V\omega_{0}t}{4\pi^{2}R} \sin \omega_{0}t \ [-\pi < \omega_{0}t \le \pi]$$

(18)

This is an even function, and

$$|a_n| = \frac{3V_n}{2\pi^2(n^2-1)}$$

(19)

The nth harmonic distortion component, in per cent of the fundamental, is

$$D_{n} = \frac{100 |a_{n}| \left| \frac{V_{on}}{I_{on}} \right|}{V_{po}}$$

(20)

From equations (13), (19), and (20),

$$D_n = \frac{150 \text{ Vn}}{\pi^2 \text{V}_{\text{po}}(n^2 - 1)^2}$$

(21)

Summing as before over n gives

$$THD = 2.773 \left| \frac{V}{V_{po}} \right|$$

(22)

This expression has been found to agree quite well with experimental results. If this distortion is to be reduced to the level of the measured residual due to other causes (about .0005%), leakage from the storage capacitor must be very small. For  $V_{po} = 10$ , the decay over one cycle must be no more than 1.8 millivolts.

Since the amplitude settling time is limited by the sampling rate, one might reasonably consider sampling more frequently, say twice per cycle. This could be done by sampling  $V_0$  alternately with the output of inverter A3. However, a small amplitude difference or dc offset between the two inputs to the sample/hold would be disastrous. The maximum allowable value of the difference between alternate samples is of the same order of magnitude as the amount of allowable sag, that is, not more than a few millivolts for a distortion contribution equal to the residual due to other causes. It would be rather difficult in practice to achieve a dc offset this small, and it would be virtually impossible to match the two amplitudes correspondingly well.

## CONCLUSION

In short, it appears that the sample/hold approach is most suitable for applications where extremely low distortion is desired, and settling in two cycles is adequate. Using this technique, it is possible to design an economical oscillator for audio frequencies whose noise and distortion characteristics are determined almost entirely by the operational amplifiers employed.

#### REFERENCES

- [1] B.J. Skehan, "Design of an amplitude-stable sine-wave oscillator", <u>IEEE J. Solid-State</u> <u>Circuits</u> (Corresp.), vol. SC-3, pp. 312-315, September 1968.

- [2] E. Vannerson and K.C. Smith, "Fast amplitude stabilization of an RC oscillator," submitted to IEEE J. Solid-State Circuits.

- [3] D. Meyer-Ebrecht, "Fast amplitude control of a harmonic oscillator," <u>Proc. IEEE</u> (Lett.), vol. 60, p. 736, June 1972.

- [4] L.C. Thomas, "The Biquad: Part I Some practical design considerations," <u>IEEE Trans. Circ-</u> <u>uit Theory</u>, vol. CT-18, pp. 350-357, May 1971.

- [5] E.I. Jury, <u>Sampled-Data Control Systems</u>. New York: John Wiley and Sons, 1958, Chapter 9.

- [6] J.T. Tou, <u>Digital and Sampled-Data Control Sys-</u> tems. New York: McGraw-Hill, 1959, Chapter 11.

- [7] M.L. Liou, "Exact analysis of linear circuits containing periodically operated switches with applications," <u>IEEE Trans. Circuit Theory</u>, vol. CT-19, pp. 146-154, March 1972.

Fig. 1. Simplified schematic diagram of the oscillator with amplitude stabilization.

Fig. 2. Block diagram of the amplitude stabilization system.

Fig. 3. Step response of the stabilization loop.

Fig. 4. Output of sample/hold for non-zero sampling time.

Fig. 5. Distortion versus normalized sampling time.

Fig. 6. Output of sample/hold showing decay between samples.