## A DISCUSSION ON THE THEORY

## OF LOGIC VALUE REDUNDANCY

Mou HU

Dept. of Computer Engineering Shanghai Institute of Railway Technology Shanghai, CHINA 200333

K.C.Smith

Dept.of Electrical Engineering

University of Toronto

Toronto, Ont., CANADA

#### Abstract

The logic value redundancy technique is a new redundancy technique which differs from the conventional redundancy techniques. This paper preliminarily discusses the theory of logic value redundancy. The contents include its concepts, theory and applications.

#### I. Introduction

To achieve the goal of fault-tolerant computing, various redundancy techniques are used nowadays. Although means adopted by different redundancy techniques differ from each other, they are all based on the same principle. This principle can be stated as follows, "very high reliability which is not reachable by conventional design methods can be reached if more resources are used than those used in conventional designs". Additional resources used to achieve high reliability are called extra resources. They might be extra hardware, extra software, extra information or extra time. The corresponding redundancy techniques are called hardware redundancy, software redundancy, information redundancy or time redundancy respectively (1)

Logic value redundancy discussed in this paper is a new redundancy technique which differs from conventional redundancy techniques. Since this technique is still under development, its theory is not mature. As an attempt to develop theory for this technique, this paper preliminarily discusses concepts, theory and applications of the theory of logic value redundancy.

## II. Concepts

Logic value redundancy is a technique to operate an n valued logic system (n>2) in an m valued mode (m>2), where n>m (2). In other words, the system can provide n logic values, but only m of them (m<n) are used as normal working logic

values. In this mode, (n-m) logic values of the system are redundant. These redundant logic values are extra resources in logic value redundancy technique. They can be used to provide properties such as self-checking, fail-safe, error-correcting etc., so that to raise testability and reliability of the system.

Logic value redundancy technique can be thought as one of information redundancy tethniques. This is because that information is represented in coded form in logic systems. For an n valued system with k information digits, the maximum information capacity which can be represented or processed

by the system is n<sup>k</sup>. It can be seen that there will be two basic approaches to produce redundant information in information redundancy techniques. They are:

- l. To increase k, number of information digits. In conventional error-detecting or error-correcting code techniques, the system radix n is fixed to 2, but the number of information digits, k, is increased due to adding checking digits.

- To increase system radix n while k is fixed. This leads to logic value redundancy technique discussed in this paper.

Until now, researches for the first approach, error-detecting or error-correcting codes are conducted thoroughly. This approach is widely accepted. But for the second approach, logic value redundancy, more research work is needed.

Since logic value redundancy and error-detecting or error-correcting codes belong to the same class of redundancy techniques, i.e. information redundancy techniques, we will consult the theory of error-detecting and error-correcting codes to establish the theory of logic value redundancy.

# III. Theory

Assume the logic value set of an n valued logic system is Q. When this system is implemented, these logic values should be represented by some physical parameters of the circuit such as voltage

values, current values or charge values etc.

When this n valued logic system is used as a logic value redundancy system, the following definitions are useful.

#### Definition 1

For two logic values a,b(Q, if the physical parameter value representing a is greater than or equal to the physical parameter value representing b, it is said that logic value a is greater than or equal to logic value b, denoted as a>b.

Any two values of a same type of physical parameter are comparable, so the logic value greater than or equal to relation in Q is a linear order, and can be represented as a Hasse diagram.

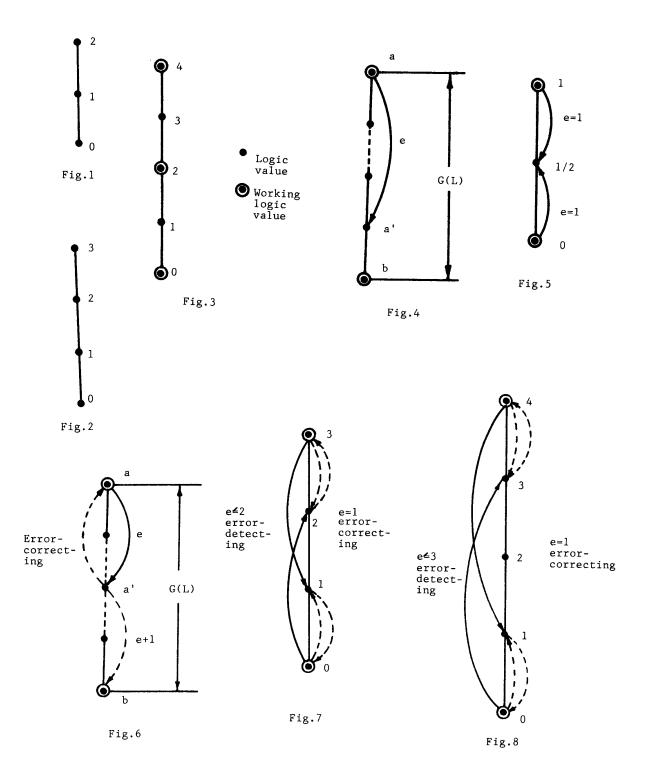

Example 1. Assume the logic value set of a ternary logic system is  $Q=\{0,1,2\}$ . In the logic circuit, these logic values are represented as voltage values. Logic value 0 corresponds to -5V. Logic value 1 corresponds to OV. Logic value 2 corresponds to +5V. The logic value greater than or equal to relation in Q can be derived by comparing the corresponding voltage values. This results in the Hasse diagram shown in Fig.1. The following relations are satisfied:

$2 \ge 2$ ,  $2 \ge 1$ ,  $2 \ge 0$ ,  $1 \ge 1$ ,  $1 \ge 0$ ,  $0 \ge 0$ .

#### Definition 2

For any two logic values a,b (Q, where a to, if there is no third logic value c, where c#a, c#b, which satisfies the following relation:

(a>c and c>b) or (b≥c and c>a), then it is said that logic values a,b are adjacent.

Example 2. For the logic system of Example 1, logic values 0 and 1 are adjacent, and so are logic values 1 and 2. But logic values 0 and 2 are not adjacent, since there is a third logic value I which satisfies 2≥1 and 1≥0.

When a logic value changes to an adjacent logic value, no third logic value will be passed. But for a pair of logic values which are not adjacent, the above feature is not true. This concept is useful for analysis of logic errors produced by faults or disturbances.

#### Definition 3

Logic value distance between any two logic values a,beQ (called value distance for short, and denoted as D(a,b)) is defined as:

- 1. If a=b, D(a,b)=0.

- If a and b are adjacent, D(a,b)=1.

- 3. If a and b are not adjacent, there must be a third logic value c (c≠a, c≠b) satisfying (a≥c and  $c \geqslant b$ ) or  $(b \geqslant c \text{ and } c \geqslant a)$ , then D(a,b)=D(a,c)+D(c,b).

Applying 2 and 3 repeatedly, it is possible to get the logic value distance between any two logic values in 0.

From the above definition, it is known that an arc in a Hasse diagram represents a value distance

1. The value distance between two logic values a,b

is equal to the number of arcs through which a changes to b or b changes to a unidirectionally. Equation D(a,b)=D(b,a) is always true.

Example 3. A quaternary logic system is shown in Fig.2. From Fig.2 we can get:

D(0,2)=2,

D(1,3)=2,

D(0,3)=3,

D(2,2)=0.

#### Definition 4

The working value distance of a logic value redundancy system L is the minimal value distance between each pair of working logic values in L. It can be denoted as G(L).

Example 4. In a logic value redundancy system L, the logic value set is Q={0,1,2,3,4}. Their " greater than or equal to" relation is shown in Fig.

Logic values 0,2 and 4 are chosen as working logic values, then G(L)=2.

In the discussion that follows, word "error" is used to represent the logic value discrepancy caused by circuit faults or external disturbances.

If an error forces a working logic value a changing to logic value b, the distance of this error is e=D(a,b).

Example 5. In the system L of Example 4, if an error changes logic value 0 to logic value 2, the distance of this error is e=D(0,2)=2.

Based on the above definitions, two important conclusions of logic value redundancy techniques can be described as two Theorems.

#### Theorem 1

To detect errors with distance e, the working value distance G(L) of a logic value redundancy system L should satisfy the following condition: G(L)≥e+1.

## Proof:

An error with distance e will change a working value of the logic system by e distance towards increasing direction or decreasing direction. Not loosing generality, assume this error changes a working value a to a' towards decreasing direction, where D(a,a')=e. To make this error detectable, the nearest working value b which is smaller than a cannot take the value a' or any logic value between a and a' (see Fig.4). This means D(a,b)≽D(a,a')+1= e+1. So the working value distance of the system should be

G(L)≽e+1.

Example 6. Fig. 5 shows a Hasse diagram for a 2-of-3-valued system. The working value distance of this system is

G(L)=2.

This system can detect all errors with e=1.

#### Theorem 2

To correct errors with distance e, the working value distance G(L) should be:

G(L)≽2e+1.

The error correcting strategy of a logic value redundancy system is to correct the erroneous logic value to the nearest working value.

#### Proof:

Not loosing generality, we only consider the case in which an error with distance e changes a working value a to a' towards decreasing direction. To make this error correctable, the distance between a and the nearest working value b towards decreasing direction should be larger than the distance between a' and a. Because D(a,a')=e, we have  $D(a',b) \gg D(a,a')+1=e+1$ . The distance between two working values a and b should be  $D(a,b)=D(a,a')+D(a',b) \gg 2e+1$  (see Fig.6).

Since b is the nearest working value to a, their distance is the working value distance. So we have  $G(L) \ge 2e+1$ . 0.E.D.

Example 7. For the quaternary system of Example 3 (Fig.2), if logic values 0 and 3 are chosen as working values, the working value distance of the system is G(L)=3. This system can correct errors with e=1. For example, erromeous logic value 2 can be corrected to the nearest working value 3.

#### IV. Applications

The above stated theory can be used as the theoretical basis of design and analysis of logic value redundancy systems.

As the first application example, this theory will be used to analyze the 2-of-3-valued systems (2,4,5) which is one type of logic value redundancy systems.

The logic value set of the 2-of-3-valued systems is  $Q=\{0,1/2,1\}$ . Logic values 0 and 1 are chosen as normal working values of the systems (see Fig.5). The working value distance of the system is G(L)=2. Thus these systems can detect all errors with e=1.

It is shown by analysis of these systems that there are three types of faults: masked faults, mid-seeking faults and mid-rejecting faults.

For masked faults, e=0, so the system produces no error when this type of faults occur. On the other hand, this type of faults cannot be detected by either concurrent testing or off-line testing.

For mid-seeking faults, e=1. The system will produces erroneous value 1/2 when this type of faults occur. As a result this type of faults are detectable during system normal operation.

For mid-rejecting faults, e=2. They change a working value to another working value. So they  $% \left\{ 1,2,\ldots ,n\right\}$

are undetectable during normal operation. However they can be treated as hardcore of the system and can be tested in off-line mode.

Next, we will use the above stated theory to discuss some new schemes of logic value redundancy techniques.

In the quaternary system shown in Fig.7, if logic values 0 and 4 are chosen as working values, we have G(L)=4. This system will detect all errors with  $e \le 3$ , or it will correct all errors with e = 1.

If the same system is used in ternary mode by choosing 0,2 and 4 as working logic values, the working value distance of the system is G(L)=2. This system will detect all errors with e=1.

This paper is a preliminary discussion on logic value redundancy technique. To make this theory more substantial more research on this area is needed. Some topics for further developments of concepts and theory include logic value redundancy systems with multiple-valued coding (6) and fail-safe system based on logic value redundancy (7)

#### References

- 1 T.Chen and G.Chen, "Diagnosis and fault-tolerance of digital systems", Defence industry publisher, Beijing, 1981.

- 2 Mou Hu, "A scheme for logic value redundancy-2-of-3-valued self-checking logic systems", Computer Engineering, 1984, No.3, pp.21-27, 1984.

- 3 D.K.Pradhan, Edited, "Fault-tolerant computing: theory and techniques", Chapters 4 and 5, Prentice-Hall, 1986.

- 4 Mou Hu and K.C.Smith, "On the use of CMOS ternary gates to realize a self-checking binary system", Proc. 11th IEEE International Symposium on Multiple-Valued Logic, pp.212-217, May 1981.

- 5 Mou Hu, K.C.Smith and H.T.Mouftah, "Low power 2-of-3-valued CMOS self-checking circuits", Proc. 13th International Symposium on Multiple-Valued Logic, pp.64-69, May 1983.

- Mou Hu and K.C.Smith, "Some new results of 2-of-3-valued logic systems", Proc. 14th IEEE International Symposium on Multiple-Valued Logic, pp.204-209, May 1984.

Mou Hu, "An FT-TSC-FS binary system based on

- 7 Mou Hu, "An FT-TSC-FS binary system based on ternary circuits", Scientia Sinica, Edition A, 1985, No.8, pp.766-772, 1985.