# 30–100-GHz Inductors and Transformers for Millimeter-Wave (Bi)CMOS Integrated Circuits

Timothy O. Dickson, *Student Member, IEEE*, Marc-Andre LaCroix, *Member, IEEE*, Samuel Boret, Daniel Gloria, Rudy Beerkens, *Member, IEEE*, and Sorin P. Voinigescu, *Senior Member, IEEE*

Abstract-Silicon planar and three-dimensional inductors and transformers were designed and characterized on-wafer up to 100 GHz. Self-resonance frequencies (SRFs) beyond 100 GHz were obtained, demonstrating for the first time that spiral structures are suitable for applications such as 60-GHz wireless local area network and 77-GHz automotive RADAR. Minimizing area over substrate is critical to achieving high SRF. A stacked transformer is reported with  $S_{21}$  of -2.5 dB at 50 GHz, and which offers improved performance and less area (30  $\mu$ m  $\times$  30  $\mu$ m) than planar transformers or microstrip couplers. A compact inductor model is described, along with a methodology for extracting model parameters from simulated or measured y-parameters. Millimeter-wave SiGe BiCMOS mixer and voltage-controlled-oscillator circuits employing spiral inductors are presented with better or comparable performance to previously reported transmission-line-based circuits.

*Index Terms*—Inductors, millimeter wave, mixer, self-resonance frequency (SRF), stacked inductors, transformers, voltage-controlled oscillator (VCO).

# I. INTRODUCTION

RECENTLY, silicon technologies have become a viable option for millimeter was a silicon technologies. option for millimeter-wave and high-speed digital circuits with data rates above 40 Gb/s. The potentially large consumer markets have attracted considerable interest in 60-GHz wireless local area network (WLAN) and 77-GHz collision avoidance automotive RADAR, resulting in 60-GHz low-noise amplifiers (LNAs), power amplifiers, and mixers [1], and 80-GHz voltage-controlled oscillators (VCOs) [2] implemented using SiGe HBT technologies. Furthermore, the demonstration of very high-speed SiGe HBT digital building blocks [3] paves the way for highly integrated serial communication transceivers with data rates exceeding 100 Gb/s. Wireless and wireline building blocks reported to date that operate in the millimeter-wave regime rely on microstrip transmission lines for on-chip matching networks and inductive peaking. However, this approach proves to be area intensive, as quarter-wavelengths in silicon dioxide at 60 and 80 GHz

Manuscript received April 21, 2004; revised August 31, 2004. This work was supported in part by Micronet under Contract C.2.T1. The work of T. O. Dickson was also supported by the Natural Sciences and Engineering Research Council of Canada.

Digital Object Identifier 10.1109/TMTT.2004.839329

are approximately 630 and 470  $\mu$ m, respectively. Given the prohibitive mask and fabrication costs in the deep-submicrometer technologies at which silicon becomes commercially feasible for millimeter-wave circuits, area consumption should be minimized if inexpensive components are to be realized. While monolithic spiral inductors and transformers have been very popular in silicon-based technologies at microwave frequencies, their application in millimeter-wave circuits has not been investigated. Mutual coupling in spiral coils allows for larger inductance in less area than transmission-line structures. Furthermore, the increasing number of metal layers available in (Bi)CMOS technologies facilitates the design of three-dimensional (or stacked) inductors and transformers reminiscent of discrete components found at lower frequencies.

This paper reports inductors and transformers suitable for millimeter-wave applications [4]. Design guidelines for planar and stacked millimeter-wave inductors are described in Section II. Section III examines planar and stacked millimeter-wave transformer structures. A stacked transformer is introduced that is ideal for single-ended-to-differential conversion above 40 GHz. A wide-band inductor model is presented in Section IV, along with a methodology for model parameter extraction. Finally, as examples of millimeter-wave circuits employing spiral inductors, the first dc-to-50-GHz broad-band mixer and the first inductor-based 40-GHz VCO are reported in Section V.

# II. INDUCTORS

# A. Millimeter-Wave Design Considerations

For silicon-based inductors in the millimeter-wave regime, loss in the silicon substrate is the dominant mechanism for degradation in the quality factor [5]. We propose that, to minimize these losses, an inductor footprint be made as small as possible. This involves reducing outer diameter, as well as metal linewidth. While inductor design at radio frequencies emphasizes the use of wide metal lines to reduce series resistances, this approach increases capacitance to substrate and reduces the self-resonance frequency (SRF). Circuits employing inductors should operate below the peak-Q frequency of the inductor in order to ensure proper behavior, which emphasizes the need for high SRF. In our designs, reliability concerns due to dc electromigration effects set the lower limit on linewidth. Turn-to-turn spacing is made roughly equal to the dielectric thickness to substrate to lessen the impact of interwinding capacitances and further improve SRF. Wide metal spacing also diminishes

T. O. Dickson and S. P. Voinigescu are with the Department of Electrical and Computer Engineering, University of Toronto, Toronto, ON, Canada M5S 3G4 (e-mail: tod@eecg.toronto.edu).

M.-A. LaCroix and R. Beerkens are with STMicroelectronics, Ottawa, ON, Canada K2H 8R6.

S. Boret and D. Gloria are with STMicroelectronics, F-38926 Crolles Cedex, France.

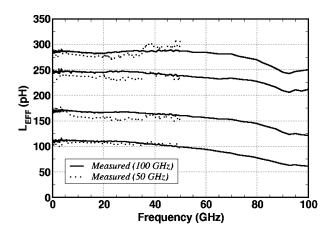

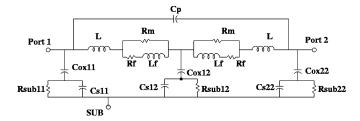

Fig. 1.  $L_{\rm EFF}$  for planar millimeter-wave inductors measured using 50- and 100-GHz network analyzers.

TABLE I

DESIGNED VERSUS MEASURED PLANAR INDUCTOR PERFORMANCE

| DUT | Outer<br>Diameter | L <sub>EFF</sub> @ 40 GHz<br>(Measured/ASITIC) | SRF<br>(ASITIC) |

|-----|-------------------|------------------------------------------------|-----------------|

| D1  | 49 μm             | 290 pH / 270 pH                                | 159 GHz         |

| D2  | 46 µm             | 168 pH / 156 pH                                | 221 GHz         |

| D3  | 39 µm             | 239 pH / 241 pH                                | 170 GHz         |

| D4  | 30 µm             | 115 pH / 101 pH                                | 334 GHz         |

the frequency dependence of the inductance set forth by the proximity effect [6].

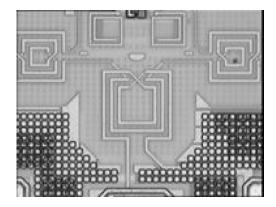

# B. Planar Inductors

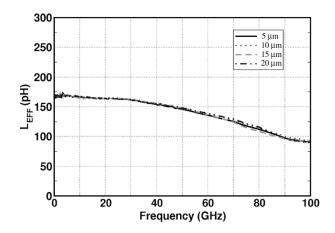

Based on the discussion in Section II-A, a family of square and symmetric [7] planar inductors was designed using ASITIC [8] and implemented in a six-layer copper CMOS back-end [9]. Inductance values range from 100 to 300 pH with outer diameters between 30–50  $\mu$ m. Inductors were measured up to 100 GHz in Crolles, France, and up to 50 GHz in Ottawa, ON, Canada. Cable and probe losses are corrected using load-reflect match (LRM) calibrations with the network analyzer. Furthermore, y-parameters for open and short test structures are measured and deembedded to correct for pad capacitances, lead inductances, and lead resistances, which can add on the order of 40 fF, 50 pH, and 1  $\Omega$ , respectively, to each port. Fig. 1 demonstrates the effective inductance measured using the 50-and 100-GHz network analyzers and extracted as

$$L_{\text{EFF}} = \frac{\text{Im}\left\{y_{11}^{-1}\right\}}{\omega}.$$

(1)

In all cases, the measured inductance was within  $\sim \! 5\%$  of the target value, as summarized in Table I. Slight dips in  $L_{\rm EFF}$  are seen close to 90 GHz in all cases, which underscore the difficulty in measuring and deembedding such small inductance values at very high frequencies. Measurements indicate that the SRF is well beyond 100 GHz in all cases. To the authors' best knowledge, this marks the first verification of ASITIC in the millimeter-wave regime.

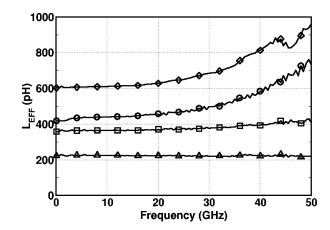

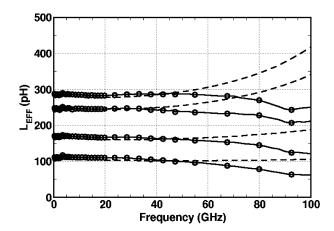

Fig. 2. Measured  $L_{\rm EFF}$  versus frequency for 200-, 370-, 400-, and 600-pH millimeter-wave stacked inductors.

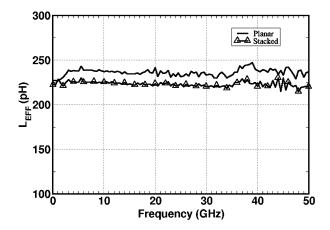

Fig. 3. Measured  $L_{\rm EFF}$  for 220-pH planar and stacked millimeter-wave inductors.

## C. Stacked Inductors

Further reduction in area is achieved using three-dimensional structures [10]. These structures benefit from strong mutual coupling between vertically adjacent metal layers, and can generate the same inductance in less area as compared with planar inductors. Stacked inductors implemented in two or three metal layers were designed with inductance values between 200–600 pH and with outer diameters ranging from 20 to 40  $\mu m$ .  $L_{\rm EFF}$  extracted from measured 50-GHz data is presented in Fig. 2.

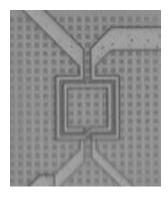

Effective inductances for a planar and stacked inductor with respective outer diameters of 36 and 18  $\mu$ m are shown in Fig. 3. In both cases, self-resonance is beyond the measurement capability. Results indicate that comparable inductance ( $\sim$ 220 pH) in the millimeter-wave regime can be obtained using stacked inductors with significant area reduction over planar inductors. A die photograph of the 220-pH stacked inductor, with two turns in metal 6 and two turns in metal 5, is presented in Fig. 4.

As with planar inductors, reducing area over substrate is paramount in increasing the SRF of stacked inductors. Two stacked inductors of similar inductance were designed, the first using the top two metal layers with an outer diameter of 30  $\mu$ m and the second using the top three metal layers with a 21- $\mu$ m diameter. The smaller inductor footprint results in an improved SRF,

Fig. 4. Die photograph of 220-pH two-metal stacked inductor. Inductor is formed with two turns in metal 6 and two turns in metal 5. The outer diameter is 18  $\mu \rm m$ .

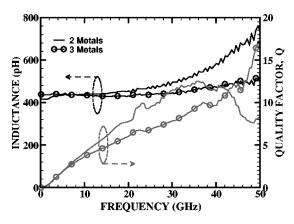

Fig. 5. Measured  $L_{\rm EFF}$  and Q of 420-pH stacked inductors implemented in two and three metal layers.

as seen in the measured  $L_{\rm EFF}$  of Fig. 5. The nearly 50% reduction in total area with more metal layers yields higher SRF, even though the bottom metal layer is slightly closer to the substrate. The effective inductor quality factor is extracted as

$$Q_{\text{EFF}} = \frac{\text{Im}\{-y_{11}\}}{\text{Re}\{y_{11}\}}$$

(2)

It is noted that attempts to implement stacked inductors at lower frequencies (below  $10\,\mathrm{GHz}$ ) have resulted in low quality factors, on the order of 2–3 [11] due to additional via resistance. However, as seen in Fig. 5, the quality factor for millimeter-wave inductors is actually improved by adding more metal layers. While the two-metal inductor has a peak Q of approximately 13, the Q of the three-metal inductor exceeds 15 and has yet to peak at 50 GHz. This underscores the importance of minimizing substrate losses, not series losses, to improve inductor performance at frequencies above 10 GHz.

# D. Impact of CMP Integrity Fill

In sub-0.18- $\mu$ m production technologies with multimetal backends, dummy metal patterns (as seen from the die photograph in Fig. 6) are required to preserve chemical mechanical planarization (CMP) integrity. While placement of these structures is usually automated by computer-aided design (CAD) tools, the layout designer can often specify an exclusion region to prevent dummy fill from being generated in or around inductors. Test structures were designed to assess the impact of varying the spacing of dummy fill from a 160-pH square inductor. Less than 5-pH variation, well within the measurement

Fig. 6. Metal fill patterns for chemical–mechanical planarization integrity near millimeter-wave inductors and transformers in a production 0.13- $\mu$ m SiGe BiCMOS technology.

Fig. 7. Effect of fill pattern proximity on measured  $L_{\rm EFF}$ .

accuracy, is observed (Fig. 7) as the distance from inductor edge to fill pattern is changed. Reducing fill proximity eases layout requirements for circuits employing inductors in state-of-the-art silicon technologies.

### III. MILLIMETER-WAVE TRANSFORMERS

While differential circuit topologies are vital to improve noise immunity in integrated circuits, they often call for the generation of differential signals from single-ended sources. High-speed current-mode logic (CML) or emitter coupled logic (ECL) digital circuits require differential clocks, but only single-ended signal generators are available above 40 GHz. In a wireless system, a single-ended-to-differential converter between a single-ended LNA and a doubly balanced mixer must have low loss to mitigate its impact on the noise figure of a receiver. At lower frequencies, conversion can be achieved via an active balun, or a differential pair with the unused input terminated off chip. However, at millimeter-wave frequencies, poor common-mode rejection renders this approach ineffective, as the differential outputs exhibit amplitude mismatch and phase misalignment. While other approaches have relied on a rat-race coupler for conversion at 80 GHz [12], the area occupied by such a coupler is substantial (250  $\mu$ m × 800  $\mu$ m). An on-chip transformer is ideal for single-ended-to-differential conversion, but has not been attempted in the millimeter-wave regime.

Fig. 8. Die photograph of millimeter-wave planar transformer. Outer diameter is 45  $\mu$ m.

Fig. 9. Die photograph of millimeter-wave stacked transformer. The primary is formed in metal 6 with metal 5 crossovers, while the secondary is formed in metal 4 with metal 3 crossovers. Outer diameter is 30  $\mu$ m.

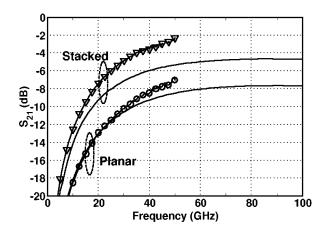

Two transformer structures have been investigated for millimeter-wave applications. The first, a planar transformer, employs symmetrical inductors for the primary and secondary, as seen in the die photograph of Fig. 8. Both windings are formed in metal 6 with metal 5 crossovers. To ensure adequate SRF in the primary and secondary, the design follows the guidelines set forth in Section II. This transformer, with an outer diameter of 45  $\mu$ m, has been utilized to generate differential 43-GHz clocks from a single-ended signal source in a 43-Gb/s decision circuit [13]. However, the coupling coefficient predicted by ASITIC is only 0.5.

Higher coupling can be achieved through the use of stacked structures. A second transformer was implemented by vertically stacking two symmetrical inductors, each with two turns. The primary is formed in metal 6 with metal 5 crossovers, while the secondary is formed in metal 4 with metal 3 crossovers. The outer diameter of the stacked transformer shown in Fig. 9 is 30  $\mu$ m, making it more area efficient than the planar structure while achieving a higher ASITIC-predicted coupling coefficient (k=0.75). While test structure layout prevents a comparison of differential transformer outputs, excellent phase and amplitude matching is expected due to the perfect symmetry of the layout. Fig. 10 compares the measured and simulated input—output coupling  $S_{21}$  of both transformers. The stacked transformer has approximately 5-dB better coupling than the planar transformer over the measured frequency range. Furthermore, the low loss

Fig. 10. Measured (symbols) and ASITIC-simulated (lines) coupling of millimeter-wave stacked and planar transformers.

Fig. 11. Compact broad-band inductor model.

(-2.5 dB at 50 GHz) makes this structure well suited for wireless applications.

# IV. COMPACT MODELING

# A. Inductor Equivalent Circuit

Accurate inductor and transformer modeling is essential to successful millimeter-wave circuit design. It is imperative that a model not only capture all relevant energy loss mechanisms, but also accurately represent the equivalent capacitances. Inadequate capacitance modeling leads to poor prediction of the SRF and, when applied to millimeter-wave LC tuned circuits, can shift center frequencies by at least 10%. A single- $\pi$  equivalent circuit is inadequate, as half of the capacitance to substrate is artificially neglected in simulations if one terminal of the inductor is connected to a small-signal ground. Instead, the distributed nature of the spiral structure is better described by the double- $\pi$  equivalent circuit of Fig. 11 [6].

For the model to be applicable over wide bands, the frequency dependence of the various loss mechanisms must be accurately captured. At millimeter wavelengths, the substrate must be modeled as a distributed RC network, as the period of the wave is less than the dielectric relaxation time of the substrate. This is true for all frequencies above approximately 15 GHz on a  $10\text{-}\Omega \cdot \text{cm}$  silicon substrate. Furthermore, the skin effect confines carriers to the surface of the conductor, leading to increased loss at high frequencies. This can be modeled by a ladder network consisting of  $L_f$  and  $R_f$  shunting  $R_m$ . Additionally, series losses are exacerbated by current crowding due to the proximity effect. As mentioned in Section II, turn spacing is increased in millimeter-wave inductors to lessen the impact of the proximity effect.

Model parameters for the double- $\pi$  equivalent circuit are obtained by direct extraction from ASITIC simulations, or from measurements, as follows. At low frequencies (less than 1 GHz), series inductances and resistances are extracted from  $y_{12}$  as

$$L_{\rm DC} = \frac{\operatorname{Im}\left\{-y_{12}^{-1}\right\}}{\omega} \tag{3}$$

and

$$R_{\rm DC} = \text{Re}\left\{-y_{12}^{-1}\right\}.$$

(4)

Oxide capacitances and substrate resistances for a single- $\pi$ equivalent circuit are extracted as

$$C_{\text{OX1}} = \frac{\left[\text{Im}\left\{\frac{1}{y_{11} + y_{12}}\right\}\right]^{-1}}{\omega} \tag{5}$$

$$C_{\text{OX2}} = \frac{\left[ \text{Im} \left\{ \frac{1}{y_{22} + y_{21}} \right\} \right]^{-1}}{\omega} \tag{6}$$

$$R_{\text{SUB1}} = \text{Re}\left\{\frac{1}{y_{11} + y_{12}}\right\}$$

(7)

and

$$R_{\text{SUB2}} = \text{Re}\left\{\frac{1}{y_{22} + y_{21}}\right\}.$$

(8)

The corresponding double- $\pi$  parameters can then be readily determined as follows:

$$C_{\text{OX}11} = \frac{C_{\text{OX}1}}{2}$$

(9

$C_{\text{OX}22} = \frac{C_{\text{OX}2}}{2}$  (10

$$C_{\text{OX22}} = \frac{C_{\text{OX2}}}{2} \tag{10}$$

$$C_{\text{OX}12} = C_{\text{OX}11} + C_{\text{OX}22} \tag{11}$$

$$R_{\text{SUB11}} = 2 \cdot R_{\text{SUB1}} \tag{12}$$

$$R_{\text{SUB22}} = 2 \cdot R_{\text{SUB2}} \tag{13}$$

$$R_{\text{SUB}12} = 2R_{\text{SUB}1} / 2R_{\text{SUB}2}.$$

(14)

The substrate capacitances  $C_{S11}$ ,  $C_{S12}$ , and  $C_{S22}$  are determined from the dielectric relaxation time of the substrate and their associated substrate resistances  $R_{SUB11}$ ,  $R_{SUB12}$ , and  $R_{\rm SUB22}$ , respectively, such that

$$R_{\rm SUB}C_S = \varepsilon_r \varepsilon_0 \rho_{\rm SI} \tag{15}$$

where  $\varepsilon_r$  is the relative permittivity of the substrate (11.7 for silicon),  $\varepsilon_0$  is the permittivity of free space, and  $\rho_{\rm SI}$  is the substrate resistivity in  $\Omega \cdot m$  [5].

Series inductance and skin-effect parameters  $L, L_f, R_f$ , and  $R_m$  are optimized to obtain broad-band agreement between the equivalent circuit and ASITIC-generated or measured y-parameters. The resulting  $y_{12}$  of the double- $\pi$  model should produce the low-frequency inductance and resistance given by (3) and (4).  $C_P$  can be optimized concurrently with these parameters. However, if the total line length is less than approximately one-

Fig. 12. Measured (solid lines) and modeled (dashed lines)  $L_{\rm EFF}$  as a function of frequency up to 100 GHz.

tenth of a wavelength, the difference in potential along the line is small, as is the electrical energy stored by  $C_P$ . Hence, it does not play a significant role in the inductor model. This does not apply to a differential inductor, as large potential differences can be observed between the two terminals of the inductor.

## B. Model Verification

The compact inductor model is applicable to both planar and stacked millimeter-wave inductors. Models were extracted from ASITIC simulations up to 100 GHz for the family of planar inductors presented in Section II, and are compared with 100-GHz measurements in Fig. 12. While the ASITIC-based models concur with measured data at lower frequencies, discrepancies are noticed above 50 GHz. In all cases, the dc resistance predicted by ASITIC is less than 3.5  $\Omega$ , which calls for careful layout of open and short deembedding structures to minimize lead resistance. Further investigations focusing on deembedding techniques and measurement error above 40 GHz are needed to conclude whether measurements or simulations are responsible for disparities.

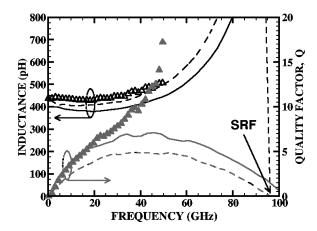

ASITIC simulations of the 400-pH three-layer stacked inductor introduced in Section II are compared in Fig. 13 with measured data. Simulations were performed at two extreme process corners to illustrate the impact of +/-10% variability in backend processing. The first process corner includes low metal sheet resistances and via resistances, along with thicker interlevel dielectrics to represent a "high-Q" process corner, while the "low-Q" corner uses high resistances and thinner dielectrics such that the inductor is closer to the substrate. It is noted that the high-Q process corner results in  $\sim 10$  GHz better SRF and a significant (40%) improvement in Q.

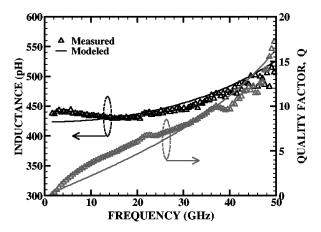

Equivalent circuit parameters for a two-metal 400-pH stacked inductor were extracted from y-parameters measured up to 50 GHz. Excellent agreement between measured and modeled effective inductance and quality factor is shown in Fig. 14 and demonstrates the applicability of the compact inductor model at millimeter waves.

Fig. 13. Measured (symbols) and ASITIC-simulated  $L_{\rm EFF}$  and Q for a 400-pH inductor implemented by stacking three metal layers in series. Simulations for a "high-Q" low metal and via resistance, thick dielectric process corner (solid), and a "low-Q" high metal and via resistance thin dielectric process corner (dashed) are shown.

Fig. 14. Measured (symbols) and modeled (lines)  $L_{\rm EFF}$  and Q for a 400-pH multimetal inductor implemented by stacking two metals in series.

# V. MILLIMETER-WAVE CIRCUITS

While common in lower frequency RF designs, inductors have not been considered to date in millimeter-wave applications. However, both broad- and narrow-band circuits can benefit from their use. In broad-band applications, peaking inductors can extend the bandwidth of resistively loaded amplifiers by up to approximately 40%. For a given bandwidth, current consumption can be traded off for inductance, which aids in the design of low-power transceivers. Furthermore, given the need to reduce inductor footprint to maximize inductor performance at millimeter-wave frequencies, the additional area occupied is not as exorbitant as it is at RF frequencies. In millimeter-wave tuned circuits, a number of silicon-based designs presented to-date (e.g., [1], [2]) make extensive use of transmission-line resonators. However, replacing transmission lines with inductors can reduce chip dimensions and facilitate the production of low-cost components. This paper demonstrates for the first time that inductors can be used in these applications without degrading performance.

To further prove the applicability of these inductors and transformers at millimeter-wave frequencies, a variety of millimeter-wave circuits have been designed and fabricated in a

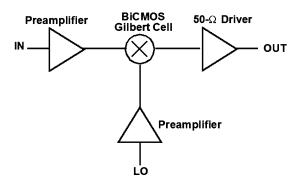

Fig. 15. Block diagram of a dc-to-50-GHz broad-band mixer with transimpedance preamplifiers and BiCMOS Gilbert multiplier.

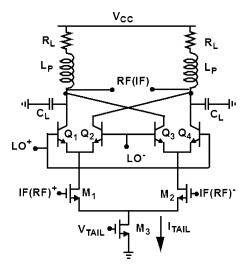

Fig. 16. Circuit schematic of BiCMOS Gilbert multiplier cell, with n-MOS transconductors and SiGe HBT mixing quad.

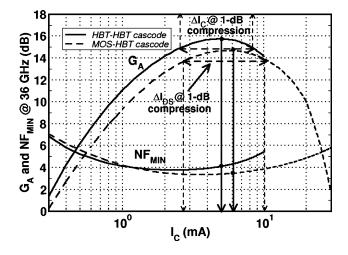

Fig. 17. Available gain and minimum noise figure versus current at 36 GHz for an SiGe HBT cascode (solid) and MOS-HBT cascode (dashed line). Device sizes are 0.2  $\mu m \times 5~\mu m$  for the SiGe HBTs, and 12  $\times$  2  $\mu m \times$  0.13  $\mu m$  for the n-channel MOSFETs. Selection of the bias point for maximum gain is illustrated for both cascodes, along with the current variation that can be tolerated before 1-dB compression occurs.

production 0.13- $\mu$ m SiGe BiCMOS technology with 150-GHz  $f_T$  SiGe HBT from STMicroelectronics, Crolles, France [9]. From these, the first dc-to-50-GHz broad-band mixer and the first inductor-based VCO at 40 GHz are discussed below as

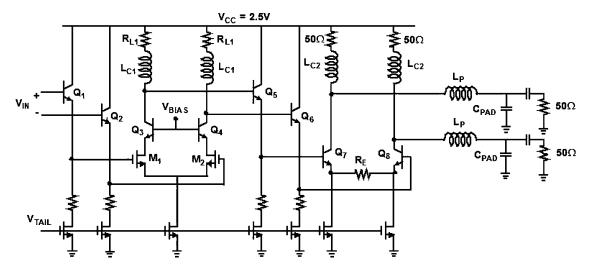

Fig. 18. Circuit schematic of a broad-band BiCMOS 50-Ω output driver employing millimeter-wave spiral inductors.

typical broad- and narrow-band millimeter-wave circuits that benefit from the reduced area afforded by the use of inductors. Additionally, an application of the planar millimeter-wave transformer presented in Section III can be found in [13].

### A. Broad-Band Mixer

Fig. 15 shows a block diagram of a novel dc-to-50-GHz broad-band mixer, which can be used both as an upconverter or downconverter. The circuit consists of a BiCMOS Gilbert multiplier-cell low-noise transimpedance preamplifiers with broad-band  $50-\Omega$  impedance match on the input and local oscillator (LO) paths [12], and a  $50-\Omega$  output driver with 50-GHz bandwidth.

The BiCMOS Gilbert cell, shown in Fig. 16, expounds upon a novel BiCMOS cascode, which has been shown to have excellent performance for millimeter-wave applications due to the low gate resistance of the MOSFET and low-output capacitance of the SiGe HBT [13] while operating with lower supply voltages. The topology consists of MOS transconductors and an SiGe HBT switching quad, the latter of which reduces the required LO power. As will be proven, this BiCMOS topology is ideal for satisfying low-noise and high-linearity requirements simultaneously.

To illustrate the design methodology for the mixer, the available gain  $(G_A)$  and minimum noise figure  $(NF_{MIN})$  of the HBT and BiCMOS cascodes as a function of the collector/drain current are compared in Fig. 17. The bias current is selected such that the gain is maximized at 36 GHz, as shown in this figure. This results in lower noise when a MOS transconductor is employed since  $NF_{MIN}$  is minimized at approximately the same current density at which  $f_T$  peaks for this device [14]. Additionally, larger current variations can be tolerated in the BiCMOS cascode before the gain is reduced by 1 dB, indicating better linearity. To optimize the linearity and bandwidth, the MOS transistors are biased at the peak- $f_T$  current density, with transistor gatewidth (W) given by

$$W = \frac{I_{\text{TAIL}}}{2J_{PfT}}.$$

(16)

The peak- $f_T$  current density of the n-channel MOSFET  $J_{PfT}$  is approximately 0.25–0.3 mA per micrometer of gatewidth, irrespective of technology for CMOS generations below the 0.5- $\mu$ m technology node [15]. For high-speed large-signal operation, SiGe HBT differential pairs are biased at a tail current corresponding to roughly 1.5 times the peak  $f_T$  current density for the device [15]. In a mixing quad, the appropriate emitter length is then related to the tail current of the Gilbert multiplier as

$$l_e = \frac{I_{\text{TAIL}}}{3J_{\text{Pf}T}w_e}.$$

(17)

Here, the peak- $f_T$  current density  $(J_{\rm P}f_T=7~{\rm mA}/\mu{\rm m}^2)$  of the SiGe HBT is technology dependent.

The frequency-dependent voltage conversion gain of the inductively-peaked mixer is given by

$$A_C = -\frac{2}{\pi} g_{m,M1} \frac{R_L + j\omega_{\text{OUT}} L_p}{(j\omega_{\text{OUT}})^2 L_p C_L + j\omega_{\text{OUT}} R_L C_L + 1}$$

(18)

where the load capacitance  $C_L$  includes the transistor output capacitance and external loading. The peaking inductance  $L_P$  can be chosen to give maximum bandwidth extension [16]

$$L_P = \frac{R_L^2 C_L}{\sqrt{2}}. (19)$$

It is noted that this choice of  $L_P$  will result in gain peaking. While the mixer is broad-band in the sense that it can operate as an upconverter or downconverter from dc to 50 GHz, the input and output signals are relatively narrow-band (less than  $10~\rm GHz$ ) and the peaking in frequency response can be tolerated as long as the signal bandwidth is within the 3-dB bandwidth of the mixer. Inductively peaking the output node allows for bandwidth extension without increasing power consumption.

Expounding on the novel BiCMOS cascode topology, a differential output driver (Fig. 18) has been designed to have 50-GHz bandwidth while driving an external  $50-\Omega$  load. Although originally intended as an output driver in broad-band serial communication circuits, the driver was applied to the mixer test circuit. The output swing can be adjusted by varying

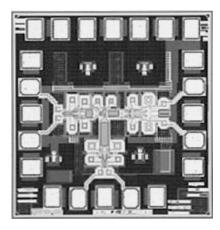

Fig. 19. Die photograph of the broad-band mixer with preamplifiers and output driver. The circuit employs 20 millimeter-wave inductors, each smaller than a  $55 \, \mu \, \text{m} \times 70 \, \mu \, \text{m}$  pad, and occupies a total area of  $720 \, \mu \, \text{m} \times 720 \, \mu \, \text{m}$ .

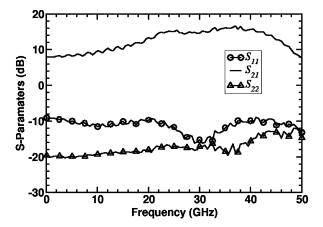

Fig. 20. Measured single-ended s-parameters of the mixer operating as an amplifier. The amplifier has 8 dB of gain at 50 GHz.

the bias current in the driver. Using a BiCMOS cascode as the first stage of the driver enables high bandwidth while operating from a lower supply voltage than can be attained in pure-bipolar topologies [13]. Furthermore, unlike the SiGe HBT, the MOSFET input capacitance is not strongly dependent on the bias point and, hence, the current can be widely varied without degrading bandwidth. The second stage requires a 50- $\Omega$  load resistance for broad-band output matching. This, along with the desired output swing, dictates the bias current in the second stage. To maximize output swing, a bipolar inverter output stage is used instead of a cascode. Resistive degeneration is employed to lessen the gain and input capacitance variation with bias current. Inductive peaking is added to the BiCMOS cascode inverter to improve its bandwidth. Additionally, shunt-series peaking at the output prevents the  $\sim$ 40-fF parasitic pad capacitance from limiting bandwidth [14].

As seen from the die photograph in Fig. 19, each of the 20 millimeter-wave inductors is smaller than a 55  $\mu$ m  $\times$  70  $\mu$ m bond pad. Despite the large number of inductors, the circuit occupies an area of only 720  $\mu$ m  $\times$  720  $\mu$ m, and is pad limited. The measured small-signal single-ended s-parameters of the mixer operating as an amplifier are illustrated in Fig. 20. Input and output return loss is better than -9 dB up to 50 GHz, and the single-ended gain is better than 8 dB over the measured range.

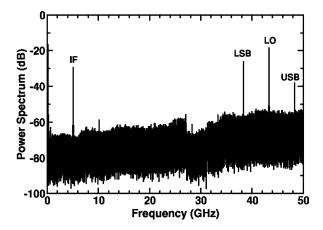

Fig. 21. Measured output spectrum of the mixer operating as an upconverter with -40-dBm 5-GHz IF input and 43-GHz LO. Cable and probe losses have not been deembedded.

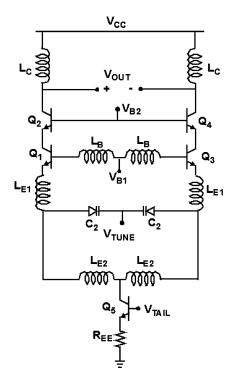

Fig. 22. Circuit schematic of 40-GHz Colpitts VCO. Inductors  $L_B,\,L_C$ , and  $L_{E2}$  are implemented with on-chip spiral inductors.

The measured output spectrum of the mixer working as an upconverter with a -40-dBm 5-GHz input signal and 43-GHz LO signal is shown in Fig. 21. As seen in Fig. 20, there is a 5-dB difference in measured gain between the lower sideband (LSB) frequency of 38 GHz and the upper sideband (USB) frequency of 48 GHz. This, combined with the additional 7 dB of cable and probe losses at 48 GHz, accounts for the higher spectral power observed in the LSB of Fig. 21. The mixer with input preamplifier, LO buffer, and output driver consumes 195 mW from a 2.5-V supply, including only 15 mW from the mixer core. Even though MOSFETs, with a lower  $f_T$  than either SiGe or InP HBTs, are used as transconductors in the Gilbert cell, the mixer still has higher bandwidth than the fastest reported dc-to-40-GHz InP HBT mixer and operates from a lower supply voltage [17].

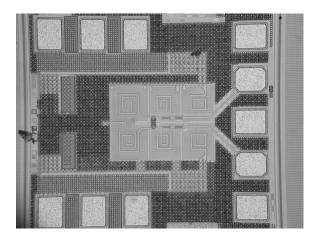

Fig. 23. Die photograph of the 40-GHz Colpitts VCO. The total chip area is 540  $\mu$ m  $\times$  490  $\mu$ m, and the VCO core occupies an area of 250  $\mu$ m  $\times$  180  $\mu$ m.

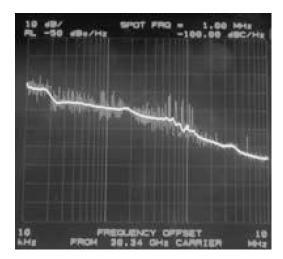

Fig. 24. On-wafer measured SSB phase noise of the 40-GHz VCO. The phase noise is -100.0 dBc/Hz at a 1-MHz offset.

# B. Millimeter-Wave VCO

A Colpitts VCO was also designed to prove the advantage of using inductors to reduce area and power dissipation while maintaining low phase noise. The schematic of a varactor-tuned Colpitts VCO is shown in Fig. 22. The differential 40-GHz VCO uses eight planar inductors, including tank inductor  $L_B$ , which has an ASITIC-predicted Q of 15 at 40 GHz. The addition of degeneration inductor  $L_{E1}$  reduces phase noise systematically by 3–4 dB [18]. Consequently, power consumption can be reduced if bias current is traded for inductance to achieve a target phase-noise specification. Inductor  $L_{E2}$  prevents the injection of high-frequency noise from current source  $Q_5$  into the tank, thus improving phase noise [19].

A die photograph of the VCO is shown in Fig. 23. It occupies an area of 540  $\mu$ m  $\times$  490  $\mu$ m, which is less than half the area of a similar 40-GHz VCO employing transmission-line resonators [2]. Moreover, the chip area is limited by the spacing between bias and high-frequency pads, which was dictated by the probes available for measurements. The VCO core area is only 250  $\mu$ m  $\times$  180  $\mu$ m. The measured single-sideband phase noise of -100.0 dBc/Hz at a 1-MHz offset from a 38-GHz fundamental (Fig. 24) is comparable to that achieved in transmission-

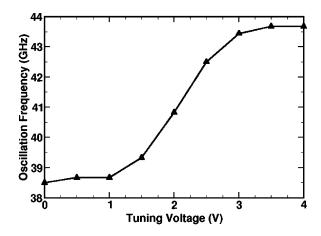

Fig. 25. Measured tuning range of the 40-GHz VCO. The oscillator is tunable over a 5-GHz band.

line based VCOs [2], [20]. Phase-noise measurements were performed on-wafer using standard power supplies. From circuit simulations, the expected phase noise was -101.0 dBc/Hz. The measured center frequency of 41 GHz is in excellent agreement with the value of 40.5 GHz predicted by SPECTRE simulations. The VCO has a 5-GHz tuning range, as seen in Fig. 25, with a VCO gain of 3 GHz/V. The tuning range is less than the expected 7-GHz value, and is attributed to the lower capacitance ratio of the MOS accumulation-mode varactor than that given by the model. The VCO delivers -1 dBm (including cable, probe, and dc blocking capacitor losses) to a 50- $\Omega$  load while consuming 85 mW from a 4.3-V supply. These results demonstrate that tuned circuits utilizing spiral inductors yield well-predicted behavior in the millimeter-wave regime without post-fabrication tuning, as in [2].

# VI. CONCLUSION

For the first time, inductors and transformers have been reported with adequate SRF for millimeter-wave applications in silicon-based integrated circuits. The inductor footprint must be minimized to obtain high SRF, making these inductors much more area efficient than transmission-line resonators for use in deep submicrometer technologies. A compact inductor model has been presented, along with a methodology for model extraction based on measured or simulated y-parameters. Their small size allows for the integration of a large number of millimeter-wave inductors to extend circuit bandwidth while reducing power dissipation and chip area. Measured results of the first dc-to-50-GHz broad-band mixer and 40-GHz VCO with integrated inductors demonstrate the applicability of spiral structures in the millimeter-wave range. The mixer operates over a wider frequency range than previously reported broad-band mixers while being biased from a lower supply voltage. Furthermore, the Gilbert cell employed in the broad-band mixer demonstrates for the first time the benefits of a true BiCMOS topology for high-linearity, low-noise, and low-power millimeter-wave circuits. Measured VCO results are comparable to those reported in transmission-line VCOs while occupying less chip area and requiring no post-fabrication tuning.

### ACKNOWLEDGMENT

The authors gratefully acknowledge the support of S. McDowall, B. Sautreuil, and STMircoelectronics, Crolles, France, for fabrication. The authors also extend special thanks to B. Prokes, STMicroelectronics, Ottawa, ON, Canada, for measurement assistance.

### REFERENCES

- S. Reynolds, B. Floyd, U. Pfeiffer, and T. Zwick, "60 GHz transceiver circuits in SiGe bipolar technology," in *Int. Solid-State Circuits Conf. Tech. Dig.*, Feb. 2004, pp. 442–443.

- [2] H. Li and H.-M. Rein, "Millimeter-wave VCOs with wide tuning range and low phase noise, fully integrated in a SiGe bipolar technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 2, pp. 184–191, Feb. 2003.

- [3] M. Meghelli, "A 108-Gb/s 4:1 multiplexer in 0.13 μm SiGe-bipolar technology," in *Int. Solid-State Circuits Conf. Tech. Dig.*, Feb. 2004, pp. 236–237.

- [4] T. O. Dickson, M.-A. LaCroix, S. Boret, D. Gloria, R. Beerkens, and S. P. Voinigescu, "Si-based inductors and transformers for 30–100 GHz applications," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Jun. 2004, pp. 205–208.

- [5] S. P. Voinigescu, D. Marchesan, J. L. Showell, M. C. Maliepaard, M. Cudnoch, M. G. M. Schumacher, M. Herod, D. J. Walkey, G. E. Babcock, P. Schvan, and R. A. Hadaway, "Process- and geometry-scalable bipolar transistor and transmission line models for Si and SiGe MMIC's in the 5–22 GHz range," in *Int. Electron Devices Meeting Tech. Dig.*, Dec. 1998, pp. 11.7.1–11.7.4.

- [6] Y. Cao, R. A. Groves, X. Huang, N. D. Zamdmer, J.-O. Plouchart, R. A. Wachnik, T.-J. King, and C. Hu, "Frequency-independent equivalent-circuit model for on-chip spiral inductors," *IEEE J. Solid-State Circuits*, vol. 38, no. 3, pp. 419–426, Mar. 2003.

- [7] M. Danesh, J. R. Long, R. A. Hadaway, and D. L. Harame, "A Q-factor enhancement technique for MMIC inductors," in *Proc. IEEE RFIC Symp.*, Apr. 1998, pp. 217–220.

[8] A. Niknejad, "ASITIC," Univ. California at Berkeley, Berkeley, CA,

- [8] A. Niknejad, "ASITIC," Univ. California at Berkeley, Berkeley, CA, 2002. [Online.] Available: http://rfic.eecs.berkeley.edu/~niknejad/asitic. html.

- [9] M. Laurens, B. Martinet, O. Kermarrec, Y. Campidelli, F. Deleglise, D. Dutartre, G. Troillard, D. Gloria, J. Bonnouvrier, R. Beerkens, V. Rousset, F. Leverd, A. Chantre, and A. Monroy, "A 150 GHz f<sub>T</sub>/f<sub>MAX</sub> 0.13 µm SiGe: C BiCMOS technology," in *Proc. IEEE Bipolar/BiCMOS Circuits Technology Meeting*, Sep. 2003, pp. 199–202.

- [10] R. B. Merrill, T. W. Lee, H. You, R. Rasmussen, and L. A. Moberly, "Optimization of high-Q inductors for multilevel metal CMOS," in *Int. Electron Devices Meeting Tech. Dig.*, Dec. 1995, pp. 38.7.1–38.7.4.

- [11] A. Zolfaghari, A. Chan, and B. Razavi, "Stacked inductors and transformers in CMOS technology," *IEEE J. Solid-State Circuits*, vol. 36, no. 4, pp. 620–628, Apr. 2001.

- [12] T. Suzuki, T. Takahashi, T. Hirose, and M. Takigawa, "A 80-Gbit/s D-type flip-flop circuit using InP HEMT technology," in *IEEE GaAs IC Tech. Symp. Dig.*, Nov. 2003, pp. 165–168.

- [13] T. O. Dickson, R. Beerkens, and S. P. Voinigescu, "A 2.5-V, 40-Gb/s decision circuit using SiGe BiCMOS logic," in *IEEE VLSI Circuits Symp. Dig.*, Jun. 2004, pp. 206–209.

- [14] S. P. Voinigescu, M. C. Maliepaard, J. L. Showell, G. E. Babcock, D. Marchesan, M. Schroter, P. Schvan, and D. L. Harame, "A scalable high-frequency noise model for bipolar transistors with application to optimal transistor sizing for low-noise amplifier design," *IEEE J. Solid-State Circuits*, vol. 32, no. 9, pp. 1430–1439, Sep. 1997.

- [15] S. P. Voinigescu, T. O. Dickson, R. Beerkens, I. Khalid, and P. Westergaard, "A comparison of Si CMOS, SiGe BiCMOS, and InP HBT technologies for high-speed and millimeter-wave ICs," in 5th Silicon Monolithic Integrated Circuits in RF Systems Topical Meeting, Sep. 2004, pp. 111–114.

- [16] T. H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits. Cambridge, U. K.: Cambridge Press, 1998.

- [17] K. W. Kobayashi, "A DC-40 GHz InP HBT Gilbert multiplier," in *IEEE GaAs Integrated Circuits Tech. Symp. Dig.*, Nov. 2003, pp. 251–254.

- [18] C. Lee, T. Yao, A. Mangan, K. Yau, M. A. Copeland, and S. P. Voinigescu, "SiGe BiCMOS 65-GHz BPSK transmitter and 30 to 122 GHz LC-varactor VCO's with up to 21% tuning range," in IEEE Compound Semiconductor IC Symp., Oct. 2004, pp. 179–182.

- [19] E. Hegazi, H. Sjoland, and A. A. Abidi, "A filter technique to lower LC oscillator phase noise," *IEEE J. Solid-State Circuits*, vol. 36, no. 12, pp. 1921–1930. Dec. 2001.

- [20] D. K. Shaeffer and S. Kudszus, "Performance-optimized microstrip coupled VCOs for 40-GHz and 43-GHz OC-768 optical transmission," *IEEE J. Solid-State Circuits*, vol. 38, no. 7, pp. 1130–1138, Jul. 2003.

**Timothy O. Dickson** (S'01) received the Bachelor of Science (with highest honors) and Master of Engineering degrees in electrical engineering from the University of Florida, Gainesville, in 1999 and 2002, respectively, and is currently working toward the Ph.D. degree at the University of Toronto, Toronto, ON, Canada.

From 2000 to 2002, he was a Graduate Research Assistant with the University of Florida, where he investigated isolation issues in RF and mixed-signal silicon-based technologies. He has held internships

in the area of analog and RF circuit design with Dallas Semiconductor (now Maxim) and Global Communication Devices. His research interests lie in the area of high-frequency integrated circuits for wireless and wireline communications.

Mr. Dickson was named an undergraduate University Scholar by the University of Florida in 1999. He was the recipient of the 2004 Best Paper Award presented at the Micronet Annual Workshop. He was a finalist in the Student Paper Competition at the IEEE Microwave Theory and Techniques Society (IEEE MTT-S) International Microwave Symposium (IMS). He holds a University of Toronto Doctoral Fellowship and is an Edward S. Rogers Sr. Scholar.

Marc-Andre LaCroix (S'97–M'02) received the Bachelor of Science degree in engineering from the University of New-Brunswick, Fredericton, NB, Canada, in 2000, and the Master of applied science degree in electrical engineering from Carleton University, Ottawa, ON, Canada, in 2002.

From 2000 to 2002, he was a Resident Researcher with STMicroelectronics, Ottawa, ON, Canada, during which time he developed millimeter-wave passive device models for silicon-based technologies. He is currently a Circuit Design Engineer

with STMicroelectronics, where he develops millimeter-wave wireless and broad-band wireline integrated circuits in state-of-the-art Si(Ge)-BiCMOS processes.

**Samuel Boret** was born in Malo-les-Bains, France, on December 23, 1972. He received the Ph.D. degree from the University of Lille, Lille, France, in 1999.

In 1996, he joined the Centre Hyperfréquences et Semiconducteurs, University of Lille. As part of his graduate studies, he was involved with monolithic integrated circuits in coplanar technology for applications of reception up to 110 GHz. He is currently with Central Research and Development, RF Electrical Characterization Group, STMicroelectronics, Crolles, France. His main interests include design,

characterization and modeling of RF devices in advanced silicon technologies.

Daniel Gloria received the Engineering degree in electronics from the École Nationale Supérieure d'Electronique et de Radioélectricité, Bordeaux, France, in 1995, and the M.S.E.E. degree in optics, optoelectronics, and microwaves design systems from the National Polytechnical Institute of Grenoble (INPG), Grenoble, France.

From 1995 to 1997, he was an RF Designer Engineer with ALCATEL Bell Network System Laboratories, Charleroi, Belgium, during which time he was involved in the development of the cable-phone RF

front-end and its integration in hybrid-fiber-coax telecommunication networks. Since 1997, he has been with Central Research and Development, STMicroelectronics, Crolles, France, as a High Frequency (HF) Research Engineer. His interests are in optimization of active and passive devices for high-frequency applications in BiCMOS and CMOS advanced technologies.

**Rudy Beerkens** (M'91) received the B.Sc. degree in electrical engineering from the University of Waterloo, Waterloo, ON, Canada, in 1986.

From 1986 to 2000, he was with Nortel Networks, during which time he was involved in the areas of semiconductor manufacturing, BiCMOS process development, yield enhancement, device characterization, and reliability. In 2000, he joined STMicroelectronics, Ottawa, ON, Canada, where he currently heads an integrated-circuits design team. His scientific interests include high-speed,

broad-band, and millimeter-wave integrated circuits.

**Sorin P. Voinigescu** (S'92–M'91–SM'02) received the M.Sc. degree in electronics from the Polytechnic Institute of Bucharest, Bucharest, Romania, in 1984, and the Ph.D. degree in electrical and computer engineering from the University of Toronto, Toronto, ON, Canada, in 1994.

From 1984 to 1991, he was involved with research and development and with academia in Bucharest, Romania, where he designed and lectured on microwave semiconductor devices and integrated circuits. From 1994 to 2000, he was with Nortel

Networks, Ottawa, ON, Canada, where he was responsible for projects in high-frequency characterization and statistical scalable compact model development for Si, SiGe, and III-V heterostructure devices. He led the modeling infrastructure development for, and was involved in the prototyping of, wireless and broad-band fiber-optics transceivers in emerging semiconductor technologies. In April 2000, he cofounded Quake Technologies, Ottawa, ON, Canada, a fabless semiconductor company that focuses on the design and fabrication of 10- and 40-Gb/s physical layer integrated circuits. In September 2002, he joined the Department of Electrical and Computer Engineering, University of Toronto, as an Associate Professor. He has authored or coauthored over 40 refereed and invited technical papers spanning the simulation, modeling, design, and fabrication of GaAs-, InP-, and Si-based heterostructure devices and circuits. He holds two U.S. patents in these areas. His research and teaching interests focus on the modeling and characterization of very deep-submicrometer semiconductor devices and on novel design techniques and low-voltage low-power topologies for wireless, optical fiber, and wireline data communication physical layer integrated circuits in the 10-100-GHz range.

Dr. Voinigescu is a member of the Technical Program Committee of the IEEE Compound Semiconductor Integrated Circuit Symposium. He was a corecipient of the Best Paper Award presented at the 2001 IEEE Custom Integrated Circuits Conference.