Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

Your Me. Votre reference

Our life Notice reference

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# VLSI Compatible Si/SiGe/Si p-MOSFET's

by

Petre Sorin Voinigescu

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy

Graduate Department of Electrical and Computer Engineering

University of Toronto

© Copyright by Petre Sorin Voinigescu 1994

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontano K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file - Votre reference

Our file. Notice reference

THE AUTHOR HAS GRANTED AN IRREVOCABLE NON-EXCLUSIVE LICENCE ALLOWING THE NATIONAL LIBRARY OF CANADA TO REPRODUCE, LOAN, DISTRIBUTE OR SELL COPIES OF HIS HER THES IS BY ANY MEANS AND IN ANY FORM OR FORMAT, MAKING THIS THESIS AVAILABLE TO INTERESTED PERSONS.

L'AUTEUR A ACCORDE UNE LICENCE IRREVOCABLE ET NON EXCLUSIVE PERMETTANT A LA BIBLIOTHEQUE NATIONALE DU CANADA DE REPRODUIRE, PRETER. DISTRIBUER OU VENDRE DES COPIES DE SA THESE L'E QUELQUE MANIERE ET SOUS QUELQUE FORME QUE CE SOIT POUR METTRE DES EXEMPLAIRES DE CETTE THESE A LA DISPOSITION DES PERSONNE INTERESSEES.

THE AUTHOR RETAINS OWNERSHIP OF THE COPYRIGHT IN HIS/HER THESIS. NEITHER THE THESIS NOR SUBSTANTIAL EXTRACTS FROM IT MAY BE PRINTED OR OTHERWISE REPRODUCED WITHOUT HIS/HER PERMISSION

L'AUTEUR CONSERVE LA PROPRIETE DU DROIT D'AUTEUR QUI PROTEGE SA THESE. NI LA THESE NI DES EXTRAITS SUBSTANTIELS DE CELLE-CI NE DOIVENT ETRE IMPRIMES OU AUTREMENT REPRODUITS SANS SON AUTORISATION.

ISBN 0-612-02935-2

| Name         | SORIN                 | PETRE               | VOINIGESCU                                                                  | _                                                               |     |

|--------------|-----------------------|---------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------|-----|

| Dissertation | Abstracts Internation | al is arranged by b | road, general subject categories. Pl<br>er the corresponding four digit cod | lease select the one subject which most in the spaces provided. | ł   |

| •            | cybonics &            |                     |                                                                             | 0544                                                            | J·N |

| <u> </u>     |                       |                     | CT TERM                                                                     | SULLECT CODE                                                    |     |

#### **Subject Categories**

# THE HUMANITIES AND SOCIAL SCIENCES

| COMMUNICATIONS AND TH       | E ARTS       | Psychology                  | .0525  |

|-----------------------------|--------------|-----------------------------|--------|

| Architecture                | 0727         | Reading                     | .0535  |

| Art History                 | 0377         | Reading<br>Religious        | .0527  |

| Cinema                      | .0900        | Sciences                    | .0/14  |

| Dance                       | .0378        | Swrondarv                   | 0233   |

| Fine Arts                   | 0357         | Sacial Sciences             | .032~  |

| Information Science         | 0723         | Sacialary as                | L.:4L  |

| Journalism                  | 0391         | perio                       | ::529  |

| Library Science             | 0399         | leacher Iraining            | 2220   |

| Mass Communications         | 0708         | technology                  |        |

| Music                       | 0413         | Tests and Measurements      | .0288  |

| Speech Communication        | 0459         | Vocational                  | 0747   |

| Theater                     | 3465         |                             |        |

| (Higgsig)                   |              | LANGUAGE, LITERATURE AND    |        |

| EDUCATION                   |              | LINGUISTICS                 |        |

| General                     | 0515         |                             |        |

| Administration              | 0414         | Language                    | 2679   |

| Adult and Continuing        | 05 6         | General<br>Ancient          | ==     |

| Agricultural                | 0517         |                             | 0290   |

| Art                         | 3273         | Linguishes                  | 0291   |

| Bilingual and Multicultural | 0282         | Modern                      | 0271   |

| Business                    | 3688         | Literature                  | 0.401  |

| Community College           | 0275         | General                     | 0504   |

| Curriculum and Instruction  | 0727         | Clossical                   | 3205   |

| Early Childhood             | 0519         | Comparative                 | 0297   |

|                             | 0524         | Medieval                    |        |

| Elementary<br>Finance       | 0277         |                             | 0278   |

| Tire and Counseling         | 0519         |                             | 0316   |

|                             | 0580         | American                    | 3591   |

| The MACHINE CONTRACTOR      | 0745         | Asian<br>Canadian (English) | 0303   |

|                             | 0520         | Canadian (English)          | .0352  |

| t ary of                    | 9278         | Canadicm (French)           | 0323   |

| Hume Economics              | 0:21         | English                     | 0593   |

| Industrial                  | 02/9         | Germanic                    | 0311   |

| Language and Literature     | 028C         | Latin American              | 0312   |

|                             | 028C<br>0522 | Middle Eastern              | . 0315 |

| Music                       | 0998         | Romance                     | 0: 3   |

| Philosophy c'               |              | Slavic and East Europerin   | 0314   |

| Physical                    | 0523         | ·                           |        |

|                             |              |                             |        |

| PHELOSOPHY, RELIGION AND THEOLOGY             |              |

|-----------------------------------------------|--------------|

| Philosophy                                    | 0422         |

| Religion                                      | -422         |

| Rengion                                       | 0318         |

| General<br>Biblical Studies                   | 6321         |

| Ciergy                                        | 11.11.       |

| Clergy History of Philosophy of               | 052C         |

| Philosophy of                                 | 0322         |

| Philosophy of<br>Theology                     | 0469         |

|                                               |              |

| SOCIAL SCIENCES                               |              |

| American Studies                              | 0323         |

| Anthropology Archaeology                      |              |

| Archaeology                                   | 0324         |

| Cuitural                                      |              |

| Cultural<br>Physical                          | 0327         |

|                                               |              |

| General                                       | 0310         |

| Accounting                                    | .0272        |

| Banking Management Marketing Canadian Studies | 0770         |

| Management                                    | .0434        |

| Marketing                                     | .0238        |

| Canadian Studies                              | . 0385       |

| Economics                                     | 0501         |

| General<br>Agricultural                       |              |

| Agricultural                                  |              |

| Commerce-Business                             | . 0505       |

| Firance                                       | 050J<br>05C9 |

| History                                       | 0307         |

| abor<br>Theory                                | 25.0         |

| heory                                         | 0358         |

|                                               |              |

| Gergraphy                                     | 0366         |

| Gerontology                                   | . 0337       |

| history<br>General                            | 0578         |

| General                                       | 05/0         |

|                                               |              |

| Ancient Medieval Modern Black African Asia, Australia and Ocennia Canadian European Latin American Midd'e Eastern United States History of Science Law | 0581<br>0582<br>0328<br>0331<br>0332<br>0334<br>0335<br>0336<br>0333<br>0585 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Political Science                                                                                                                                      |                                                                              |

| General<br>Intra ational Law and                                                                                                                       | .0615                                                                        |

| relations Public Administration Recreation Social Work                                                                                                 | 0616<br>0617<br>0814                                                         |

| Sociology General Criminology and Penalogy Demography Ethnir and Racial Studies                                                                        | 0626<br>0627<br>0938<br>0631                                                 |

| Individual and Family Studies                                                                                                                          | 0628                                                                         |

| Industrial and Labor Relations Public and Social Welfare Social Structure and                                                                          | .0629<br>.0630                                                               |

| Des Sapment Theory and Methods Transportation Uroan and Regional Plauning Warrer, Studies                                                              | 0999                                                                         |

|                                                                                                                                                        |                                                                              |

## THE SCIENCES AND ENGINEERING

| BIOLOGICAL SCIENCES Agriculture              |              |

|----------------------------------------------|--------------|

| General                                      | 0473         |

| Agronomy                                     | 0285         |

| Animal Culture and                           |              |

| Nisition                                     | 0475         |

| Animal Pathology                             | 0476         |

| Food Science and                             |              |

| Technology                                   | 0359         |

| Factorology Face try and Wiltlife            | C478         |

| Proticulture                                 | 0479         |

| Plane Patholism                              | 0480         |

| Plant Plysiology                             | 0812         |

| ana. Vanagement                              | 0777         |

| Plant Physiology sings Management richnology | 0746         |

|                                              |              |

| erol                                         | 0306         |

| · yomy                                       | 0297         |

| Biostatistics                                | 0308         |

| Botany                                       | 0309         |

| Çell                                         | 0379         |

| Ecology                                      | 0329         |

| Entomology                                   | 0353<br>0369 |

| Genetics                                     | 0369         |

| Genetics<br>Limnology<br>Microbiology        | 0793         |

| Microb ology                                 | .0410        |

| Molari ar                                    | 0307         |

| Neuro, ince                                  | 0317         |

| Oceanography                                 | 0416         |

| Physiology<br>Radiation                      | 0433         |

| Radiation                                    | .0821        |

| Veterinary science                           |              |

| Zoulogy                                      | 0472         |

| Biophysics                                   |              |

| General                                      |              |

| Medical                                      | 0760         |

| EARTH SCIENCES Biogeochemistry Geochemistry  | 0425         |

| Occidentistry                                | 0770         |

| Gcodesy Geology Geophysics Hydrology Minerclogy Pales: bology Pales: bology Pales: cology Pales: rology Paricusuringy Paryrology 7. hydrol Geography Physical Geography Physical Oceanography | 0373<br>0388<br>0411<br>0345<br>0426<br>0418<br>0985 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| HEALTH AND ENVIRONMENTAL SCIENCES                                                                                                                                                             | L                                                    |

| 2,111,911,101,101                                                                                                                                                                             | 0768                                                 |

| Health Sciences General                                                                                                                                                                       | 0566                                                 |

| YI'H AND FNAIKONWENIYI                            | •     |

|---------------------------------------------------|-------|

| IENCES                                            |       |

| vironmental Sciences                              | 0768  |

| alth Sciences                                     |       |

| General                                           | 0566  |

| Audiology                                         | 0300  |

| Audiology<br>Chemotherapy                         | 0992  |

| Pentisiry                                         | 0567  |

| Education                                         | 0350  |

| Hospital Management                               | 0769  |

| Human Development                                 | 0758  |

| Immunology                                        | 0982  |

| Medicine and Surgery                              | 0564  |

| Mental Health                                     | 0347  |

| Nursing                                           | 0569  |

| Nutrition                                         | 0.570 |

| Chatetries and Gynecology                         | 0380  |

| Obstetrics and Gynecology Occupans nal Health and |       |

| Therapy                                           | .0354 |

| Ophthalmology                                     | .0381 |

| Pathology                                         | .0571 |

| Pharmacology                                      | .0419 |

| Pharmacy                                          | .05/2 |

| Physical Therapy                                  | .0382 |

| Public Health                                     | .0573 |

| Speech Fathology                                            | 0383  |

|-------------------------------------------------------------|-------|

| Toxicalogy<br>lone Economics                                | .0383 |

| HYSICAL SCIENCES                                            |       |

| ure Sciences                                                |       |

| hemistry                                                    | 3405  |

| General                                                     | 0485  |

| Agricultural                                                | 0/47  |

| Analytical                                                  | 0407  |

| Biochemistry                                                | 0407  |

| Nuclear                                                     | 077-0 |

| Nuclear                                                     | 0.400 |

| Organic<br>Pharmaceutical                                   | 0470  |

| nt                                                          | 0404  |

| Physical<br>Polymer                                         | 0405  |

| rolymer                                                     | 0754  |

| Radiation Authematics                                       | 0405  |

|                                                             | 0405  |

| hysics<br>General                                           | 0405  |

| General                                                     | 000J  |

| Acoustics                                                   | 0700  |

| Astronon y and<br>Astrophysics                              | OAOA  |

| Astrophysics                                                | 0408  |

| Atmospheric Science                                         | 0748  |

| Atomic Electronics and Electricity Elementary Particles and | 0402  |

| Elements and Electricity                                    | 000/  |

| High Energy                                                 | 0708  |

| Fluid and Plasma                                            | 0759  |

| Mclecular                                                   | 0409  |

| Nuclear                                                     | 0410  |

| Optics                                                      | 0752  |

| Rodigtion                                                   | 0756  |

| Solid State                                                 | 0611  |

| itaristics                                                  | 0463  |

|                                                             |       |

| Applied Sciences                                            | 00.44 |

| Appliec' Mechanics                                          | 0346  |

| Computer Science                                            | U984  |

| Engineering<br>General                                                                                | . 0537  |

|-------------------------------------------------------------------------------------------------------|---------|

|                                                                                                       | 0538    |

| Agricultural                                                                                          | 0539    |

| Automotive<br>Biomedical                                                                              | 0540    |

| Chemical                                                                                              | 1)542   |

| Ciul                                                                                                  | 0543    |

| Civil<br>Electronics and Electrical                                                                   | 0544    |

| Heat and The modynamics.                                                                              | 0348    |

| Hydraulic                                                                                             | .0545   |

| Industria!                                                                                            | 9546    |

| Marine                                                                                                | 0547    |

| Majerials Science                                                                                     | ., 0/94 |

| Mechanical                                                                                            | 0548    |

| Metallurgy                                                                                            | 0743    |

| Mining                                                                                                | 0551    |

| Nuclear                                                                                               |         |

| Packaging                                                                                             | 0347    |

| Petroleum Sanitary and Municipal System Science Geotechnology Operations Research Plastics Technology | 0554    |

| System Science                                                                                        | 0790    |

| Geotechnology                                                                                         | 0428    |

| Operations Research                                                                                   | 0796    |

| Plastics Technology                                                                                   | 0795    |

| Textile Technology                                                                                    | 0994    |

| PSYCHOLOGY                                                                                            |         |

| General                                                                                               | 0621    |

| Behavioral                                                                                            |         |

| Clinical                                                                                              |         |

| Developmental                                                                                         | 0620    |

| Experimental                                                                                          | 0023    |

| Indestrial                                                                                            | 0425    |

| PersonralityPhysiological                                                                             | 0023    |

| Psychobiology                                                                                         | 0349    |

| Psychometrics                                                                                         | 0632    |

| 375.7011001102                                                                                        |         |

# THE UNIVERSITY OF TORONTO LIBRARY MANUSCRIPT THESIS - DOCTORAL AUTHORITY TO DISTRIBUTE

| NOT         | E: The AUTHOR will sign in there be NO RESTRICTI cases. | one of the two places indicated.<br>ON on the distribution of the pub                                        | It is the intention of the University that lication of theses save in exceptional |

|-------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| (a)         | Immediate publication in                                | microform by the National Library                                                                            | y is authorized.                                                                  |

|             | Author's signature                                      | . A                                                                                                          | _ Date October 7 199                                                              |

|             |                                                         | - OR -                                                                                                       |                                                                                   |

| (b)         | (normal maximum delay is                                | al Library is to be postponed until<br>s two years). Meanwhile this the<br>itten permission on each occasion | Sts may not be consulted in the Univer                                            |

|             | Author's signature                                      |                                                                                                              | Date                                                                              |

| This r      |                                                         | asons which seem to me, as Ch                                                                                | air of the Graduate Department of                                                 |

| Signat      | lure of Graduate Departmen                              | l Chair                                                                                                      |                                                                                   |

| ne au       | thor it it is proposed to make                          | roper credit for any use made of<br>extensive quotations, or to repre                                        | the thesis, and to obtain the consent of oduce the thesis in whole or in part.    |

|             | Signature of borrower                                   | Address                                                                                                      | Date                                                                              |

|             |                                                         |                                                                                                              |                                                                                   |

| •           |                                                         |                                                                                                              |                                                                                   |

|             |                                                         |                                                                                                              |                                                                                   |

| <del></del> |                                                         |                                                                                                              |                                                                                   |

|             | •                                                       |                                                                                                              |                                                                                   |

|             |                                                         |                                                                                                              |                                                                                   |

|             |                                                         |                                                                                                              |                                                                                   |

|             |                                                         |                                                                                                              |                                                                                   |

|             |                                                         |                                                                                                              |                                                                                   |

# VLSI Compatible Si/SiGe/Si p-MOSFET's

by

Sorin Petre Voinigescu

**University of Toronto**

Copyright by Sorin Petre Voinigescu 1994

# VLSI Compatible Si/SiGe/Si p-MOSFET's Doctor of Philosophy Degree, 1994

#### Petre Sorin Voinigescu

# Graduate Department of Electrical and Computer Engineering University of Toronto

#### ABSTRACT

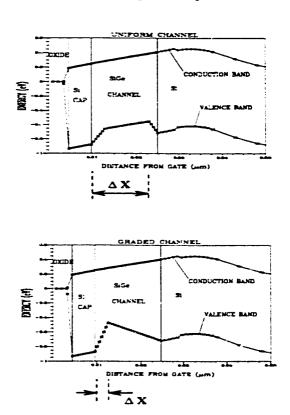

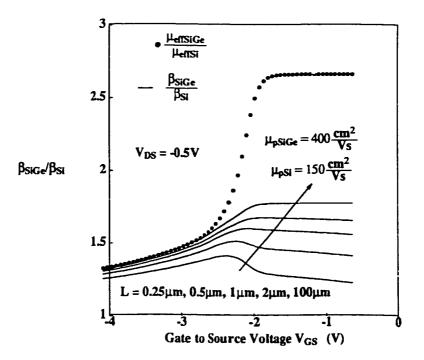

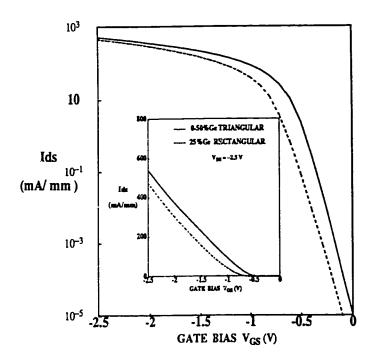

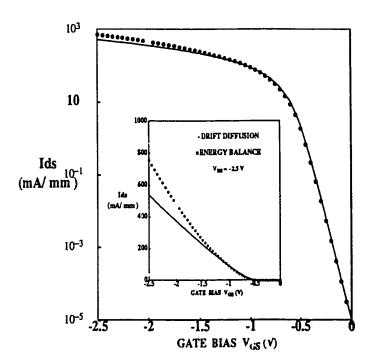

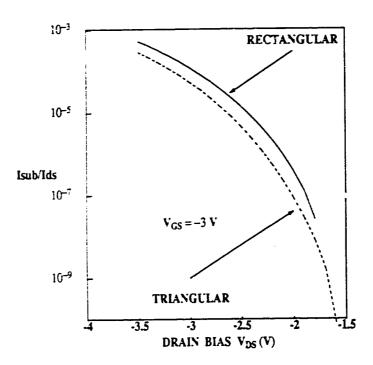

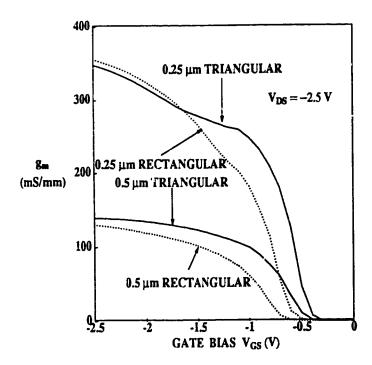

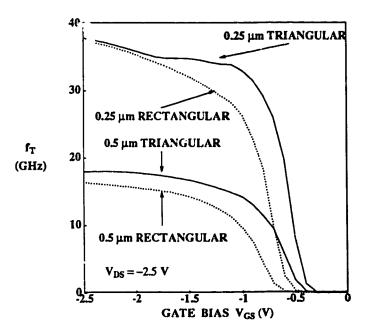

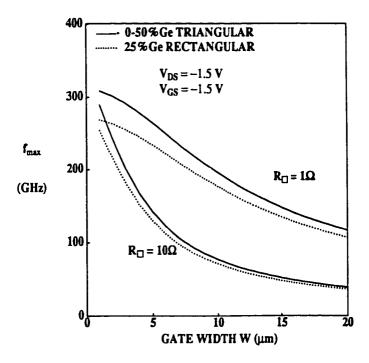

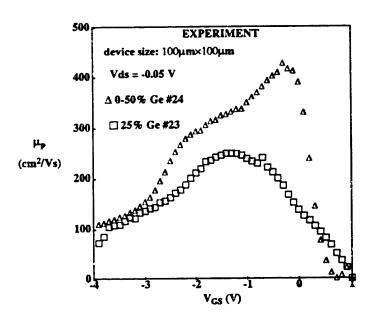

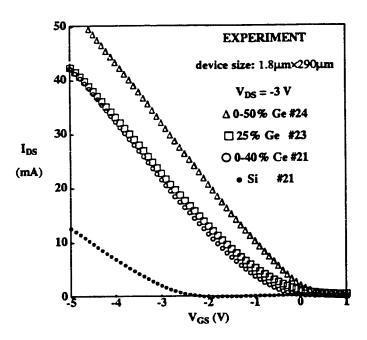

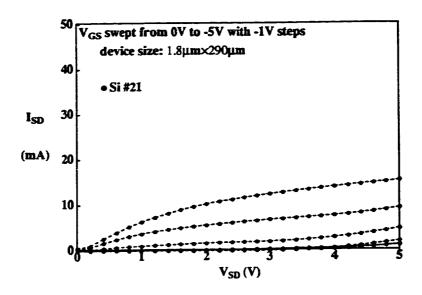

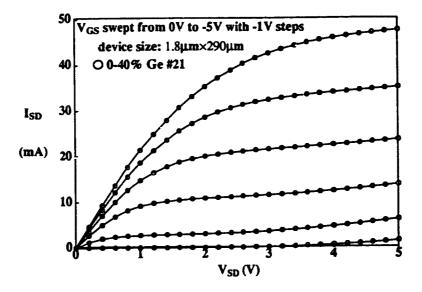

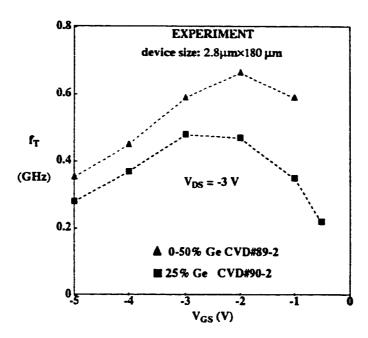

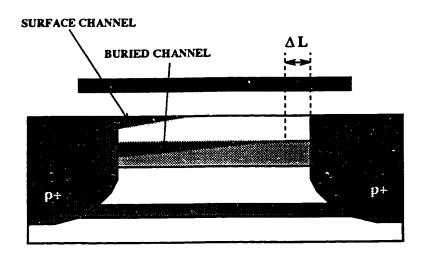

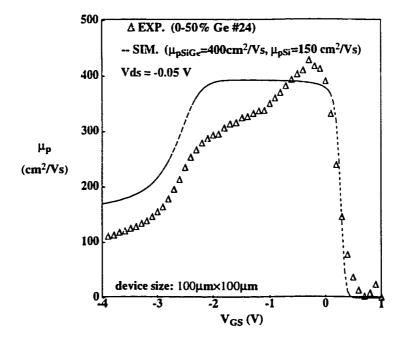

Silicon-Germanium (SiGe) has emerged as a promising vehicle for expanding the performance bounds of silicon-based VLSI technology. Attempts are now underway worldwide to demonstrate that SiGe field effect transistors can reach industrial maturity. In particular, SiGe p-MOSFET's require the most urgent attention because of the poor performance of silicon pchannel devices. A novel Si/SiGe/Si p-MOSFET structure is proposed here, whereby the effective hole mobility is maximized by employing a buried SiGe channel with triangular Ge profiles. The benefits of the triangular Ge channel, in comparison with the established rectangular Ge channel profile, were demonstrated both theoretically and experimentally. The SiGe p-MOSFET's were implemented in-house, in a VLSI compatible process that allowed for the integration of silicon and SiGe p-MOSFET's on the same chip. Hole mobilities of 400 cm<sup>2</sup>/Vs and 250 cm<sup>2</sup>/Vs were measured for devices with 0-50% Ge triangular and 25% Ge rectangular channels, respectively. A factor of two improvement in transconductance with respect to the equivalent, on-chip silicon p-MOSFET was obtained. When compared to rectangular Ge profile devices, the MOSFET's with triangular Ge channel profiles demonstrated 30-40% improvement in mobility, transconductance and cutoff frequency. New methods to characterize the band offset and doping concentration in Si/SiGe layers, as well as the mobility profiles inside the channel, were also developed and validated experimentally.

## **ACKNOWLEDGMENTS**

I would like to thank Prof. C.A.T. Salama for his support throughout this work. His guidance and advice have had a major impact on the final outcome of the thesis. Prof. Kris Iniewski's contribution through helpful and friendly discussions on numerous theoretical aspects involving Si and SiGe MOSFET's is greatly appreciated. I would also like to acknowledge the advice on processing and layout issues that I have received from Dr. Ralph Lisak. Thanks are also due to my former and future colleague and friend Mark Schumacher. His experience with Si/SiGe HBT processing has spared me many a trial run.

I would also like to acknowledge several external collaborators without whose contribution this work would not have been possible. These are Dr. Derek C. Houghton and Dr. Jean-Pierre Noël from the National Research Council of Canada, Ottawa, who have been kind enough to grow the MBE Si/SiGe layers, and Dr. Theodore I. Kamins of Hewlett-Packard Laboratories, Palo Alto, Ca., whom I have never met in person, but who presented me with the gift of CVD grown Si/SiGe wafers. My thanks also go to Dr. Peter B. Rabkin of Silvaco International, Santa Clara, Ca., who has provided us with free copies of the first commercial two-dimensional heterostructure device simulator. Without his help and prompt advice the Si/SiGe/Si p-MOSFET's discussed in this thesis would have taken much longer to understand and design.

I would like to thank Jaro Pristupa and Dana Reem for being there whenever I needed their help (and that was not infrequent, I may add), as well as the students and staff in the Integrated Circuits Lab at the University of Toronto for creating an excellent working environment.

This work was supported by the Natural Sciences and Engineering Research Council, Micronet, Northern Telecom, National Research Council of Canada, Hewlett Packard and Silvaco International.

Last, and not least, I thank my family for having endured through it all.

## **Table of Contents**

| CHAPTER 1: INTRODUCTION                                                 | 1.1  |

|-------------------------------------------------------------------------|------|

| 1.1. Why Silicon-Germanium ?                                            | 1.1  |

| 1.2. Silicon-Germanium Material Properties                              | 1.3  |

| 1.2.1. Lattice Constant and Film Growth                                 | 1.3  |

| 1.2.2. Bandgap                                                          | 1.6  |

| 1.2.3. Carrier Transport in Silicon-Germanium Alloys                    | 1.7  |

| 1.3. Silicon-Germanium Devices                                          | 1.8  |

| 1.4. Why Si/SiGe/Si p-MOSFET's?                                         | 1.10 |

| 1.5. Thesis Objectives and Outline                                      | 1.11 |

| References                                                              | 1.12 |

| CHAPTER 2: THE HETEROSTRUCTURE MOS CAPACITOR                            | 2.1  |

| 2.1. Introduction                                                       | 2.1  |

| 2.2. Physics of Heterostructure MOS Capacitors                          | 2.3  |

| 2.2.1. Charge Distribution and Threshold Voltages                       | 2.5  |

| 2.2.2. Capacitance-Voltage Characteristics                              | 2.15 |

| 2.3. The Si/SiGe MOS Capacitor as a Process and Device Characterization |      |

| Vehicle                                                                 | 2.17 |

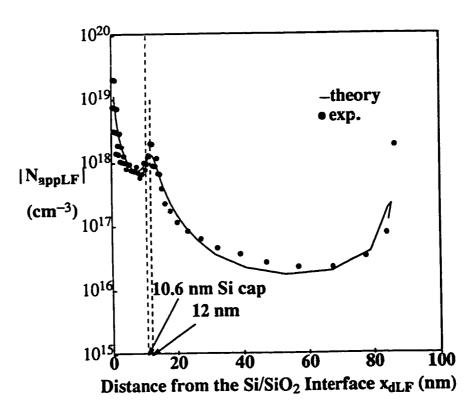

| 2.3.1. Apparent Doping Profiles and Extraction of the Silicon Cap |      |  |  |

|-------------------------------------------------------------------|------|--|--|

| Thickness                                                         | 2.18 |  |  |

| 2.3.2. Calculation of the Valence Band Offset                     | 2.21 |  |  |

| 2.3.3. Sources of Error Affecting the Valence Band Offset         | 2.22 |  |  |

| 2.3.4. Proposed Characterization Technique                        | 2.25 |  |  |

| 2.3.5. Experimental Results                                       | 2.26 |  |  |

| 2.4. Conclusions                                                  | 2.32 |  |  |

| References                                                        | 2.33 |  |  |

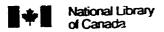

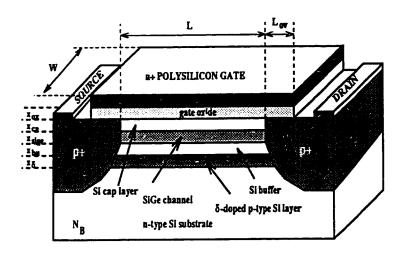

| CHAPTER 3: THE Si/SiGe/Si p-MOSFET                                | 3.1  |  |  |

| 3.1. Introduction                                                 | 3.1  |  |  |

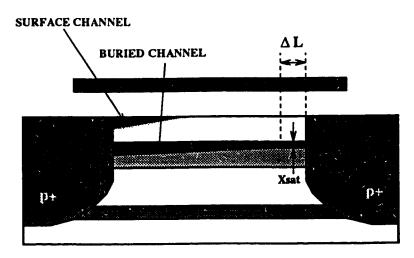

| 3.2. Basic Concept and Proposed Structure                         | 3.2  |  |  |

| 3.3. Si/SiGe/Si p-MOSFET Model                                    | 3.7  |  |  |

| 3.3.1. Threshold Voltage and Body Effect                          | 3.7  |  |  |

| 3.3.2. Threshold Voltage Roll-Off                                 | 3.9  |  |  |

| 3.3.3. I-V Characteristics                                        | 3.11 |  |  |

| 3.3.4. Hot Carrice Effects                                        | 3.17 |  |  |

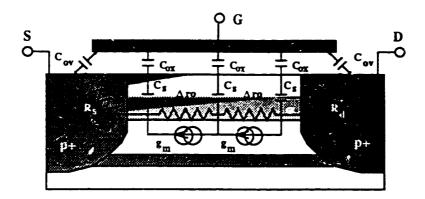

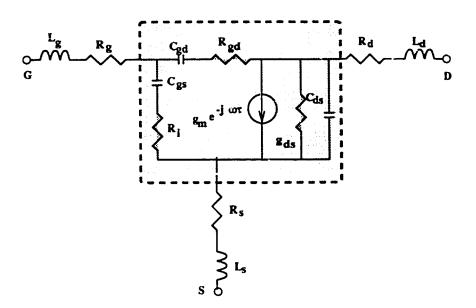

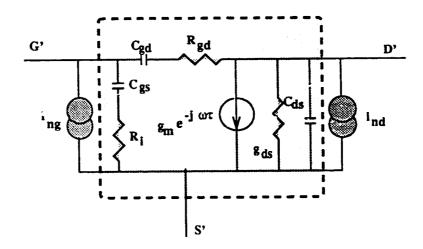

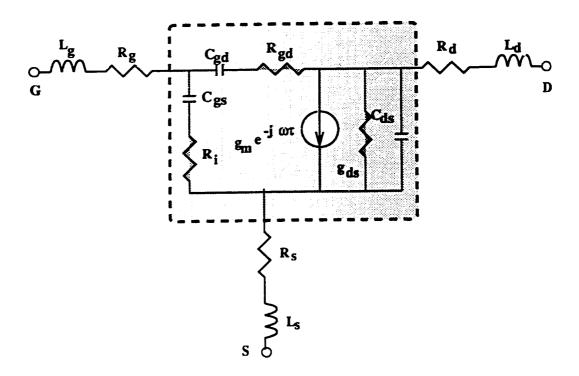

| 3.3.5. Small Signal Equivalent Circuit                            | 3.20 |  |  |

| 3.3.6. High Frequency Performance                                 | 3.25 |  |  |

| 3.3.7. Noise Performance                                          | 3.29 |  |  |

| 3.4. Si/SiGe/Si p-MOSFET Design Methodology                       | 3.31 |  |  |

| 3.4.1. Guidelines for Vertical Layer Structure Design | 3.32 |

|-------------------------------------------------------|------|

| 3.4.2. Guidelines for Layout Geometry Design          | 3.34 |

| 3.5. Si/SiGe/Si p-MOSFET Scaling                      | 3.32 |

| 3.5.1. Scaling Rules                                  | 3.35 |

| 3.5.2. Scaling Rules Verification by Simulation       | 3.37 |

| 3.6. Conclusions                                      | 3.41 |

| References                                            | 3.44 |

| CHAPTER 4: Si/SiGe/Si p-MOSFET FABRICATION AND CHAR-  |      |

| ACTERIZATION                                          | 4.1  |

| 4.1. Introduction                                     | 4.1  |

| 4.2. MBE and CVD Process Description                  | 4.2  |

| 4.2.1. MBE Wafers                                     | 4.2  |

| 4.2.2. CVD Wafers                                     | 4.5  |

| 4.2.3. Critical Processing Steps                      | 4.6  |

| 4.3. Test Chip Description                            | 4.6  |

| 4.4. Process Characterization                         | 4.8  |

| 4.5. Device Characterization                          | 4.11 |

| 4.5.1. C-V Characteristics and Mobility Profiling     | 4.11 |

| 4.5.2. Current Voltage Characteristics                | 4.15 |

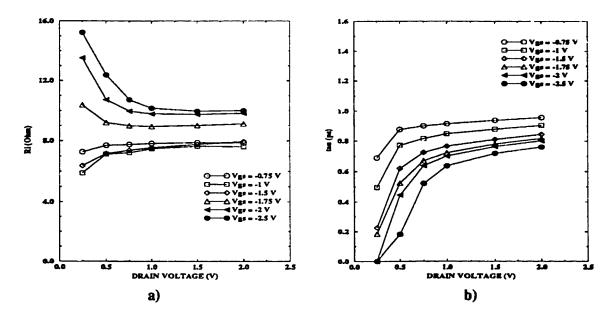

| 4.5.3. Transconductance and Output Conductance        | 4.18 |

| 4.5.4. High Frequency Characteristics                  | 4.20         |

|--------------------------------------------------------|--------------|

| 4.6. Conclusion                                        | 4.23         |

| References                                             | 4.24         |

| CHAPTER 5: CONCLUSIONS                                 | 5.1          |

| 5.1. Thesis Summary                                    | 5.1          |

| 5.2. Thesis Contributions                              | 5.2          |

| 5.3. Suggestions for Future Work                       | 5.3          |

| APPENDIX A: ANALYTICAL SOLUTION TO POISSON'S EQUA-     |              |

| TION                                                   | <b>A.</b> 1  |

| APPENDIX B: 1D SELF-CONSISTENT SCHRODINGER AND POIS-   |              |

| SON EQUATION SOLVER                                    | B.1          |

| APPENDIX C: ANALYTICAL MODEL FOR Si/SiGe/Si p-MOSFET's |              |

| C.1 Threshold Voltage and Body Effect                  | <b>C</b> .1  |

| C.2 I-V Characteristics                                | C.2          |

| C.3 Small Signal Equivalent Circuit                    | <b>C</b> .11 |

| C.4 Noise Performance                                  | C.13         |

| References                                             | C.15         |

| APPENDIX D: 2D NUMERICAL MODELING OF Si/SiGe/Si p-     |              |

| MOSFET's                                               | D.1          |

| D. I. Constant Francisco                               | D 1          |

| D.2 Mobility and Impact Ionization Models                              | D.1  |

|------------------------------------------------------------------------|------|

| References                                                             | D.3  |

| APPENDIX E: PARAMETER EXTRACTION FOR Si/SiGe/Si p-                     |      |

| MOSFET's                                                               | E.1  |

| E.1 Mobility Profiling in Long and Wide (FAT) Si/SiGe/Si p-MOSFET's    |      |

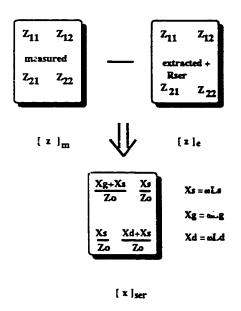

| E.2 Extraction of the Small Signal Equivalent Circuit from S-parameter |      |

| Measurements                                                           | E.3  |

| References                                                             | E.12 |

# **CHAPTER 1**

# INTRODUCTION

# 1.1. Why Silicon-Germanium?

Silicon technology has reached a very mature stage at which incremental progress is achieved with increasing difficulty. Further improvements in the performance of silicon IC's can be expected by using novel materials and device structures. One of these possibilities is being offered by an alloy of silicon and germanium SiGe, grown on Si substrates, which can form the basis for a host of new high speed electronic and optoelectronic devices [1-4].

White compatible with existing silicon chip-fabrication lines [3], SiGe offers a significant increase in device performance due to its superior transport properties as compared to silicon. Carrier mobilities are larger in SiGe than in Si [1,5] and result in higher speed of operation of SiGe devices. The energy bandgap of SiGe is smaller than that of silicon [5] and linearly scales with the Ge content, opening up exciting opportunities to build devices based on bandgap engineering concepts. These favorable properties of SiGe have spurred great interest in the IC community over the last few years.

One possible system application for SiGe devices is a portable digital transceiver. As illustrated in Fig.1.1. a state of the art version of such a transceiver is built

up from four chips, three of which are implemented in silicon and one in GaAs.

#### ANT1 ANT2 Plessey's GPSI DE6003 (Computer Design Nov. '93) RF requirements: RECEIVED DATA-CMOS 150 kB(z ANTENNA SWITCH: CMOS COMPATIBLE MHz IF RECEIVER (Roff/Ros) 24-25 GHz (BIPOLAR) LNA: CMOS, HBT (NF, bandwidth) MICROWAVE VCO: HBT GRAR FRONT END (1/f make) TRIPLE MIXER: HBT 2.65 350 2.15 GHz SYNTHESIZER MHz Hearty, NF) AND 18 MHz HPA: HBT or CMOS 700 MHz REFERENCE h current de OSCILLATOR OSCILLATOR ge output swing) AND DIVIDER (CMOS) (BIPOLAR) SERIAL kB/s O By compromising performs TRANSMIT

#### Digital wireless transceiver on a chip?

Figure 1.1 Possible application of Si/SiGe technology in a single-chip digital wireless transceiver. Current Si/SiGe device performance allows for the replacement of the GaAs block by a Si/SiGe circuit.

DATA

State of the art Si/SiGe HBT's can deliver most functions currently implemented in the RF GaAs block, with the exception of the low noise amplifier and antenna switching functions. Si/SiGe CMOS devices would be more suitable for the latter two circuits. High speed Si/SiGe CMOS devices would also facilitate a significant increase in the digital data rate. With its high speed, low voltage and low power features, Si/SiGe technology has the potential to integrate all these functions on a single chip, thus making the wristwatch personal communicator a possibility in the near, rather than distant, future.

# 1.2. Silicon-Germanium Material Properties

#### 1.2.1. Lattice Constant and Film Growth

Irrespective of the Ge mole fraction Y,  $Si_{1-Y}Ge_Y$  maintains a diamond structure, which is characteristic for both silicon and germanium [2,5]. The lattice constant of  $Si_{1-Y}Ge_Y$  depends on the mole fraction Y and, for low Y, can be expressed as [5]

$$a_{SiGe} = a_{Si} + Y(a_{Ge} - a_{Si})$$

(1.1)

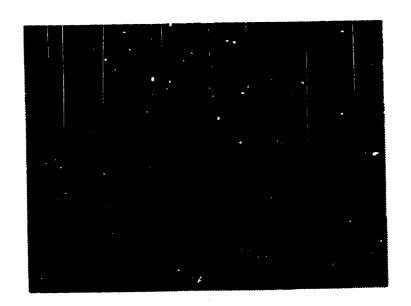

where  $a_{Si}$  is the lattice constant of silicon and  $a_{Ge}$  is the lattice constant of germanium. Since  $a_{Si}$  (0.5431 nm) and  $a_{Ge}$  (0.5646 nm) have different values, a lattice mismatch of 4.17% occurs at room temperature. Because of the lattice mismatch, only thin layers of SiGe can be grown free of misfit dislocations on a silicon substrate. As illustrated schematically in Fig. 1.2, two situations can occur when a SiGe layer is grown on top of a Si substrate a) an in-plane compressed (coherently) strained SiGe lattice with a corresponding lattice expansion along the growth direction and b) generation of dislocations at the SiGe/Si interface.

In the first case, known as pseudomorphic growth [5], coherent mechanical strain builds up in the SiGe film to retain a dislocation free interface between Si and SiGe. The in-plane lattice constant of the SiGe film thus grown is given by the equation [5]

$$a_{\text{in-plane}} = \frac{a_{\text{SiGe}} x_{\text{SiGe}} + a_{\text{Si}} x_{\text{Si}}}{x_{\text{SiGe}} + x_{\text{Si}}}$$

(1.2)

where  $x_{SiGe}$  and  $x_{Si}$  are the thicknesses of the SiGe film and of the Si substrate, respectively.

Figure 1.2 Schematic illustration of the mechanisms by which thin SiGe films can be grown on a Si substrate.

The second case, generation of dislocations, produces a very defective interface between SiGe and Si which results in a poor quality SiGe film being grown on top of the silicon substrate. For these reasons, only pseudomorphic SiGe films are of interest for device and circuit applications.

For the film to be strained and dislocation free during and after growth, two conditions must be met. First, the SiGe film must be thin enough to accommodate the strain, i.e.  $x_{SiGe} \ll x_{Si}$ . The thickness of the film is bound by the Matthews-Blakeslee

critical value [6], which is a function of the lattice mismatch. For SiGe films, the critical thickness decreases strongly as the Ge mole fraction increases [5]. Second, the temperature during the growth and during all subsequent processing steps must be sufficiently low in order to prevent strain relaxation. The requirement for low temperature processing results from the typically metastable character of most strained SiGe films used in semiconductor devices. Under high temperature conditions, the film cannot maintain the strain and misfit dislocations are generated. In fact, both the temperature and the duration of the process, i.e. the thermal budget, are important. As an example, temperatures up to 600 °C applied for tens of minutes are considered to be "safe", while those up to about 900 °C are "acceptable" for time intervals up to two minutes before strain relaxation and generation of dislocations set in [7]†.

In the example considered in Fig. 1.2, the SiGe film was grown on a silicon substrate. In some device applications a complementary processing sequence, the growth of a tensile strained silicon layer on top of a relaxed SiGe layer, is important. Both systems, strained SiGe on relaxed Si and strained Si on relaxed SiGe, can be grown either by Molecular Beam Epitaxy (MBE) [8], or by one of several variants of Chemical Vapor Deposition (CVD) techniques such as High Vacuum (HV-CVD) [1], Rapid Thermal (RT-CVD) [9] or Limited Reaction Processing (LRP-CVD) [7]. Because of the better quality of the grown layers and because of the possibility of processing a batch of wafers in one run, HV-CVD has emerged as the industry

<sup>†</sup> The MOSFET structures described in this thesis are within the Mathews-Blakeslee critical thickness. While this and other strain-relaxation models are still debated, these experimental results, as well as IBM's SiGe MOSFET's [2] indicate that average Ge mole fractions of 25% over 15 nm are technologically feasible.

standard for the growth of Si/SiGe heterojunctions [1-3].

#### 1.2.2. Bandgap

One of the key features of SiGe is its energy bandgap  $E_{G_{SiGe}}$ , which is lower than that of silicon  $E_{G_{Si}}$ . The bandgap of SiGe depends on the Ge mole fraction Y and changes from 1.17eV for Y = 0 to 0.78 eV for Y = 0.5 [5]. In this range of Ge mole fractions, the dependence has an approximately linear character [5].

$$\Delta E_G = E_{G_{SiGe}} - E_{G_{SiGe}} = 0.74*Y$$

(1.3)

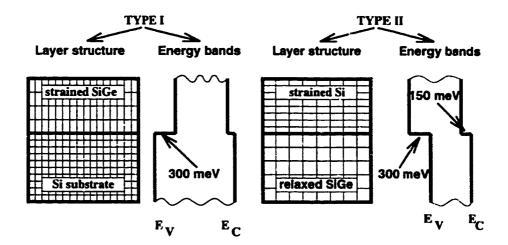

In addition to the energy bandgap, a critical issue for device operation is the actual bandgap alignment between SiGe and Si. The two combinations of Si and SiGe that are relevant for device operation and the corresponding energy bands alignments are illustrated schematically in Fig. 1.3.

Figure 1.3 Schematic illustration of the energy bands alignment and of the layer structure in type I and type II Si/SiGe heterostructures. In both cases the Ge mole fraction Y is 0.5.

The band alignment shown in the left side of Fig. 1.3 is of the type I character, i.e. the SiGe bandgap lies within the Si bandgap. The bandgap difference  $\Delta E_G$  is the sum of the valence band  $\Delta E_V$  and of the conduction band  $\Delta E_C$  offsets

$$\Delta E_{\rm G} = \Delta E_{\rm V} + \Delta E_{\rm C} \tag{1.4a}$$

and is accommodated almost entirely in the valence band (i.e.  $\Delta E_V \gg \Delta E_C$ ) [1,5]. The large valence band discontinuity and its monotonic increase with the Ge mole fraction are two of the most attractive features of the type I Si/SiGe alignment that can be used to control hole confinement in field effect transistors and hole injection and electron transport in npn heterostructure bipolar transistors [1].

The band diagram is significantly different for the second case, that of strained silicon on a relaxed SiGe substrate. This band alignment, in which the SiGe bandgap lies partially above the silicon bandgap, is defined as type II. In this case, eqn.(1.4a) must be replaced by

$$\Delta E_{G} = \Delta E_{V} - \Delta E_{C} \tag{1.4b}$$

The type II energy bands alignment scheme allows for the separate confinement of electrons and holes at the heterojunction, i.e. holes in the SiGe layer and electrons in the strained Si layer. This property of the type II system is used in both n-channel and p-channel FET's.

### 1.2.3. Carrier Transport in Silicon-Germanium Alloys

The in-plane electron and hole mobilities in SiGe are complex functions of the mechanical strain, of the Ge mole fraction Y, and of the various scattering

mechanisms in the SiGe and adjacent layers. For example, increasing the Ge mole fraction will reduce the effective mass and, consequently, enhance mobility. This trend competes with a reduction in mobility caused by alloy (up to mole fractions of 50%) and interface scattering. It was demonstrated both theoretically [10-12] and experimentally [13-16] that carrier mobilities are larger in strained SiGe and strained silicon films than in conventional silicon. Electron mobilities as large as 2700 cm<sup>2</sup>/Vs have been obtained at room temperature in strained silicon layers grown on a SiGe substrate[1], while SiGe hole mobilities of 1300 cm<sup>2</sup>/Vs have been measured [16]. It is noteworthy that hole mobilities in SiGe quantum layers are theoretically predicted to be larger than in pure germanium [10], indicating that mobility cannot be simply extrapolated between Si and Ge.

It must be mentioned that, despite the larger mobilities, the saturation drift velocities of electrons and holes in SiGe layers are comparable to those of silicon [14, 15]. Therefore, small geometry devices in which the velocity saturation effect is the current limiting mechanism might not benefit from the presence of SiGe to the extent suggested by the mobility data.

### 1.3. Silicon-Germanium Devices

By inserting a precisely controlled SiGe layer in the vertical structure of a Si bipolar or field effect transistor an additional design freedom is obtained. As a consequence, the current and voltage gain, unity gain cutoff frequency and the maximum frequency of oscillation can be optimized over wider voltage and temperature ranges, as compared to the original silicon devices. Because of the possibility of controlling

both the bandgap and the index of refraction, SiGe has also been successfully applied to heterostructure photodetectors and optical waveguides. For a recent overview of silicon-based optoelectronics, reference [17] may be consulted.

In the case of Heterostructure Bipolar Transistors (HBT's) [1-3], the interest in a SiGe base was first driven by the ability to tailor the bandgap of SiGe so that an exponential increase in the current gain  $\beta$  could be traded off for a reduction in the base resistance, thus simultaneously improving the gain, the maximum frequency of oscillation and the noise figure of the device. Later refinements involved grading the Ge profile along the base in order to maximize the electron velocity and, thereby, the cutoff frequency of the transistor [1,3]. The SiGe HBT is by now a mature device that has already been integrated in a commercial BiCMOS process [3,4]

Even though research interest in SiGe FET's [18] predated that in SiGe HBT's, they have yet to make a significant impact on Si technology. The conventional way of enhancing the performance of field effect transistors is to scale down the gate length. Another technique is to use a material with better transport properties as the conductive channel between source and drain. SiGe is the ideal material to boost the speed of both n and p-channel Si MOSFET's. Developments over the last decade have demonstrated that high speed FET action can be achieved with both type I and type II Si/SiGe heterostructure alignments, employing either Schottky or MOS gates [18-27]. Record breaking electron and hole mobilities have so far been the exclusive domain of type II Si/SiGe FET's [17, 21-25]. However, these devices, which require a relaxed SiGe substrate, have proved until now very difficult to integrate in conven-

tional Si technology. Furthermore, the defect density in type II Si/SiGe layers is still too high to meet VLSI specifications. For these reasons, only type I Si/SiGe devices will be discussed.

# 1.4. Why Si/SiGe/Si p-MOSFET's?

First, because the performance of state of the art silicon CMOS and BiCMOS circuits is limited by the slow p-channel MOSFET, upgrading the p-FET requires urgent attention. Secondly, while undoubtedly a worthy pursuit, the implementation of n-channel devices raises more severe hurdles. Due to the negligible conduction band offset in the type I Si/SiGe system, there is minimal electron confinement to increase n-MOSFET speed. n-MOSFET's have therefore been attempted primarily in the Type II system, beset by fabrication problems.

Recently reported type I Si/SiGe/Si p-channel MOSFET's, which are relatively easy to fabricate in a VLSI process [26,27], have exhibited hole mobilities higher than in Si devices, but well below those measured in type II Schottky gate, Modulation-Doped FET's (MODFET's). Based on very recent experiments [28], which indicate a monotonic increase in hole mobility with the Ge mole fraction, it is highly probable that a significant increase in performance can only be attained if very large (in excess of 40-50%) Ge mole fractions are used in the channel. Practical implementations of large Ge mole fractions in Type I p-MOSFET's have been precluded by the necessity of complying with the Matthews-Blakeslee critical layer thickness [6], by the rectangular or trapezoidal shape [29] of the Ge profile in the channel, and by interface scattering at very abrupt Si/SiGe interfaces [1]. The latter

severely degrades mobility. The thrust of the thesis is to demonstrate, through theory and experiments, that a practical solution to these problems may be achieved by using a triangular Ge profile in the channel of the MOSFET.

# 1.5. Thesis Objectives and Outline

The objectives of this thesis are to demonstrate the feasibility of a VLSI compatible type I Si/SiGe/Si p-MOSFET with triangular Ge profiles and to develop electrical characterization techniques for Si/SiGe/Si MOSFET technology.

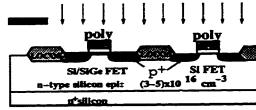

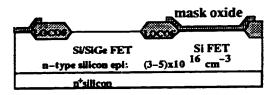

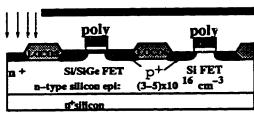

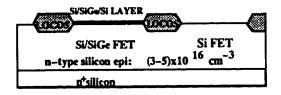

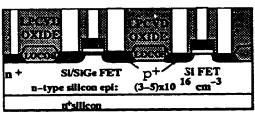

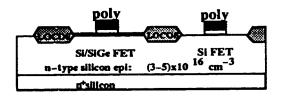

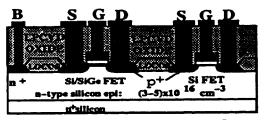

In order to meet these goals, a theory is developed in Chapter 2 to model and interpret the C-V characteristics of heterostructure MOS capacitors [30]. This model is followed up in the second part of that chapter by the proposal and experimental validation of a C-V characterization technique that extracts the parameters of the Si/SiGe heterojunction, which are critical in the design of Si/SiGe/Si p-MOSFET's [31]. The material and process information obtained from these measurements include the valence band offset and the Ge composition at the Si/SiGe interface, as well as the doping level in the Si substrate. The concept of a Si/SiGe/Si p-MOSFET with triangular Ge channel profiles [32] is proposed in Chapter 3 and its benefits in comparison with current Si/SiGe/Si p-MOSFET's are discussed based on newly developed analytical models and on two-dimensional simulation results [33,34]. A fabrication process, compatible with conventional silicon VLSI process lines, whereby SiGe and Si p-MOSFET's are integrated on the same chip, is described in Chapter 4 [35,36]. Experimental characteristics of Si and SiGe transistors implemented in this technology are also presented. Finally, in Chapter 5, conclusions are drawn regarding the implications of this work for the short and medium term prospects of Si/SiGe IC's. Possible related topics for future research are also discussed.

#### References

- B. S. Meyerson, "UHV/CVD growth of Si and SiGe Alloys: Chemistry, Physics and Device Applications," *Proc. IEEE*, vol. 80, pp. 1592-1608, 1992.

- 2. B. S. Meyerson, "High-Speed Silicon Germanium Electronics," *Scientific American*, pp. 62-67, March 1994.

- D. L. Harame, E. F. Crabbé, J. D. Cressler, J. H. Comfort, J. Y. -C. Sun, S. R. Stiffler, E. Kobeda, J. N. Burghartz, M. M. Gilbert, J. C. Malinowski, A. J. Daly, S. Ratanaphanyrat, M. J. Saccamango, W. Rausch, J. Cotte, C. Chu, and J. M. C. Stork, "A High Performance Epitaxial SiGe-Base ECL BiCMOS Technology," *Proc. IEDM*, pp. 19-22, 1992.

- J. D. Cressler, D. L. Harame, J. H. Comfort, J. M. C. Stork, B. S. Meyerson, and T. E. Tice, "Silicon-Germanium Heterojunction Bipolar Technology: The Next Leap in Silicon?," *Proc. IEEE ISSCC*, pp. 24-27, 1994.

- 5. R. People, "Physics and applications of Ge<sub>x</sub>Si<sub>1-x</sub>/Si strained layer heterostructures," *IEEE J. of Quantum Electron.*, vol. **QE-22**, pp. 1696-1702, 1986.

- 6. R. People and J. C. Bean, "Calculation of critical layer thickness versus lattice mismatch for strained layer heterostructures," *Appl. Phys. Lett.*, **47**, pp. 322-324, 1985 in conjunction with

- J. W. Matthews and A. E. Blakeslee, "Defects in epitaxial multilayers I. Misfit dislocations in layers," J. Crystal Growth, 27, pp. 118-122, 1974.

- 7. J. F. Gibbons, C. M. Gronet, and K. E. Williams, "Limited Reaction Processing:

- silicon epitaxy," *Appl. Phys. Lett.*, vol. 47, pp. 721-723, 1985, and D. Vook, T. I. Kamins, G. Burton, P. J. Vande Voorde, H. H. Wang, R. Coen, J. Lin, D. Pettengill, P. K. Yu, S. Rosner, J. E. Turner, S. S. Laderman, H.-S. Fu, and A. S. Wang, "Double-Diffused Graded SiGe-Base Bipolar Transistors," *IEEE Trans. Electron. Dev.*, vol. ED-41, pp. 1013-1018, 1994.

- J. C. Bean, L. C. Feldman, A. T. Fiory, S. Nakahara, and I. K. Robinson, "Ge<sub>1-x</sub>Si<sub>x</sub>/Si strained layer superlattice grown by molecular beam epitaxy," J. Vac. Sci. Technol., vol. A2, pp 436-440, 1984.

- M. L. Green, B. E. Weir, D. Brasen, Y. F. Hsieh, G. Higashi, A. Feygenson, L.

C. Feldman, and R. L. Headrick, "Mechanically and thermally stable Si-Ge films and heterojunction bipolar transistors grown by rapid thermal chemical vapor deposition at 900 C," J. Appl. Phys., vol. 69, pp. 745-751, 1991.

- S. K. Chun and K. L. Wang, "Effective Mass and Mobility of Holes in Strained Si<sub>1-x</sub>Ge<sub>x</sub> Layers on (001) Si<sub>1-y</sub>Ge<sub>y</sub> Substrate," *IEEE Trans. Electron. Dev.*, vol. ED-39, pp. 2153-2164, 1992.

- H. Miyata, T. Yamada, and D. K. Ferry, "Electron transport properties of a strained Si layer on a relaxed Si<sub>1-x</sub>Ge<sub>x</sub> substrate by Monte Carlo simulation," Appl. Phys. Lett., vol. 62, pp. 2661-2663, 1993.

- 12 T. Vogelsang and K. R. Hofmann, "Electron transport in strained Si layers on Si<sub>1-x</sub>Ge<sub>x</sub> substrates," *Appl. Phys. Lett.*, vol. **63**, pp. 186-188, 1993.

- P. M. Garone, V. Venkataraman, and J. C. Sturm, "Mobility Enhancement and Quantum Mechanical Modeling in Ge<sub>x</sub>Si<sub>1-x</sub> Channel MOSFET's from 90 to

- 300 K," Proc. IEDM, pp. 29-32, 1991.

- K. Ismail, S. F. Nelson, J. O. Chu, and B. S. Meyerson, "Ele-tron transport properties of Si/SiGe heterostructures: Measurements and device implications," Appl. Phys. Lett., vol. 63, pp. 660-662, 1993.

- 15 S. H. Li, J. M. Hinckley, J. Singh, and P. K. Bhattacharya, "Carrier velocity-field characteristics and alloy scattering potential in Si<sub>1-x</sub>Ge<sub>x</sub>/Si," *Ap*, *l. Phys. Lett.*, vol. **63**, pp. 1393-1395, 1993.

- U. König and F. Schäffler, "p-Type Ge-Channel MODFET's with High Transconductance Grown on Si Substrates", *IEEE Electron Device Lett.*, vol. EDL-14, pp. 205-207, 1993.

- 17 R. A. Soref, "Silicon-Based Optoelectronics," *Proc. IEEE*, vol. **81,** pp. 1687-1706, 1993.

- T. P. Pearsall, J. C. Bean, R. People, and A. T. Fiory, "Ge<sub>x</sub>Si<sub>1-x</sub> modulation-doped p-channel field effect transistors," *Proc. 1st. Int. Symp. Silicon Molecular Beam Epitaxy, Electrochemical Soc.* Pennington, N.J., pp.400-405, 1985.

- H. Dambkes, H. -J. Herzog, H. Jorke, H. Kibbel, and E. Kasper, "The n-channel Si/SiGe modulation-doped field-effect transistor," *IEEE 1 rans. Electron Dev.*, vol. ED-33, pp. 633-6638, 1986.

- 20. D. K. Nayak, J. C. S. Woo, J. S. Park, K. -L. Wang, and K. P. MacWilliams, "Enhancement-Mode Quantum-Well Ge<sub>x</sub>Si<sub>1-x</sub> PMOS," *IEEE Electron Device Lett.*, vol. EDL-12, pp. 154-156. 1991.

- U. König and F. Schäffler, "Si/SiGe Modulation-Doped Field-Effect Transistor with two electron channels," *Electronics Lett.*, vol. 22, pp. 1405-1407, 1991.

- U. König, A. J. Boers, F. Schäffler, and E. Kasper, "Enhancement mode n-channel Si/SiGe MODFET with high intrinsic transconductance," *Electronics Lett.*, vol. 23, pp. 160-162, 1992.

- K. Ismail, B. S. Meyerson, S. Rishton, J. Chu, S. Nelson, and J. Nocera, "High-Transconductance n-Type Si/SiGe Modulation-Doped Field-Effect Transistors,"

IEEE Electron Device Lett., vol. EDL-13, pp. 229-231, 1992.

- 24. G. Schüberth, F. Schäffler, M. Besson, G. Abstreiter, and E. Gornik, "High electron mobility in modulation-doped Si/SiGe quantum well structures," Appl. Phys. Lett., vol. 59, pp. 3318-3320, 1991.

- 25. J. Wesler, J. L. Hoyt, and J. F. Gibbons, "Electron Mobility Enhancement in Strained-Si N-Type Metal-Oxide-Semiconductor Field-Effect Transistors," IEEE Electron Dev. Lett., vol. EDL-15, pp. 100-102, 1994.

- 26. V. P. Kesan, S. Subbanna, P. J. Restle, M. J. Tejwani, J. M. Aitken, S. S. Iyer, and J. A. Ott, "High-Performance 0.25 μm p-MOSFET's with Silicon-Germanium Channels for 300K and 77K Operation," *Proc. IEDM*, pp. 25-28, 1991.

- 27. S. Verdonckt-Vanderbroek, E. F. Crabbe, B. S. Meyerson, D. L. Harame, P. J. Restle, J. M. C. Storck, A. C. Megdanis, C. L. Stanis, A. A. Bright, G. M. W. Kroesen, and A. C. Warren, "High-Mobility Modulation-Doped Graded SiGe-Channel p-MOSFET's," *IEEE Electron Dev. Lett.*, vol. EDL-12, pp. 447-449,

1991.

- 28. T. K. Carns, S. K. Chun, M. O. Tanner, K. L. Wang, T. I. Kamins, J. E. Turner, D. Y. C. Lie, M.-A. Nicolet, and R. G. Wilson, "Hole Mobility Measurements in Heavily Boron Doped Si<sub>I-x</sub>Ge<sub>x</sub> Strained Layers," *IEEE Trans. Electron Dev.*, vol. 41, pp. 1273-1281, 1994.

- S. Verdonckt-Vanderbroek, E. F. Crabbe, B. S. Meyerson, D. L. Harame, P. J. Restle, J. M. C. Storck, A. C. Megdanis, and J. B. Johnson, "SiGe-Channel Heterojunction p-MOSFET's," *IEEE Trans. Electron Dev.*, vol. 41, pp. 90-101, 1994.

- 30. K. Iniewski, S. Voinigescu, J. Atcha and C. A. T. Salama, "Analytical Modeling of Threshold Voltages in p-Channel Si/SiGe/Si MOS Structures," *Solid-State Electron.*, vol. **36**, pp. 775-783, 1993.

- 31. S. Voinigescu, K. Iniewski, R. Lisak, C. A. T. Salama, J. P. Noël and D. Houghton, "New technique for the Characterization of Si/SiGe Layers using heterostructure MOS Capacitors," *Solid-St. Electron*, vol. 37, pp. 1491-1501, 1994.

- 32. S. Voinigescu and C. A. T. Salama, "Optimal channel grading in p-type Si/SiGe metal oxide semiconductor field effect transistors (MOSFET's)," *Can. J. Phys.*, vol. **70**, pp. 975-978, 1992.

- 33. S. Voinigescu, P. B. Rabkin, C. A. T. Salama, and P. Blakey, "2D Numerical Investigation of Gate Structure, Band Alignment and δ-Doping Effects on the Transconductance and Cutoff Frequency of Submicrometer Si/SiGe FET's,"

Proc. of the European Solid State Device Research Conference, Grenoble,

France, pp. 361-364, 1993.

- 34. S. P. Voinigescu, P. B. Rabkin, C. A. T. Salama, and P. Blakey, "2D Numerical Investigation of the Impact of Compositional Grading on the Performance of Submicrometer Si/SiGe MOSFET's," submitted for publication in *IEEE Trans. Electron Dev.*, May, 1994.

- S. P. Voinigescu, C. A. T. Salama, J. -P. Noël, and T. I. Kamins, "Si/SiGe/Si p-MOSFET with Triangular Ge Channel Profiles," European Solid State Device Research Conference, Edinburgh, UK, September, 1994.

- 36. S. P. Voinigescu, C. A. T. Salama, J. -P. Noël, and T. I. Kamins, "Optimized Ge Channel Profiles for VLSI compatible Si/SiGe p-MOSFET's," *International Electron Device Meeting*, December, 1994.

# **CHAPTER 2**

# THE HETEROSTRUCTURE MOS CAPACITOR

#### 2.1. Introduction

A salient feature of the Si/SiGe heterostructure system† is the possibility of growing high quality oxides, comparable to those obtained on Si [1,2]. The aim of this chapter is to demonstrate - based on analytical models, numerical simulation and experimental results - that, like its silicon counterpart, the Si/SiGe heterostructure MOS capacitor is a useful tool in the understanding of the underlying physics of Si/SiGe/Si MOSFET's. It is also shown that it can become an effective characterization vehicle for Si-based heterostructure technology.

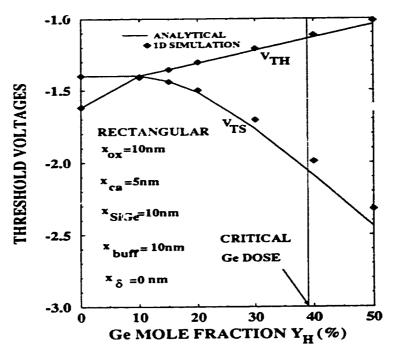

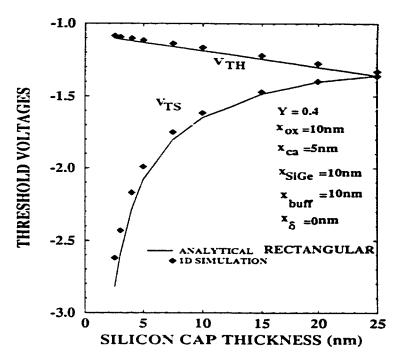

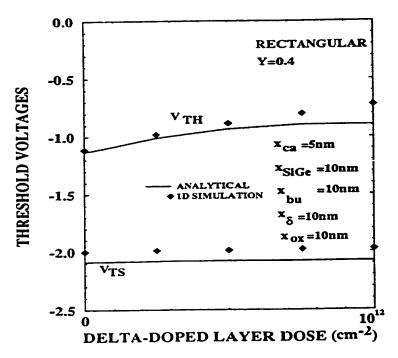

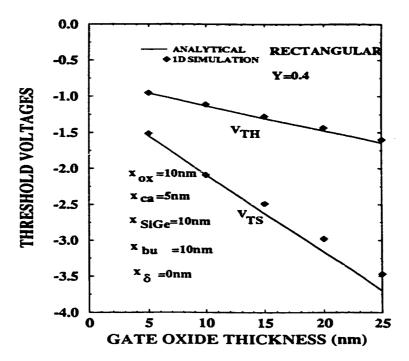

This chapter is organized as follows. First the Si/SiGe MOS capacitor structure is defined and the main assumptions in the derivation of the threshold voltages and of the charge distribution are discussed. The energy band diagram and the charge distribution in the three regimes - inversion, depletion, and accumulation - are compared with those of a conventional MOS capacitor. Analytical expressions for the threshold voltages are also derived. Their dependence on structural parameters such as the Ge mole fraction Y, the silicon cap layer thickness  $x_{ca}$  and the impurity dose in the  $\delta$ -doped layer is investigated using analytical and one dimensional (1D) simulation

<sup>†</sup> For simplification purposes, the term SiGe will be used throughout the thesis to refer to a SiGe alloy with a Ge mole fraction Y, and a Si mole fraction 1-Y.

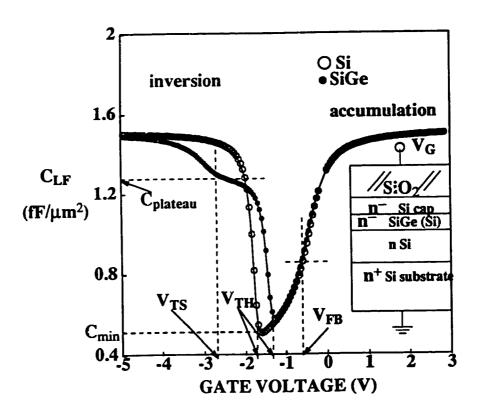

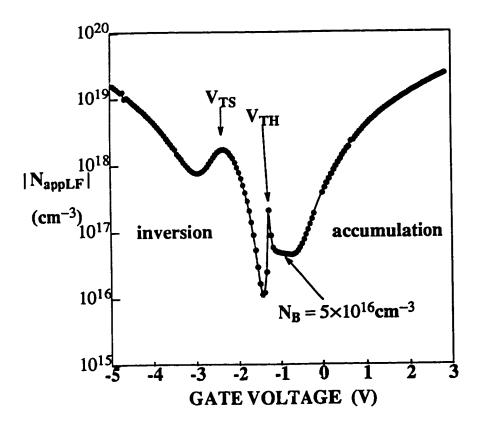

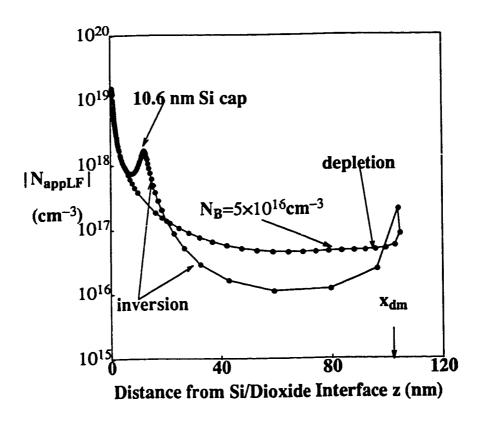

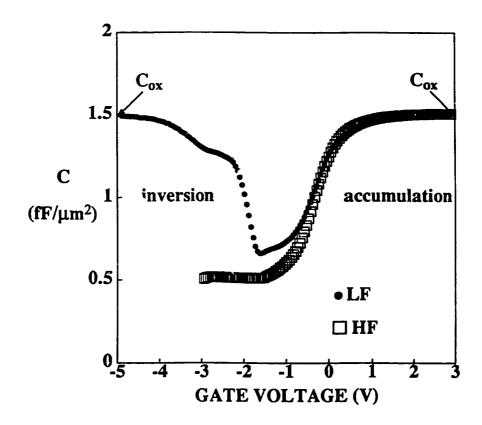

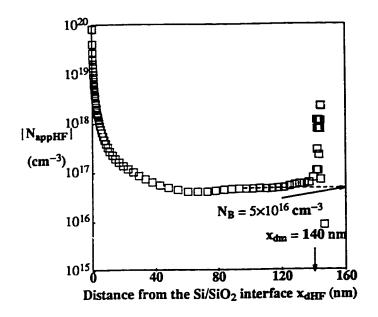

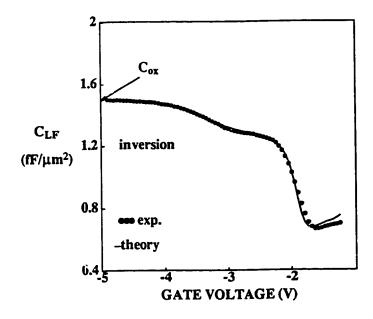

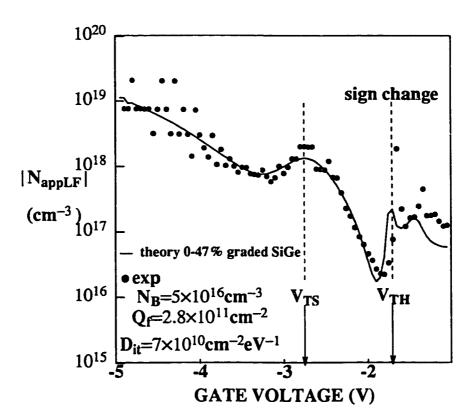

results. The capacitance-voltage (C-V) characteristics are discussed next. Finally, a technique is developed for the reverse engineering of the layer structure from high-frequency (HF) and low-frequency (LF) C-V measurements. The limitations of the technique and the sources of errors associated with the measurements are documented. Experimental validation is provided.

The analytical derivation of the threshold voltages, of the semiconductor charge, and of the semiconductor capacitance is described in detail in Appendix A. An overview of the one-dimensional numerical simulation technique, which selfconsistently solves Poisson's and Schrödinger's equations to obtain the potential and carrier distributions inside the capacitor structure, is presented in Appendix B.

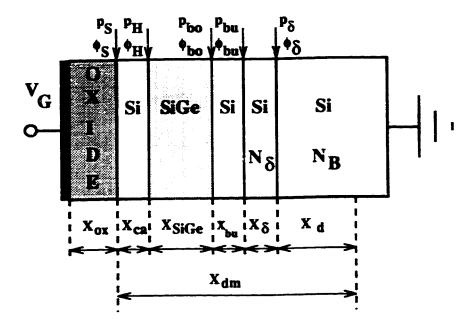

# 2.2. Physics of Heterostructure MOS Capacitors

Consider the schematic of the p-channel heterostructure MOS capacitor shown in Fig.2.1. The structure is similar to that of a conventional silicon MOS capacitor, except for the presence of the undoped SiGe channel, of thickness  $x_{SiGe}$ , separated from the Si/SiO<sub>2</sub> interface by a thin undoped silicon cap layer of thickness  $x_{ca}$ . A  $\delta$ -doped boron layer, of thickness  $x_{\delta}$ , is usually inserted below the SiGe channel [3]. Separation between the SiGe film and the  $\delta$ -doped film is provided by an undoped silicon buffer, of thickness  $x_{bu}$ . This separation is necessary in order to prevent the mobile holes in the SiGe film from scattering by the ionized acceptors of the  $\delta$ -doped region. The primary role of the  $\delta$ -doped layer is to control the threshold voltage of the SiGe channel. This sandwich of layers is grown by CVD or MBE techniques on top of a uniformly-doped, n-type silicon substrate.

Figure 2.1 Si/SiGe MOS capacitor structure and notation employed for potential and hole concentration at each interface.

#### Basic assumptions

In order to facilitate understanding of the operation of the heterostructure MOS capacitor and to render the problem analytically tractable, the following assumptions are made

- the bandgap difference  $\Delta E_G$  between Si and SiGe lies entirely in the valence band, i.e.  $\Delta E_G = \Delta E_V$  [4],

- the contribution of the fixed charge in the undoped layers is negligible,

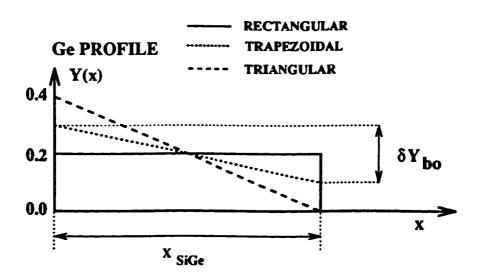

- the Ge mole fraction Y is either constant throughout the SiGe layer, or it varies linearly from Y<sub>bo</sub>, at the bottom of the SiGe film, to Y<sub>H</sub> at the top,

the Ge profile is constrained by the assumption of positive grading i.e.

$$\delta Y(x) = Y_H - Y(x) \ge 0$$

implying that, as illustrated in Fig. 2.2, only rectangular ( $\delta Y_{bo} = 0$ ), trapezoidal ( $\delta Y_{bo} > 0$ ) or triangular ( $\delta Y_{bo} = Y_H$  and  $Y_{bo} = 0$ ) profiles are allowed.

The latter restriction is not really a limitation since all cases of practical interest are covered.

Figure 2.2 Three types of Ge profiles considered for the Si/SiGe MOS capacitor structure.

Because of their linear dependence on the Ge mole fraction, the valence band offset  $\Delta E_V$  and the permittivity in the SiGe film  $\epsilon_{SiGe}$ , become position dependent [4] and can be expressed as

$$\Delta E_{V}(x) = \Delta E_{VH} - 0.74\delta Y(x) = \Delta E_{VH} - qF_{bi}x \qquad (2.1)$$

$$\varepsilon_{\text{SiGe}}(x) = \varepsilon_{\text{SiGeH}} - 4.2\delta Y(x)$$

(2.2)

where  $F_{bi} = \frac{0.74\delta Y_{bo}}{x_{SiGe}}$  is the built-in electric field due to Ge profile grading. The

total Ge dose in the SiGe film can be expressed in cm, (Y is dimensionless), as

Dose(Ge) =

$$\int_0^{x_{SiGe}} Y(x)dx = \left[ Y_H - \frac{\delta Y_{bo}}{2} \right] x_{SiGe}$$

(2.3)

In the above equations, the values at the top heterojunction (subscript H) are considered as reference.

#### 2.2.1. Charge Distribution and Threshold Voltages

Figure 2.1 illustrates the definitions of the potential  $\phi(x)$  and of the hole concentration p(x) at the substrate/ $\delta$ -doped layer interface (subscript  $\delta$ ), at the buffer/ $\delta$ -doped layer interface (subscript bu), at the bottom Si/SiGe heterojunction (subscript bo), at the top Si/SiGe heterojunction (subscript H) and at the Si/SiO<sub>2</sub> interface (subscript S).

The Fermi potential in the bulk corresponds to that of an n type silicon substrate with uniform ionized donor concentration  $N_{\rm B}$

$$\phi_{\rm F} = -\frac{\rm KT}{\rm q} \ln \left[ \frac{\rm N_B}{\rm n_{iSi}} \right] \tag{2.4}$$

By accounting for the position-dependent bandgap, the concentration of mobile holes p(x) is expressed as

$$p(x) = N_{B} \exp \left[ \frac{2q\phi_{F} + \Delta E_{G}(x) - q\phi(x)}{KT} - \ln \left[ \frac{N_{VSi}}{N_{VSiGe}} \right] \right]$$

(2.5)

Because of the negligible conduction band offset, the electron concentration is identical to that in a silicon MOS capacitor

$$n(x) = N_B \exp\left[\frac{\dot{\phi}(x)}{\dot{\phi}_T}\right] \tag{2.6}$$

Similarly, the gate voltage  $V_G$ , and the total semiconductor charge  $Q_T$ , can be described in terms of the su face potential  $\phi_S$  [5]

$$V_G = V_{FB} + \phi_S + V_{ox} = V_{FB} + \phi_S - \frac{\sqrt{2q\epsilon_{Si}N_B\phi_T f(\phi_S)}}{C_{ox}}$$

(2.7)

$$Q_{T} = \sqrt{2q\varepsilon_{Si}N_{B}\phi_{T}f(\phi_{S})}$$

(2.8)

where  $C_{ox} = \varepsilon_{ox}/x_{ox}$  is the gate oxide capacitance per unit area,  $x_{ox}$  is the gate oxide thickness,  $V_{FB}$  is the flatband voltage which includes the contribution of the work-function difference  $\phi_{MS}$  between the gate and the silicon substrate and that of the fixed charge  $Q_f$  at the Si-SiO<sub>2</sub> interface.  $f(\phi_S)$  contains the heterojunction-specific information and its expression is derived in Appendix A.

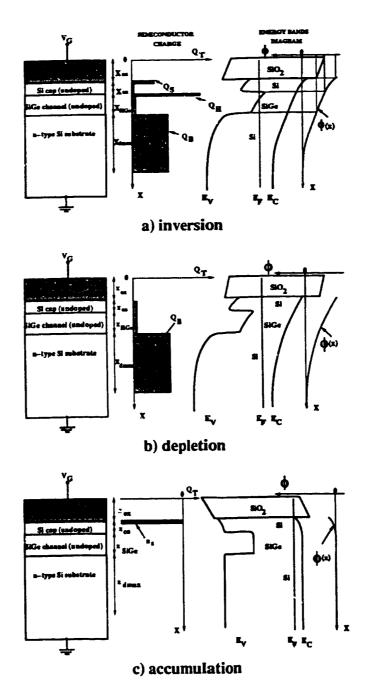

Figure 2.3 shows the schematic energy bands diagram and the corresponding charge distribution in the a) inversion, b) depletion and c) accumulation regimes. For the sake of simplicity, the  $\delta$ -doped layer is not included.

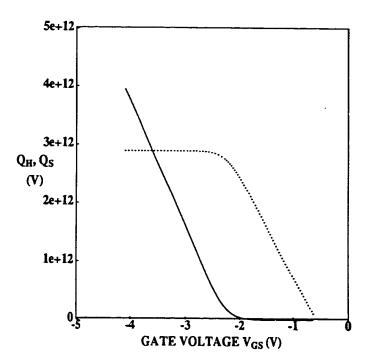

The distinctive feature of the charge distribution is the presence of mobile holes in strong inversion at both the Si/SiO<sub>2</sub> interface p<sub>S</sub>, and at the top Si/SiGe heterojunction p<sub>H</sub>. Since the type I Si/SiGe heterojunction has a negligible conduction band offset, the accumulation and depletion charges are similar to those of a MOS capacitor fabricated in silicon. Therefore, the focus next is on the investigation of the

threshold voltages and of the inversion charge.

Figure 2.3 Schematic energy bands diagrams and charge distribution in a) inversion, b) depletion and c) accumulation in a Si/SiGe MOS capacitor.

The onset of strong inversion at the top Si/SiGe interface corresponds to the gate voltage at which the concentration of minority holes at the top Si/SiGe heterojunction is equal to the substrate doping concentration N<sub>B</sub> [6]

$$p_{H} \begin{vmatrix} p_{H} \\ V_{G} = V_{TH} \end{vmatrix} = N_{B} \exp \left[ \frac{2q\phi_{F} + \Delta E_{VH} - q\phi_{H}}{KT} - \ln \left( \frac{N_{VSi}}{N_{VSiGe}} \right) \right] = N_{B}$$

(2.9)

This leads to the following condition for the threshold potential  $\phi_{TH}$  at the top heterojunction

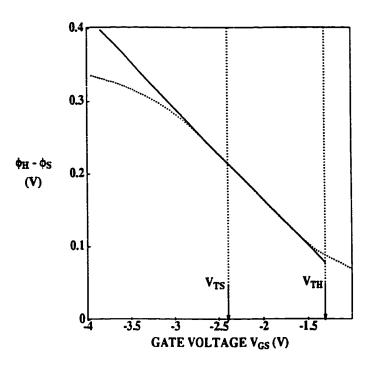

$$\phi_{TH} = \phi_H \bigg|_{V_G = V_{TH}} = 2\phi_F + \frac{\Delta E_{VH}}{q} - \phi_T \ln \left( \frac{N_{VSi}}{N_{VSiGe}} \right)$$

(2.10)

where  $N_{VSi}$  and  $N_{VSiGe}$  are the densities of states in the valence band for silicon and for SiGe, respectively, and  $\phi_T$  is the thermal voltage. The gate voltage which causes strong inversion at the top Si/SiGe interface is denoted by  $V_{TH}$ , the threshold voltage of the SiGe channel.

Similarly, strong inversion at the Si/SiO<sub>2</sub> interface is defined as

$$p_{S} \Big|_{V_{G} = V_{TS}} = N_{B} \exp\left[\frac{2\phi_{F} - \phi_{S}}{\phi_{T}}\right] = N_{B}$$

(2.11)

and the corresponding threshold surface potential  $\phi_{TS}$  must satisfy the condition

$$\phi_{TS} = \phi_S \bigg|_{V_G = V_{TS}} = 2\phi_F \tag{2.12}$$

The gate voltage which causes strong inversion at the surface of the silicon cap layer is denoted by  $V_{TS}$ , the threshold voltage of the surface channel [6].

A simplified version of  $f(\phi_S)$  is plugged into eqn. (2.7) to derive expressions for the threshold voltages  $V_{TH}$  and  $V_{TS}$ . The fixed charge in the depletion layer and the mobile hole charge in the SiGe film are accounted for. The hole charge in the silicon cap is neglected since, for a properly designed structure,  $V_{TH}>V_{TS}$ , indicating that strong inversion occurs first at the top Si/SiGe heterointerface. As detailed in Appendix A, for  $V_{TS} \leq V_G$ , the following relation holds

$$V_{G} = V_{FB} + \phi_{H} - Q_{B} \left[ \frac{x_{ca}}{\varepsilon_{Si}} + \frac{x_{ox}}{\varepsilon_{ox}} \right] \sqrt{1 + H(\phi_{H})}$$

(2.13)

where  $Q_B = q(N_Bx_d-N_\delta x_\delta)$  is the fixed charge in the depletion layer, accounting for the contribution of the  $\delta$ -doped layer and of the uniformly-doped substrate.  $H(\phi_H)$  represents the contribution of holes in the SiGe layer to the potential drop across the silicon cap.

The expression for  $V_{TH}$  is derived directly from eqn. (2.13) as

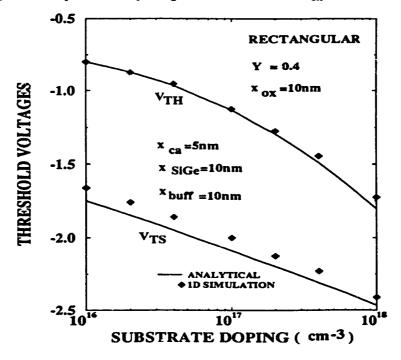

$$V_{TH} = V_{G} \Big|_{\phi_{H} = \phi_{TH}} = V_{FB} + \phi_{TH} - Q_{Bmax} \left( \frac{x_{ca}}{\varepsilon_{Si}} + \frac{x_{ox}}{\varepsilon_{ox}} \right) \sqrt{1 + H(\phi_{TH})}$$

(2.14)

In eqn.(2.14),  $x_d$  and  $Q_B$  assume their maximum values  $x_{dmax}$  and  $Q_{Bmax}$ , respectively, corresponding to the onset of strong inversion.