## Performance Monitoring and Visualization of Object-Oriented Operating Systems

by

Adam Czajkowski

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto

Copyright © 2008 by Adam Czajkowski

## **Abstract**

# Performance Monitoring and Visualization of Object-Oriented Operating Systems

#### Adam Czajkowski

Master of Applied Science

Graduate Department of Electrical and Computer Engineering

University of Toronto

2008

Computer systems are becoming more complex every year, making it exceedingly difficult to understand how well a running system is performing. Various tools have been developed to aid in systems analysis. Some of them can be used to monitor performance and help identify performance bottlenecks. However, they all have limitations, and the scope of their monitoring capabilities is usually limited.

This dissertation presents a new monitoring system called the Kernel Object Viewer (KOV) that makes three primary contributions. First, it can dynamically track important performance metrics using Hardware Performance Counters:

- 1. at object instance-level granularity,

- 2. requiring no changes to the code,

- 3. adding no overhead when monitoring is not required, and

- 4. allowing monitoring overhead to be varied by dynamically changing the sampling frequency.

Second, it implements a system-wide scanning facility which extracts all live processes and their objects. Finally, it implements a novel mechanism to dynamically track lock acquisitions and lock contention.

## Acknowledgements

I would like to express my sincere gratitude to my thesis supervisor, Professor Michael Stumm. I am deeply grateful for the guidance, support, and encouragement he has provided me with over the years. Throughout the course of my research his advice has always been invaluable, and his extensive knowledge and expertise have made this research possible.

I would like to thank my family, Dr. Gregory Czajkowski, Tatiana Czajkowska and Tomasz Czajkowski, for their constant support and inspiration.

I would also like to acknowledge The Edward S. Rogers Sr. Department of Electrical & Computer Engineering for its financial support.

# Contents

| 1        | Introduction |        |                                               |    |  |  |  |  |

|----------|--------------|--------|-----------------------------------------------|----|--|--|--|--|

|          | 1.1          | Existi | ng Monitoring Software                        | 3  |  |  |  |  |

|          | 1.2          | KOV    | Overview                                      | 6  |  |  |  |  |

|          | 1.3          | Contri | ibutions                                      | 9  |  |  |  |  |

|          | 1.4          | Outlin | ne                                            | 9  |  |  |  |  |

| <b>2</b> | Bac          | kgroui | nd                                            | 10 |  |  |  |  |

|          | 2.1          | Perfor | mance Monitoring Unit                         | 10 |  |  |  |  |

|          |              | 2.1.1  | PMU Limitations                               | 13 |  |  |  |  |

|          |              | 2.1.2  | Software Multiplexing of Hardware Performance |    |  |  |  |  |

|          |              |        | Counters                                      | 15 |  |  |  |  |

|          | 2.2          | Instru | mentation Techniques                          | 17 |  |  |  |  |

|          |              | 2.2.1  | Static Instrumentation                        | 17 |  |  |  |  |

|          |              | 2.2.2  | Dynamic Instrumentation                       | 18 |  |  |  |  |

|          | 2.3          | Instru | mentation Tools                               | 22 |  |  |  |  |

|          |              | 2.3.1  | KLogger                                       | 23 |  |  |  |  |

|          |              | 2.3.2  | K42's event log                               | 23 |  |  |  |  |

|          |              | 2.3.3  | Linux Trace Toolkit                           | 24 |  |  |  |  |

|          |              | 2.3.4  | Lockmeter                                     | 25 |  |  |  |  |

|          |              | 2.3.5  | KernInst                                      | 25 |  |  |  |  |

|   |      | 2.3.6                   | Kprobes                                        | 26 |

|---|------|-------------------------|------------------------------------------------|----|

|   |      | 2.3.7                   | DTrace                                         | 26 |

|   |      | 2.3.8                   | SystemTap                                      | 27 |

|   |      | 2.3.9                   | JIFL                                           | 27 |

|   |      | 2.3.10                  | PAPI                                           | 28 |

|   | 2.4  | K42                     |                                                | 29 |

|   |      | 2.4.1                   | Design Features                                | 29 |

|   |      | 2.4.2                   | Clustered Objects                              | 31 |

|   |      | 2.4.3                   | Memory Management                              | 35 |

| 3 | Syst | tem De                  | esign and Implementation                       | 38 |

|   | 3.1  | Overvi                  | iew                                            | 38 |

|   | 3.2  | Monito                  | oring Infrastructure                           | 39 |

|   |      | 3.2.1                   | Kernel State and Performance Monitoring Module | 41 |

|   |      |                         | Object Scan                                    | 41 |

|   |      |                         | Performance Monitoring Unit                    | 43 |

|   |      |                         | Spin locks                                     | 47 |

|   |      |                         | Software Instrumentation                       | 50 |

|   |      | 3.2.2                   | Data and Control Interface                     | 52 |

|   | 3.3  | Graph                   | ical User Interface                            | 53 |

|   | 3.4  | 3.4 Limitations         |                                                | 60 |

|   | 3.5  | Chapte                  | er Summary                                     | 61 |

| 4 | Exp  | Experimental Evaluation |                                                |    |

|   | 4.1  | •                       |                                                | 63 |

|   |      | 4.1.1                   | Apache Workloads                               | 64 |

|   |      | 4.1.2                   | SPECjbb2000 Workloads                          | 66 |

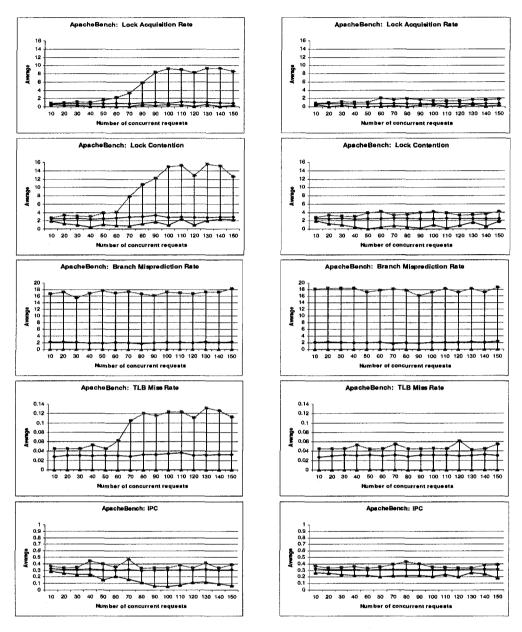

|   | 49   | Experi                  | mental Results                                 | 67 |

|    |       | 4.2.1  | Apache loaded with ApacheBench | • | 68  |

|----|-------|--------|--------------------------------|---|-----|

|    |       | 4.2.2  | Apache loaded with SURGE       |   | 74  |

|    |       | 4.2.3  | SPECjbb2000                    |   | 78  |

|    | 4.3   | Overh  | ead Considerations             | • | 83  |

|    |       | 4.3.1  | Sampling Frequency             | • | 89  |

|    | 4.4   | Correc | etness of Measurements         |   | 92  |

|    |       | 4.4.1  | PMU                            |   | 92  |

|    |       | 4.4.2  | Software Instrumentation       |   | 96  |

| 5  | Con   | cludin | g Remarks                      |   | 97  |

|    | 5.1   | Lesson | ns Learned                     |   | 98  |

|    | 5.2   | Future | e Work                         |   | 100 |

| Bi | bliog | graphy |                                |   | 101 |

# Chapter 1

## Introduction

Computer systems, consisting of both hardware and software, are becoming more complex every year. For example, processor architectures have added deeper pipelines, multi-level caches, branch predictors, multiple cores, multi-threading, and other features in recent years. Often, multiple processing units are combined to form a single multiprocessor. Operating systems, which provide a layer of isolation between applications and the raw hardware, have added support for multi-processor architectures, enhanced security, numerous optimizations within the file system and memory management subsystems, as well as support for many new devices.

This increased complexity makes it exceedingly difficult to qualitatively and quantitatively understand how well a running system is performing. Moreover, for performance-critical applications it is equally challenging to deduce the effects of code (or design) modifications on performance (i.e., whether the changes significantly affect branch mispredictions or cache miss rates, or whether the changes significantly affect the page miss rate or load balancing). Similarly, a programmer might want to identify performance bottlenecks and their precise causes with the goal of optimizing the code, yet this is becoming more difficult as the complexity of the system substrate increases. Likewise, operating system designers will want to identify performance bottlenecks under different

workloads.

Various tools have been developed to aid in systems analysis. Some of them can be used to monitor performance and help identify performance bottlenecks. However, they all have limitations, and the scope of their monitoring capabilities is usually limited to a particular layer. For example, the VTune monitoring tool monitors solely at the hardware level by presenting information gathered from hardware performance counters. Another performance monitoring tool, called GNU gprof, requires recompilation in order to monitor a target application, and thus is not fit for production environments. Similarly, neither of these tools simultaneously monitors a target application's performance as well as kernel-level structures (e.g. memory manager) which serve this application. In cases where an application performs a significant amount of I/O or network operations, a combined user-level and kernel-level look at performance is more comprehensive and thus more useful at accurate and precise identification of performance bottlenecks.

In this dissertation we present the design and implementation of the Kernel Object Viewer (KOV), an object-oriented monitoring system which

- 1. combines hardware-level and software-level monitoring capabilities,

- 2. simultaneously monitors user-level and kernel-level software components,

- 3. can attribute performance bottlenecks to specific object-level code segments, and

- 4. provides sophisticated visualization support to aid in system performance debugging.

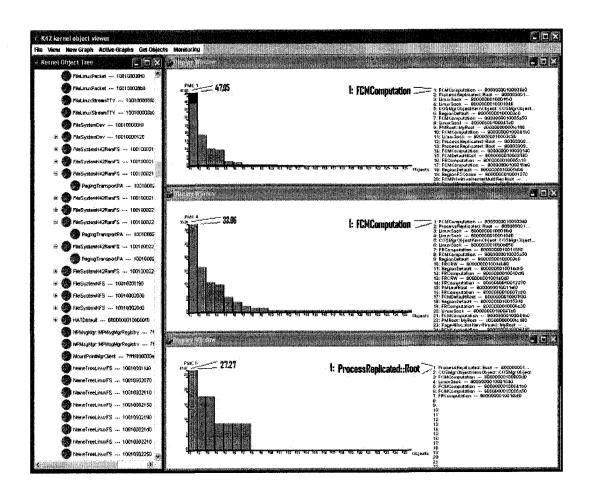

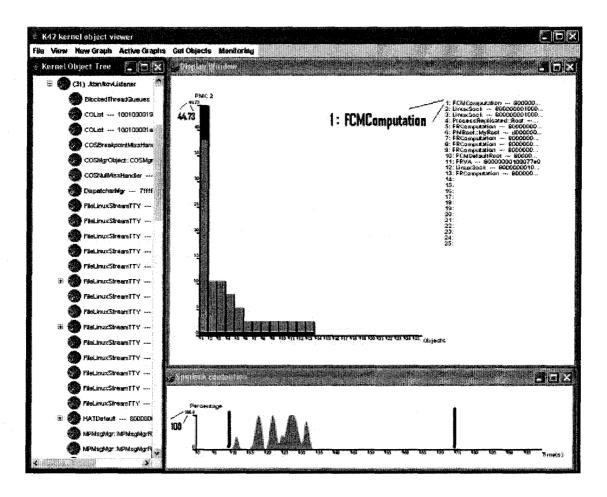

We used KOV to analyze the performance of different applications on the K42 operating system. We demonstrate how KOV identifies hot objects in the operating system, and how KOV provides useful visual information by showing the rate of hardware events on a per-object basis.

## 1.1 Existing Monitoring Software

Existing performance monitoring tools can be classified into two categories, called static and dynamic instrumentation, based on the type of instrumentation used to quantify performance. Static instrumentation tools augment the original binary with extra instrumentation off-line. In contrast, dynamic instrumentation tools are capable of plugging in and removing monitoring functionality seamlessly at runtime. There exists a plethora of commercial performance monitoring tools available for multiple operating system platforms, as well as open-source alternatives available for several operating systems such as Linux and Solaris. One can acquire proprietary tools, such as Intel VTune, Windows System Performance Monitor, and LivePerf, or download open-source alternatives such as GNU gprof and InfraRED.

We provide a brief overview of some of these tools and highlight their current limitations.

#### Intel VTune

VTune is a sampling profiler developed by Intel and designed for generic performance monitoring of applications running on Intel hardware [36]. VTune uses hardware performance counters to monitor processor events (and thus the limitation to Intel hardware), or simply to provide a CPU utilization breakdown on a per-function basis. VTune uses the program counter (PC) value obtained automatically from each hardware performance counter event to trace back the aforementioned hardware events to specific segments of code.

#### Windows Performance Monitor

The Windows Performance Monitor tool is freely available for Windows 2000, Windows Server 2003, and Windows XP [28, 33, 44]. It enables the user to gather operating system level data such as number of memory pages swapped to disk, time spent executing each

process, or disk usage. Each performance metric is attributed by this tool to a physical resource at coarse granularity. For example, execution time is attributed to "processor", and disk usage to "physical disk". Data are presented at process granularity versus time for each of the characteristics being monitored. All performance monitoring data gathered with this tool are also displayed in a graphical user interface (GUI) provided with the tool. This tool exclusively relies on performance gathering capabilities incorporated into the Windows operating system.

#### LivePerf

The LivePerf performance monitoring tool is a performance data gathering and displaying facility [27]. A GUI collects and displays data gathered from applications using their built-in performance gathering capabilities. LivePerf does not contribute any of its own monitoring capability, but rather relies on the targeted application's API to interface with and gather data from it. It currently supports gathering data from Websphere, SQL Server, DB2, Oracle, Unix and Windows operating system, Apache and IIS webservers, .NET and J2EE applications. In addition, LivePerf enables logging and replaying of different statistics.

#### GNU gprof

GNU gprof is a tool that allows a user to learn where a program spends its time executing, which functions were called and how many times [21, 31]. With this information it is possible to deduce which portions of a program are slower than expected. However, gprof does not provide the reason for the slowdown. The type of information generated by gprof can single out "hot" functions, and thus allows the user to focus their efforts. Although somewhat useful for simple programs, gprof is not able to instrument multithreaded applications. As such, the utility of this tool is limited to simple programs, and only provides course-grained timing measurements at function-level granularity.

#### **InfraRED**

InfraRED is a tool for monitoring performance of J2EE applications and diagnosing performance problems [24]. It collects metrics on various aspects of an application's performance and makes it available for quantitative analysis of the application. InfraRED uses Aspect-Oriented Programming (AOP) to inject performance monitoring code between distinct parts of the application, as defined by the AOP paradigm [25]. InfraRED is a comprehensive monitoring tool for programs written in Java, however it only utilizes software data gathering techniques (as provided by the instrumentation inserted between the AOP blocks).

#### Generic Tools

It is not always necessary to buy or download a performance monitoring tool. Operating systems typically provide useful utilities with the original distribution. For example, the Linux or Solaris operating systems contain vmstat, iostat, netstat, and other simple tools. Although these tools can provide statistics on virtual memory, disk access, processor activity (in the case of vmstat), or I/O (iostat), the results are aggregated for the system as a whole. These tools do not generally identify the source of a particular bottleneck. Nevertheless, such tools can be helpful at identifying the existence of a performance problem, but they are not specific enough for performance debugging.

#### Limitations of existing monitoring tools

The performance monitoring tools presented above gather performance data either at the hardware level or at the software level, but not both. Only a few of the tools map potential performance issues back to the code segments that incur them. Intel's VTune is one of the few, as it is capable of tracing hardware events back to the lines of code that caused them. However, none of the tools directly support object-oriented code by mapping potential performance bottlenecks back to specific object instances. Yet this

information could be useful. By identifying which object instance causes a performance bottleneck, it becomes easier to perform accurate and precise performance debugging.

Not all of the above tools have a Graphical User Interface (GUI). The advantage of having a GUI in a performance monitoring tool is clear. Clarity in displaying the data makes it easier to interpret, and well designed graphs can highlight important trends.

## 1.2 KOV Overview

This dissertation describes the design and implementation of a performance monitoring tool called the Kernel Object Viewer (KOV) that addresses the limitations described above. KOV is comprised of two main parts connected by a common interface.

- 1. An ensemble of static and dynamic instrumentation together with a performance data gathering module located in the operating system kernel, and

- 2. A graphical user interface which displays the performance data at process and object-level granularity.

KOV was implemented for K42, an object-oriented operating system for shared memory multiprocessors. KOV uses both hardware-level and software-level monitoring capabilities. Hardware performance counters (HPCs) are used to obtain information on hardware-level events (e.g. TLB misses, IPC rates), and software modifications enable system analysis (e.g. by obtaining a list of live objects), as well as provide information on software-level metrics (e.g. sleep lock queue lengths, object invocation counts).

HPCs can be configured to generate events periodically at a user-defined frequency. As such, the KOV monitoring system allows for fine-grained, variable-overhead performance readings of any hardware-level event being monitored. Using HPCs allows this performance monitoring technique to be fully dynamic with respect to a target application or OS subsystem, because monitored application or system-level code is not modified.

The benefit of this form of dynamic instrumentation is that it incurs no overhead when turned off, and can be enabled or disabled at any time without restarting the system or target application.

Software-level performance gathering capabilities have been implemented with direct source-code modifications. Object classes were extended to allow for a scan of live objects, as well as to provide a hierarchical relationship with other objects. When an object is scanned, it responds with a list of other objects it refers to, and thereby positions itself with respect to other objects within the system's hierarchy. Although this static instrumentation cannot be removed without recompiling the system, it is outside of the critical path, and is in fact not invoked outside the scope of the KOV performance monitoring system. Other software-level instrumentation code enables logging of object invocations, as well as measurement of sleep lock queue lengths. This code introduces overhead to the system, even when disabled, and is quantified in Section 4.3.

KOV collects performance data from both kernel-level and user-level components. HPCs can be configured to count hardware events generated by the execution of either kernel-level code, user-level code, or both. Likewise, the object scan initiated by KOV is on a per process basis, and thus the scan can include the kernel process and arbitrarily many user processes. Software-level monitoring of sleep lock queue lengths is also available for both user-level and kernel-level code. Since the sleep lock instrumentation is part of the class definition used to implement sleep locks (this class is provided as a part of libc), any code which instantiates this object class will enable itself to be monitored by KOV.

For object-oriented software, it is particularly important to be able to track performance at object instance granularity. Because an object instance encapsulates data specific to the instance, two objects of the same class may experience observably different performance behaviour even though they share the same code base. As a result, optimizations on an entire class may improve performance for some instances but worsen performance for other instances. Some object-oriented systems support dynamic optimization at object instance granularity, such as K42's hot-swapping facility [8], where individual object instances may be replaced dynamically at run-time by an instance of another (related) class providing the same functionality but with a different implementation.

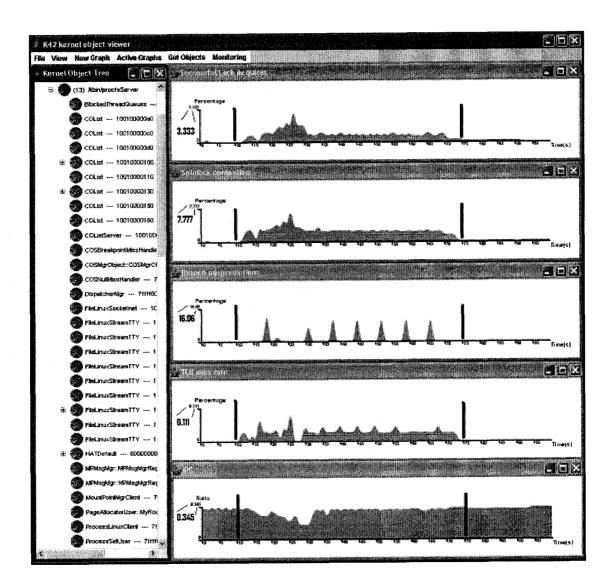

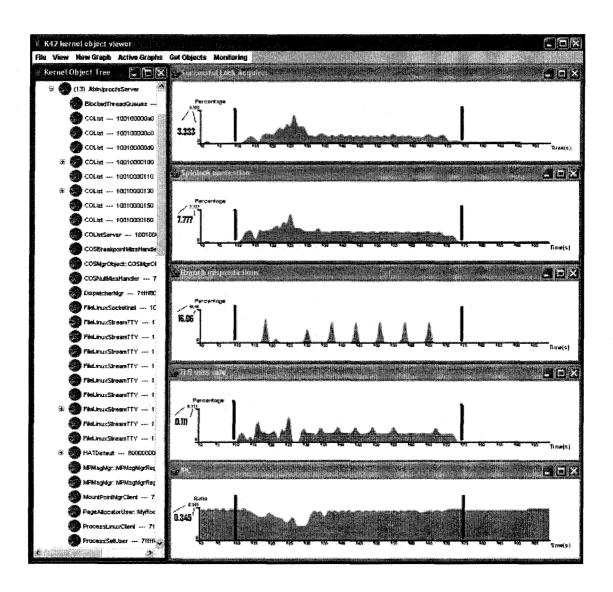

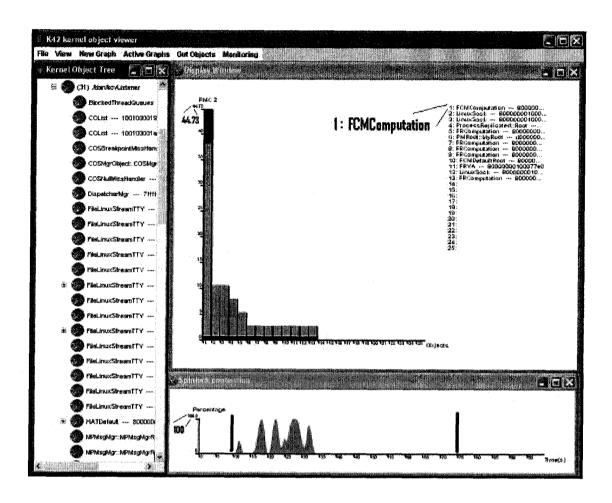

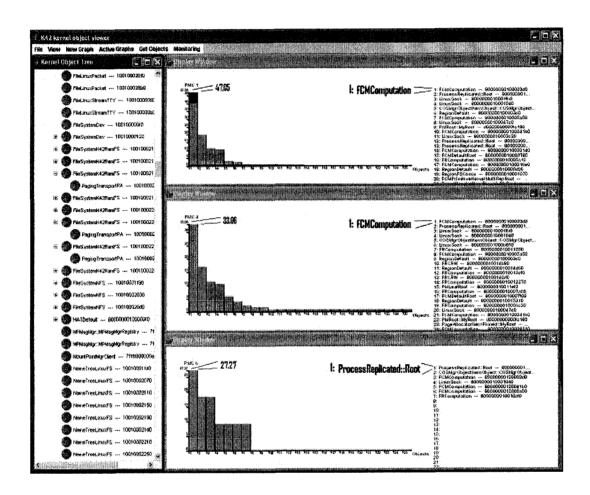

The live representation of the system, as well as all performance data gathered, are shown in a graphical user interface. The aforementioned object hierarchy is shown in the form of a tree, and performance bottlenecks are shown either directly on the tree (by highlighting the problem objects), or in one of many types of graphs. By displaying performance data in a KOV graph, the user can depict behaviour over time for a specific object instance, or the system as a whole. It is also possible to display all the objects with their attributed percentage of total data.

We have implemented KOV on the K42 operating system running on PowerPC hardware. KOV obtains data from the architecture's Performance Monitoring Unit (PMU) using the statistical PMU sampling system we developed as an extension of Azimi et al [11]. Currently, we use a GUI to display the performance statistics gathered and updated in real-time. The GUI displays a hierarchical tree of object instances and performance statistics in two ways: (i) object instances are displayed ordered by severity of performance impact, and (ii) performance statistics for any object instance are displayed over time. Using the GUI, it is possible to observe correlations between different performance metrics (such as correlation between lock contention and TLB misses). Ultimately, we envision a scenario where dynamic run-time optimizers will obtain the statistics from the monitoring infrastructure and use object hot-swapping [8] to improve system performance.

## 1.3 Contributions

In this dissertation we make three primary contributions. First, we describe a performance monitoring infrastructure we have developed, called the Kernel Object Viewer (KOV), that dynamically tracks important performance metrics using Hardware Performance Counters:

- at object instance-level granularity,

- requiring no changes to the code,

- adding no overhead when monitoring is not required, and

- allowing monitoring overhead to be varied by dynamically changing the sampling frequency.

The second contribution of this dissertation is a comprehensive, system-wide scanning facility which extracts all live processes and their objects. In addition, the scanning capabilities of KOV encompass both the kernel process and user processes, and cause no overhead when not in use.

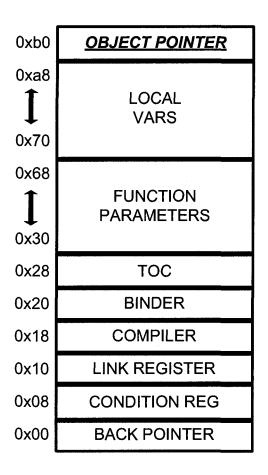

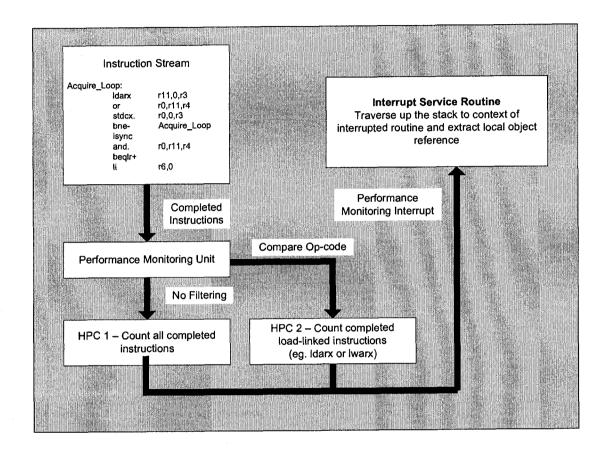

The third contribution of this dissertation is a novel mechanism to track lock acquisitions and lock contention in a way that requires no changes to the code. To gather statistics on locks, we use PMU features of IBM PowerPC processors to count occurrences of load-linked and store-conditional instructions and then walk the stack to tie lock events to specific object instances.

## 1.4 Outline

The rest of this dissertation presents background information relevant to KOV in Chapter 2, the design and implementation of our tool in Chapter 3, followed by an experimental evaluation of KOV in Chapter 4, and concluding remarks in Chapter 5.

## Chapter 2

# Background

This chapter presents background material to allow a better understanding of the remainder of this dissertation. Specifically, we present a brief overview of the Performance Monitoring Unit, provide a more in-depth explanation of static and dynamic software instrumentation, and conclude by describing the structure of the K42 operating system, the platform upon which the Kernel Object Viewer (KOV) prototype was evaluated.

## 2.1 Performance Monitoring Unit

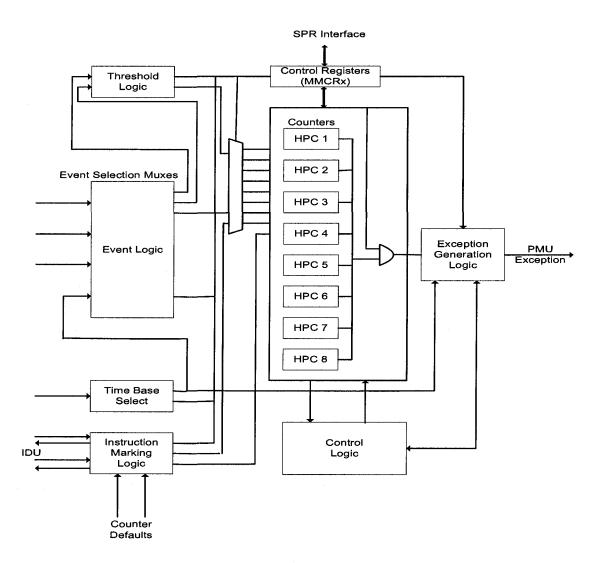

Today's complex, speculative, out-of-order execution cores usually come with sophisticated Performance Monitoring Units (PMUs). A modern processor will have a PMU that supports memory hierarchy profiling, instruction sampling, functional unit event sampling, and potentially other implementation dependent functionalities. An example architecture of a performance monitor is shown in Figure 2.1. A Hardware Performance Counter (HPC), accumulates occurrences of a distinct hardware event, chosen by a series of multiplexers which lead to the counters block in which the actual HPCs reside.

A typical PMU will have many HPCs (e.g. PowerPC 970FX has eight), where a single HPC can be configured to count only one type of event from a subset of all hardware events at any given time. The size of this subset of events available for monitoring by

each HPC is determined by multiplexing logic leading up to the counters block, as shown in Figure 2.1. Although actual implementation details vary depending on the specific processor architecture, it is sufficient to point out that events are chosen by a network of multiplexers comprised of several stages.

In the platform used to develop the prototype described in this dissertation, specifically the PowerPC 970FX, three stages of multiplexers choose which events end up being counted by each HPC. Given that the total number of events that could potentially be counted on this architecture is roughly 500, from a hardware implementation point of view, it is too costly to have eight, 500-way multiplexers to allow each and every HPC to count any event. Consequently, the cheaper three-stage network of multiplexers allows each HPC to count only a specific subset of all hardware events. By assigning each HPC to a different set of hardware events, it is then possible to span all events by using all available counters. On the PowerPC 970FX there is some overlap between the sets of events each counter can monitor, consequently giving the programmer some flexibility in terms of configuration parameters.

Functionally, a Hardware Performance Counter is a register which accumulates the occurrences of hardware events. A software program, running in kernel-space, can directly read from, and write to, all HPC registers.

A simple usage model for performance monitoring involving the use of HPCs could be realized by periodically polling (reading) all counters to obtain an update of all event counts being monitored. Since polling is considered an inefficient programming technique, due to the constant overhead associated with periodic reads, the PMU also allows counters to generate interrupts.

The use of PMU interrupts for performance monitoring is a two step process. The first step involves configuring a set of Special Purpose Registers (SPRs) on the PMU (registers referred to as MMCRx). A software program, running in kernel-space, will write to these SPRs values that will determine when a PMU interrupt is to be generated,

Figure 2.1: Performance Monitor Architecture for the PowerPC 970FX RISC Microprocessor. Hardware Performance Counters (HPCs) receive signals from a variety of sources, ranging from a thresholder, event generator, time base selector, instruction marker, processor functional units (i.e. arithmetic-logic unit), and others. The crucial link between the hardware and software layer is the Exception Generation Logic. Based on a set of flags set in Special Purpose Registers (SPR), an interrupt will be generated once any of the counters meets a pre-defined condition set in performance monitor specific control registers (MMCRx).

and which HPCs are to generate interrupts. PMU interrupts can be generated when a specific HPC overflows, or periodically after executing a specified number of processor cycles.

The second step of using PMU interrupts for performance monitoring involves the Interrupt Service Routine (ISR), which is called whenever a PMU interrupt occurs. The ISR is a software program which runs at exception-level and is capable of performing low-level tasks, such as reading from, and writing to, SPRs and HPCs, or saving data to software buffers for later analysis. The programmer must be careful when writing an ISR, because an exception (such as a page-fault) when executing an ISR will cause the system to crash. As such, an ISR should only perform simple tasks.

A simple usage model for performance monitoring involving the use of interrupts could consist of setting one HPC to generate an interrupt every 10,000 branch misprediction events, and the aforementioned ISR to read the HPC value and save it in a dedicated software buffer. Another program could subsequently read this data from the buffer and use it for performance analysis.

In conclusion, HPCs allow counting of detailed micro-architectural events in the processor [4, 17, 18, 40], enabling new ways to monitor and analyze performance. There has been a considerable amount of work done using HPCs to explore the behaviour of applications, as well as to identify performance bottlenecks resulting from excessively stressed micro-architectural components [3, 19, 42].

#### 2.1.1 PMU Limitations

Most microprocessor PMUs offer a limited number of HPCs. For instance, the IBM POWER4 and PowerPC970 provide eight HPCs, the POWER5 has six per SMT (two of which are hard-wired), Intel Itanium II has four generic HPCs and five registers for holding instruction and data address samples, and the AMD Athlon has four generic HPCs. In addition to the limited number of HPCs, there are often restrictions on the

combinations of hardware events that the HPCs can count, as previously mentioned for the PowerPC970. Other architectures have similar limitations. For instance, although Intel P4 and Xeon have 18 HPCs, they are divided into nine groups, each of which can only count events from a specific subset of 48 available hardware events.

In many performance monitoring scenarios, several low-level hardware events must be counted simultaneously to obtain information of interest. For instance, to obtain the L1 data cache miss rate on an IBM POWER4 processor, at least four separate events must be counted (L1 load misses, L1 store misses, L1 loads, and L1 stores). Also, usually two HPCs have to be dedicated to counting processor cycles and instructions retired to provide context for other data being gathered. For example, one thousand branch mispredictions per one million retired instructions is less significant than one thousand branch mispredictions per fifty thousand retired instructions (a 20x difference). On a processor such as the AMD Athlon, that leaves only two unused HPCs to gather other hardware events. These two remaining HPCs are not sufficient to count L1 load misses, L1 store misses, L1 loads, and L1 stores.

Even if one had eight counters available, such as on the PowerPC 970FX, and could fit all the L1 events as well as processor cycles and retired instructions in a single PMU configuration, there is other information available which, if monitored, could aid in accurate and precise performance debugging. It might be desirable to also monitor L2 cache misses, L3 cache misses, branch mispredictions, TLB misses, instruction mix (integer/floating point), instruction cache misses, or other events that are important for obtaining a complete picture of application and system performance depending on the workload being explored.

# 2.1.2 Software Multiplexing of Hardware Performance Counters

To address the need for a large number of hardware counters to enable comprehensive hardware event monitoring, Azimi et al proposed and implemented a system which dynamically multiplexes the set of hardware counters by using fine-grained time slices [11]. The programming interface component takes a set of events to be counted as input and automatically assigns them to a number of HPC groups such that in each group there are no conflicts due to PMU constraints. The sampling engine assigns each group a fraction of cycles out of the total sampling period. At the end of each HPC group's time slice, the sampling engine automatically assigns another HPC group to the PMU. The value that is read from an HPC is scaled up linearly as if that group was active during the entire period. As a result, the user's program (e.g. a run-time optimizer) is presented with more logical counters than actually exist in the underlying processor architecture.

Some types of events exhibit more volatile behaviour than others. For example, L1 miss rates change dramatically depending on the current workload, whereas the number of completed processor cycles does not. To capture greater variations in system performance it becomes necessary to increase the sampling frequency for those events which change more often. As defined by the Nyquist rate, the HPC sampling rate must be at least twice the frequency of changes within the data being monitored (e.g. if L1 miss rate changes every 100ms, HPCs must sample at least every 50ms to accurately measure event transitions).

The multiplexing system introduced by Azimi et al can easily be programmed to favour certain HPC groups by using their configuration for longer periods of time. This is accomplished by allocating multiple time slices to the group, rather than just one in the default case. This PMU multiplexing scheme is analogous to time-sharing a CPU amongst various processes. Moreover, the accuracy may differ for different hardware

events with the same share size. A default share assignment scheme might be overridden by explicit requests from a user interested in closely monitoring a specific hardware event, such as L1 miss rates.

With multiplexing, time is usually measured in terms of CPU cycles. Therefore, one counter in each HPC group is reserved to count CPU cycles. The use of cycle counters as timers allows the user to define arbitrarily fine time-slices down to a few thousands of cycles. Another metric that can be used to define HPC group share sizes is the number of instructions retired. The main advantage of instruction-based multiplexing is that the HPC group share sizes are aligned more closely with the progress of the application. Actual share sizes will differ in terms of real time depending on the amount of available instruction level parallelism (ILP) in the application currently running.

Sampling introduces inaccuracies in measurement. A pathological case for the multiplexing engine is the existence of a large number of short-lived bursts of a particular hardware event. If the burst time is shorter than a particular number of cycles, the HPC that counts that hardware event might be inaccurate because the PMU actually counts the event only in a fraction of the total time slice, and thus it may miss short-lived bursts. However, given that most applications will go through several execution phases, each longer than a time slice, the occurrence rate of hardware events is stable in the common case. Experimental results presented by Azimi et al demonstrate that the statistical distance between the sampled and real rates of hardware events is small in most cases.

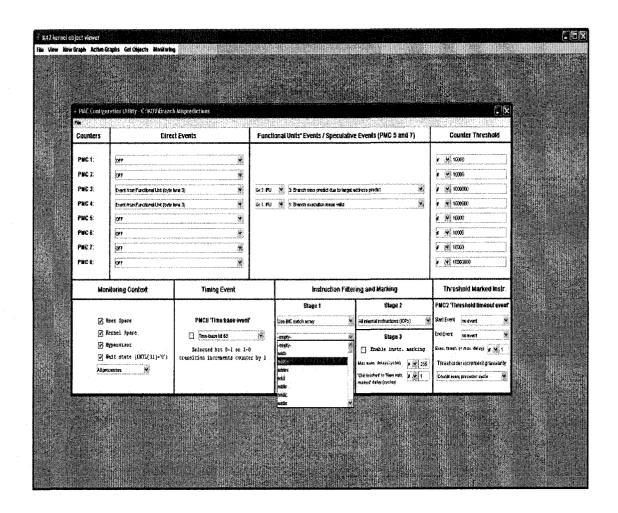

KOV makes extensive use of Azimi's HPC multiplexing infrastructure. KOV provides a Graphical User Interface (GUI) for configuring the PMU on the PowerPC 970FX. Each set of configuration parameters can be saved in a config file, such as "TLB misses" or "Branch mispredictions". The GUI logic prevents the user from choosing conflicting events within a single configuration. The user can subsequently send both the "TLB misses" and "Branch mispredictions" configurations to the multiplexing infrastructure

and specify the percentage of time each configuration is to be used within the PMU. The multiplexing infrastructure automatically switches between the two different configuration parameters.

## 2.2 Instrumentation Techniques

To address the growing need for comprehensive performance monitoring systems, a variety of tools have emerged that can loosely be classified into one of two categories depending on the type of instrumentation being used to quantify performance. Static instrumentation systems can be characterized by the fact that they augment the original binary with extra instrumentation off-line. In contrast, dynamic instrumentation is defined by the capacity to plug in and remove monitoring functionality seamlessly while the system is running. Examples of static instrumentation systems include: KLogger[20], K42's event log[45], Linux Trace Toolkit[46], and Lockmeter[15], and examples of dynamic instrumentation systems include: KernInst[43], Kprobes[32], DTrace[16], SystemTap[34], JIFL[30], and PAPI[14].

### 2.2.1 Static Instrumentation

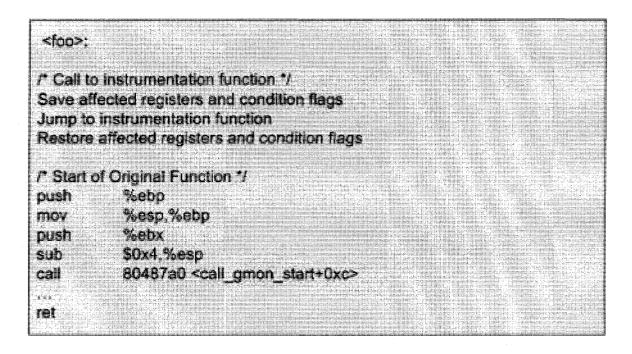

Static instrumentation can be the done via direct source code modifications such as with Paragon[37] and K42's event log[45] or by instrumenting the binary off-line as is done with Atom[41]. Although not requiring source code in the latter case does increase the system's utility, this type of approach still suffers from the need to restart the target application when new instrumentation is added or removed. Similarly if the OS is being instrumented, a full system reboot is necessary. An example of how static instrumentation could be done is shown in Figure 2.2. When adding static instrumentation, the user has unlimited freedom in where and how to instrument. However, static instrumentation incurs constant overhead and requires recompilation to remove it completely.

```

long int invocation_count;

void foo()

{

/* Source code instrumentation counts number of function calls */

Invocation_count++;

/* Start of Original Function */

...

}

```

Figure 2.2: An example implementation of static instrumentation. Since the system is not running when adding this type of instrumentation, the user has unlimited freedom in where and how to instrument. Unfortunately, this approach incurs constant overhead and requires recompilation to remove it completely.

As such, static instrumentation is inappropriate for production environments in which restarts represent an unacceptable lapse in service. Moreover, static instrumentation does not lend itself well to the analysis of systemic problems or emergent misbehaviour [29], which only appears after prolonged and continuous system operation, because it implies having all the necessary functionality already in place. This is difficult to achieve in practice because the nature of an emergent problem is not know during development.

## 2.2.2 Dynamic Instrumentation

Dynamic instrumentation on the other hand entails no off-line modifications to the target application or OS subsystem being monitored. Instead, the monitoring tool inserts dynamic instrumentation by modifying a target application's executable code in memory. Alternatively, hardware generated events can be used to interrupt a currently executing program to take snapshots of its current state. These are only a few techniques of dynamic instrumentation. Because dynamic instrumentation is not as direct as static instrumentation, it is also much richer in terms of the assortment of existing approaches,

and currently remains an active field of research.

Within the scope of dynamic instrumentation, one can consider software and hardware approaches. The former consists of two main groups, probe and just-in-time (JIT) based paradigms, whereas the latter utilizes hardware performance counters (HPCs). Due to the inherent level of abstraction at the software and hardware level, some information lends itself better to either one of the two approaches. For example, when interested in the behaviour of a scheduling algorithm, hardware has no notion of processes and thus is not a good choice. Alternatively, when monitoring cache misses, a program does not experience them directly, and thus HPCs are a better solution.

The first dynamic instrumentation technique to have emerged is the probe-based approach. It works by overwriting instructions in the original program with trampolines to instrumentation code. Effectively, only one instruction is overwritten whereas the actual instrumentation function, which resides in a different location, can be arbitrarily large. Since the overwritten instruction isn't executed once it is overwritten, its effects have to be duplicated by the instrumentation function, to ensure correct execution of the original program.

Probes can be implemented in a straight-forward way on fixed-length instruction set architectures (ISAs), such as Sun's UltraSparc, by inserting jump instructions to the relevant code at each instrumentation point; however, on variable-length ISAs, such as the popular Intel x86 and AMD x86-64, probes have to be implemented with trap instructions [43]. An example of what such an instrumented program would look like is shown in Figure 2.3. At each instrumentation point, execution of the trap instruction causes an exception handler to be dispatched. The handler must then determine what type of instrumentation is needed at that point. The overhead of such traps can be substantial, and it can make comprehensive and fine-grained instrumentation unfeasible [30].

Just-In-Time (JIT) based dynamic instrumentation was developed to address some

Figure 2.3: An example implementation of dynamic instrumentation using the probebased approach. In order to keep the binary the same size, and thus preserve the correctness of static branch targets, an existing instruction is overwritten with a trap. The resulting interrupt will call the required instrumentation function based on the trap's address and compensate for the overwritten instruction with extra code.

of the most prevalent shortcomings of the probe-based techniques. With this approach, execution is redirected to a runtime system at the entry of a section of code that is to be instrumented. A JIT compiler creates a duplicate copy of each basic block of the original code immediately before it is executed, embedding calls to instrumentation routines within it, much as if the instrumentation had been added to the source code and the source recompiled. An example of what this type of instrumentation would look like is shown in Figure 2.4. The resulting instrumented basic blocks are stored in a code cache, from where they are dispatched instead of the original code.

JIT instrumentation can provide better performance and a better usage model than probe-based techniques for large amounts of fine-grained instrumentation. The primary

Figure 2.4: An example implementation of dynamic instrumentation using the JIT-based approach. Since the code being instrumented is in the code cache, and not in the original binary, no existing instructions need to be overwritten. A call to the desired instrumentation function is inserted, as well as necessary instructions required to maintain the original program's state which could be corrupted by instrumentation.

performance advantage stems from the fact that instrumentation can be inserted between instructions. This eliminates the need for expensive trap instructions to redirect execution to instrumentation code on variable-length ISAs. In addition, when using the JIT technique, instrumentation is only inserted into code after it is known that it will execute, thereby eliminating any cost of instrumenting instructions that might not be executed. Furthermore, if the instrumentation code is small enough, it can be inlined directly into the copied basic blocks to eliminate the cost of executing function calls.

From a usability point of view, probe-based instrumentation requires a user to specify the exact locations in the code where instrumentation should be inserted. When instrumentation of a large amount of code is desired, the user is required to manually specify the location of a large amount of probes. Manually inserting hundreds of probes can become erroneous. In contrast, JIT instrumentation requires only entry, and possibly exit, points of the entire code being considered for instrumentation to be identified. Because instrumentation is added as code blocks are discovered, there is no need for a priori identification of possible instrumentation points. For example, when instrumenting a system call with the JIT technique, only the appropriate entry in the system call table needs to be identified. Conversely, the probe-based technique would require the user to go through the entire system call code and specify the addresses for all the probes to be inserted.

## 2.3 Instrumentation Tools

We have described the various techniques available to monitor performance. We now describe several tools that implement these techniques in greater detail. Examples of static instrumentation systems include: KLogger[20], K42's event log[45], Linux Trace Toolkit[46], and Lockmeter[15], and examples of dynamic instrumentation systems include: KernInst[43], Kprobes[32], DTrace[16], SystemTap[34], JIFL[30], and PAPI[14].

## 2.3.1 KLogger

KLogger monitors performance by recording occurrences of kernel events and using hardware performance counters. The logging code is integrated into the kernel and activated at runtime by a special sysctl call using the proc file system. KLogger logs events defined at compile-time, including events such as context switching, recalculation of priorities, forks, execs, changing the state of processes, and others. Logs are stored in a memory buffer (typically 4MB). Every five seconds a daemon stores the contents of the memory buffer to disk, allowing the user to analyze the data at a later time. Because the events monitored by KLogger can only be specified at compile time, and results are not analyzed in real-time, this tool is not usable for performance debugging production systems, where a full system reboot presents an unacceptable lapse in service. In contrast, KOV can change the metrics it monitors while the system is running, and analyzes results in real-time. This flexibility is important to detect bottlenecks immediately as they emerge, and to ease the analysis of a newly identified bottleneck by choosing a more specific set of metrics (e.g. when the memory subsystem becomes a bottleneck, KOV can start monitoring L1 cache, L2 cache, and TLB miss rates immediately upon a user's request).

## 2.3.2 K42's event log

K42's event tracing infrastructure provides for correctness debugging, performance debugging, and performance monitoring of the system [7]. This infrastructure allows for inexpensive and concurrent logging of events by applications, libraries, servers, and the kernel. All events are stored in a special event log which can be read in several ways. This event log may be examined while the system is running, written out to disk, or streamed over the network. Post-processing tools allow the event log to be converted to a human readable form or to be displayed graphically. The types of events that can be monitored by this tracing facility are divided into 64 major classes. Events that are related to a

common purpose are placed in the same major class (e.g. memory management events are grouped into *traceMem*). All classes of events represent actions or positions in the code deemed important by the developer.

Although useful, this infrastructure only monitors components of K42 explicitly identified at compile-time. In addition, when enabled, the tracing facility will log all events from a selected major class of events, regardless of how many events are of interest to the user. This can be problematic if the user is only interested in a small subset of events from a particular class, because there can be a significant amount of data obscuring the results the user is actually interested in seeing. In contrast, KOV only monitors occurrences of events the user has explicitly chosen, avoiding overhead resulting from gathering superfluous data.

#### 2.3.3 Linux Trace Toolkit

The Linux Trace Toolkit (LTT) [46] is a static instrumentation system that allows a user to record and analyze system behaviour. The toolkit is capable of recording information such as CPU time per process, instruction count, fraction of time spent in each function, as well as disk and network I/O statistics. The main contribution of this work is its data collection facility that records and stores pertinent information.

The data collection facility consists of three main components: a trace facility, a trace module, and a daemon. The trace facility functions as a unique entry point to all other kernel facilities. Once an event occurs, the trace facility forwards the event to the trace module. The trace module can then determine the type of event that has occurred. If the event is one identified to be monitored, then the trace module will keep track of it. However, it is possible to configure the trace module to ignore some of the events it was designed to track by the means of an *ioctl* system call. This permits a finer control of the monitoring system.

One drawback of the Linux Trace Toolkit is the fact that it does not attribute per-

formance bottlenecks to specific code segments. Although kernel events caused by the execution of a program can be logged, the LTT does not identify which parts of the program caused these events to occur. In contrast, KOV attributes performance bottlenecks to specific code segments as well as individual object instances.

### 2.3.4 Lockmeter

Bryant and Hawkes designed and implemented a spin lock monitoring infrastructure for the Linux kernel called Lockmeter [15]. Similarly to our approach, Lockmeter can identify problematic spin lock instances with low overhead; however, Lockmeter requires source code annotation of Linux lock macros. In contrast, our approach does not require any direct source code instrumentation of locking structures and is based on exploiting hardware performance counters which enable fine-grained overhead control by varying the sampling frequency.

#### 2.3.5 KernInst

KernInst [43] is a dynamic instrumentation framework designed for debugging, profiling, and application tuning. KernInst was the first to implement probe-based dynamic instrumentation in the kernel. Because it targeted the UltraSparc RISC architecture, which is a fixed-length ISA, KernInst was able to safely implement probes with branch instructions. Although this tool was only evaluated on the UltraSparc, Tamches and Miller proposed using trap instructions for redirecting control on x86. The current code release includes an x86 implementation which uses this trap-based strategy. Due to the high overhead associated with using traps, this tool is only usable with a small set of probes, thus limiting the scope of code being monitored. In contrast, KOV can simultaneously monitor all user and kernel level code with minimal overhead (see Section 4.3).

## 2.3.6 Kprobes

Kprobes [32] uses dynamic instrumentation to insert probes in the form of trap instructions. Using probes, this tool can instrument arbitrary code with extra code to record information. Because execution is redirected to instrumentation routines by means of a trap and hash table lookup, instrumentation is heavyweight. To alleviate this, a patch called Djprobes is currently under development, which allows overwriting some addresses with a 5-byte jump instruction, enabling direct jumps to instrumentation code. The most prevalent shortcoming of this tool is its overhead. In contrast, KOV experiences minimal runtime overhead even when simultaneously monitoring various metrics (see Section 4.3).

#### 2.3.7 DTrace

DTrace [16] is an instrumentation framework for the Solaris operating system, designed for use with production systems. DTrace instrumentation works by inserting jump-based trampolines on fixed-length RISC architectures, but uses the same trap mechanism as KernInst or Kprobes on variable-length ISAs. Anecdotally, DTrace runs quite fast on Sparc architectures, however we expect it would suffer similar overheads as Kprobes on x86 because of the need to use trap instructions. DTrace is also able to dynamically instrument both user and kernel-level code. Because DTrace is intended for use in production systems, it guarantees that user instrumentation cannot cause additional system failures. User-supplied instrumentation code is expressed in a C-like high-level control language which enforces safety. DTrace makes it easy to monitor system resources, allowing system administrators to quickly identify the causes of system sluggishness, or to examine the otherwise unattainable system resources used by software (e.g., the number of I/O requests per second).

This tool suffers from the same drawbacks as KernInst and Kprobes when considering the scope and overhead trade-off associated with performance monitoring. As the

amount of code being monitored increases, so does the number of probes. Consequently, monitoring overhead is directly proportional to the amount of code being monitored. In contrast, KOV can simultaneously monitor all user and kernel-level code with minimal overhead (Section 4.3). KOV controls overhead by varying the accuracy of results when adjusting the PMU sampling frequency, and not by specifying the scope of performance monitoring. Consequently, KOV makes no a priori judgements about which segments of code are expected to perform worse than others, and therefore is more comprehensive in its measurements.

## 2.3.8 SystemTap

The SystemTap project [34] is a joint effort by Red Hat, IBM, Intel, and Hitachi to add an easy to use front-end to Kprobes with functionality similar to DTrace, including the use of a scripting language. Instrumentation scripts can make symbolic references to the kernel, user programs, or included libraries (called 'tapsets'). Scripts are compiled into a kernel module and loaded to start the probes and handlers. Although a stable version of SystemTap is not yet released, some early adopters have found it useful. SystemTap currently uses Kprobes for low-level instrumentation. Consequently, the performance trade-offs when compared to KOV are similar to Kprobes.

#### 2.3.9 **JIFL**

The JIT Instrumentation Framework for Linux (JIFL) [30] was the first instrumentation technique to instrument kernel code. JIFL was designed to alleviate the high performance cost associated with probe-based instrumentation techniques, such as Kprobes. JIFL shows the feasibility and desirability of kernel-based JIT instrumentation for the Linux kernel on an SMP machine. JIFL works by inserting instrumentation code directly into a duplicate copy of the original code. By embedding calls to instrumentation routines within the duplicate copy of the original code, the usual overhead associated with traps in

the probe-based approach is eliminated. Using JIT instrumentation, JIFL outperformed Kprobes, at both micro and macro levels, by orders of magnitude when applying medium-and fine-grained instrumentation.

Although superior to other dynamic instrumentation tools in terms of performance, JIFL incurs considerable memory overhead associated with duplicating the original code. As such, the scope of performance monitoring with JIFL is limited. In contrast, KOV can monitor all user and kernel-level code simultaneously with minimal overhead (see Section 4.3).

### 2.3.10 PAPI

PAPI [14] is a public domain tool that is implemented on many platforms. Its main emphasis is on platform-independence rather than efficiency. The portable interface is implemented in software, and as a result it may incur significant overhead in some scenarios. PAPI also implements Hardware Performance Counter (HPC) multiplexing at user-level. A fine-grained timer is used as a means for a HPC group switch. The timer sends a signal to the process that has requested a multiplexed set of hardware events. A major limitation of this approach is that the sampling granularity must be large due to the large overhead of an HPC group switch, which requires a system call. As a result, the sampling error may become high for some applications, where a high sampling frequency is required to obtain an accurate measure of performance. In contrast, KOV has been shown to achieve accurate results while incurring minimal overhead (see Section 4.3.1). This advantage is largely the consequence of the fact that KOV uses a kernel module to interact with the PMU, and thus avoids the associated system call overhead.

## 2.4 K42

K42 is a high performance, open source, general-purpose research operating system (OS) kernel designed for cache-coherent multiprocessors. This OS was designed to address scalability across server systems aimed at utilizing small to very large-scale multiprocessors. Towards this end, primary focus was placed on achieving a high degree of spatial and temporal locality in code and data. K42 features a modular, object-oriented structure where each resource or entity is managed by a separate object instance [10]. Currently K42 runs only on the PowerPC architecture, and supports both the Linux Application Programming Interface (API) and Application Binary Interface (ABI).

## 2.4.1 Design Features

The K42 design team's initial goal was to start with a clean slate and examine what system structures were needed to achieve excellent performance in a scalable, maintainable, and extensible system [26]. In order to gain traction with the community, developers aimed at fully supporting existing applications. To this end, K42 was made fully Linux API and ABI compatible [6].

A large part of K42's design was oriented around providing an easily extensible infrastructure to tailor to emerging application requirements while at the same time providing an attractive systems research platform [38]. Various research groups have, using K42, explored new approaches in memory management, scheduling, inter-process and intra-process communication, event management, file systems, performance monitoring, scalable data structures, and dynamic adaptation [8, 13, 26, 39].

The entire operating system was designed using an object-oriented structure. Each virtual resource (e.g., virtual memory region, network connection, file, process) and physical resource (e.g., memory bank, network card, processor, disk) is managed by its own object instance. Each object encapsulates the meta-data necessary to manage the re-

source as well as the locks necessary to manipulate the meta-data. Therefore, global locks, global data structures, and global policies were entirely avoided. K42's modular design enables developers to confine the impact of their changes within a fixed set of modified components, thereby greatly simplifying the debugging process as well as decreasing the inherent complexity of the system as a whole.

K42 is structured around a client-server model, and much of the functionality traditionally implemented in the kernel or servers is moved to libraries in the application's address space. For example, all thread scheduling is done by a user-level scheduler library that is linked into each process. This design supports flexibility on a per-application basis. The specialization of services for a class of applications (e.g., games, scientific applications, databases, JVMs) is achieved by choosing the objects that are appropriate for the requirements of the target application and packaging them into a library. Overhead is reduced in many cases because crossing address space boundaries to invoke system services can be avoided. Also, space and time are consumed in the application rather than in the kernel or servers. For example, an application can have a large number of threads or file descriptors without consuming any additional kernel memory.

As multi-core chips become more prevalent, the scalability of the operating system becomes an important issue. K42 has been designed to achieve good multiprocessor performance through its object-oriented structure by maintaining the following characteristics. (1) Independent requests to different resources are serviced independently because there are no shared data structures to be traversed and no shared locks to be accessed, (2) locality is maintained for resources accessed by a small number of processors, and (3) the use of clustered-object technology allows widely accessed objects to be implemented in a distributed fashion.

Clustered objects are an enhanced object-oriented model supported by K42 [5, 9, 22]. Clustered objects, described in more detail in Section 2.4.2, improve access locality by enabling selective partitioning, replication, and distribution of object implementations.

The systematic integration of support for flexible data distribution on a per-object basis has yielded a simpler, incremental approach to scalable system design and implementation. The clustered object based infrastructure eases the addition of new scalable services by allowing the developer to focus initially on functional aspects through a non-distributed version, and then extend the implementation incrementally (for example, on a per-method basis) to a distributed version.

Distributed implementations can offer better scalability, but they also typically suffer greater overheads when scalability is not required. Distributed implementations also tend to optimize certain operations, improving their scalability, while increasing costs of other operations. In order to provide a means for coping with the tradeoffs of using distributed implementations, K42 enables hot-swapping, a technique for dynamically replacing a live clustered object instance with a different, but compatible, instance. This mechanism can be used to switch between shared and distributed implementations and additionally enable other forms of dynamic adaptation.

The design of K42, and the aforementioned hot-swapping capabilities, are centered around the concept of clustered objects. The next subsection explains clustered objects in greater detail.

## 2.4.2 Clustered Objects

Clustered objects are the building blocks of K42, and are integral to realizing scalability and customizability within the K42 operating system. Each clustered object is identified by a unique interface to which every implementation conforms [5]. K42 uses a C++ pure virtual base class to express a clustered object interface (Clustered Object interface class). An implementation of a clustered object consists of two definitions: a Root definition and a Representative definition expressed as separate C++ classes. The Root class defines the global portions of an instance of the clustered object. Every instance of a clustered object has exactly one instance of its Root class that serves as the internal central anchor

or 'root' of the instance. The Representative (Rep) definition of a clustered object defines the per-processor portion of the clustered object. The Representative class implements the interface of the clustered object, inheriting from the clustered object's interface class. Each Rep has a pointer to the Root of the clustered object instance. The methods of a Rep can access the shared data and methods of the clustered object via its root pointer.

Clustered objects support distributed designs while preserving the benefits of a component-based approach [5]. A clustered object can be internally decomposed into a group of cooperating subparts, called Representatives, that implement a uniform interface, but use distributed structures and algorithms to avoid shared memory and synchronization on its frequent and critical operations. Clustered objects provide an infrastructure to implement both shared and distributed implementations of objects, and transparently to the client, permit the use of the implementation appropriate for the access pattern of the object. Collections of C++ classes are used to define a clustered object, and run-time mechanisms are used to support the dynamic aspects of the model.

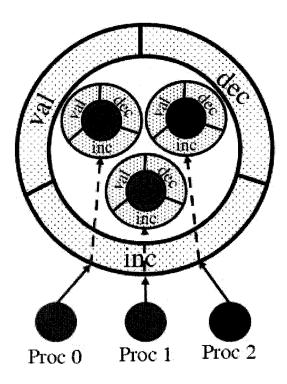

Clustered objects allow each object instance to be decomposed into per-processor Representatives <sup>1</sup>, and therefore provide a vehicle for distributed implementations of objects. Figure 2.5 illustrates a clustered object of a simple distributed integer counter. Externally, a single instance of the counter is visible, but internally, the implementation of the counter is distributed across a number of Representatives, each local to a processor. An invocation of a method of the clustered object's interface on a processor is automatically and transparently directed to the Representative local to the invoking processor. The internal distributed structure of a clustered object is encapsulated behind its interface and transparent to clients of the object. In Figure 2.5, a single instance of the counter, represented by the outer ring labeled with the counter's interface (inc, val and dec), is accessed by code executing on the processors at the bottom of the diagram. All

$<sup>^{1}</sup>$ A Representative can be associated with a cluster of processors of an arbitrary size, from 1 to n, and not necessarily per processor

Figure 2.5: Abstract Clustered Object Distributed Counter

processors invoke the **inc** method of the instance. Transparently to the invoking code, the invocations are directed to internal per-processor Representatives, illustrated by the three inner rings in the diagram. Each Representative supports the same interface, but encapsulates its own data members. This ensures that the invocation of the **inc** method on each processor results in the update of an independent per-processor counter, thereby avoiding sharing and ensuring better performance.

At run-time, an instance of a given clustered object is created by instantiating an instance of the desired Root class. Instantiating the Root establishes a unique Clustered Object Identifier (COID also referred to as a Clustered Object ref) that is used by clients to access the newly created instance. To the client code, a COID appears to be a pointer to an instance of the Rep Class [5]. To provide better code isolation, this fact is hidden from the client code with the macro:  $\#define\ DREF(coid)\ (*(coid))$ . For example, if c is a variable holding the COID of an instance of a clustered performance counter that has

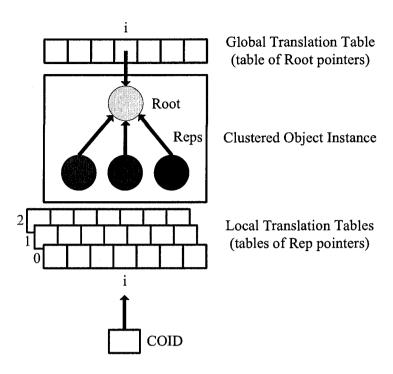

Figure 2.6: A Clustered Object Instance and Translation Tables

a method inc, a call would look like: DREF(c)->inc().

A set of tables and protocols are used to translate calls on a COID in order to achieve the unique run-time features of clustered objects. There is a single shared table of Root pointers called the Global Translation Table (GTT) and a set of Rep pointer tables called Local Translation Tables (LTTs), one per processor. An illustration of how a clustered object's Root and Reps relate to each other is shown in Figure 2.6.

In order to avoid overhead caused by redundant creation of Reps on processors that do not use them, a Rep is not immediately created or installed into the LTTs when the clustered object is instantiated. Instead, empty entries of the LTT are initialized to refer to a special hand-crafted object called the Default Object. The first time a clustered object is accessed on a processor, the same global Default Object is invoked. The Default Object leverages the fact that every call to a clustered object goes through a virtual function table. (Remember that a virtual base class is used to define the

interface for a clustered object.) The Default Object overloads the method pointers in its virtual function table to point at a single trampoline method. The trampoline code saves the current register state on the stack, looks up the Root installed in the GTT entry corresponding to the COID that was accessed, and invokes a well-known method that all Roots must implement, called handleMiss. This method is responsible for installing a Rep on the processor into the LTT entry corresponding to the COID that was accessed. This is done either by instantiating a new Rep or by identifying a preexisting Rep and storing its address into the address pointed to by the COID in the LTT. On return from the handleMiss method, the trampoline code restarts the call on the correct method of the newly installed Rep. The above process is called a Miss and its resolution Miss-Handling. Note that after the first Miss on a clustered object instance, on a given processor, all subsequent calls on that processor will proceed as standard C++ method invocations via two pointer dereferences. Thus, in the common case, methods of the installed Rep will be called directly with no involvement of the Default Object.

## 2.4.3 Memory Management

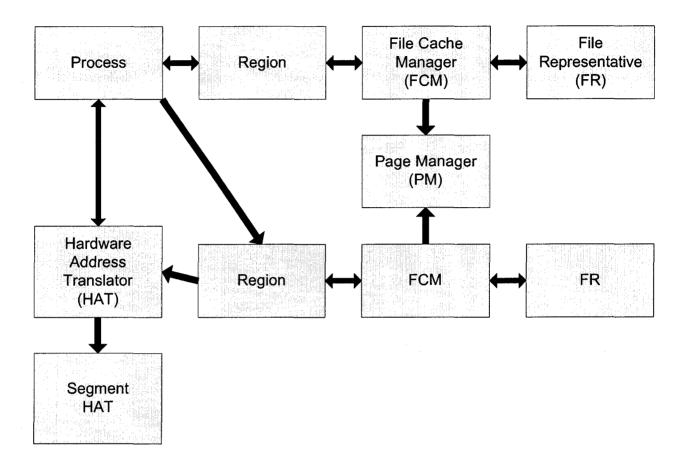

An overview of K42's overall memory management structure can be seen in Figure 2.7. Each of the objects in the diagrams has the following functionality:

- Process root of the object tree representing a Process in the kernel. The Process maintains a list of Regions that exist in its address space, and maintains a reference to a virtual to physical memory address translator.

- 2. Region represents the mapping from a range of virtual addresses to a range of file offsets (all memory in K42 is accessed by using files).

- 3. File Representative (FR) the kernel realization of a file. Facilitates communication with the external implementation of the file to do I/O and for other file system purposes.

Figure 2.7: An overview of K42 memory management structure. Each K42 Process contains a single address space. The address space is made up of Regions, each of which spans a range of virtual addresses in the Process's address space. A Region maps its range of addresses onto a range of offsets in a file, handled by the FR. The FR communicates with an external file system of choice, which is a service provided by a user-level implementation. Although at first glance it seems that there is a duplicate version of the Region object in this hierarchy, the different connectivity is used to represent a specialized implementation. A Region can be used to only manage virtual addresses (top), or to implement processor-specific memory by using the processor's number in its mapping of virtual addresses to file offsets, in which case it needs the HAT (bottom).

- 4. File Cache Manager (FCM) controls the page frames currently assigned to contain file contents in memory. It also implements the local paging policy for the file and supports Region requests to make file offsets addressable in virtual memory.

- 5. Page Manager (PM) controls the allocation of page frames to FCMs.

- 6. Hardware Address Translator (HAT) manages the hardware representation of an address space.

- 7. Segment HAT manages the representation of a hardware segment. Segments are of hardware dependent size and hold several virtual memory pages. Their size and amount of pages they can store depends on both the underlying architecture and page granularity.

We have presented background material which relates to the work described in this dissertation, including HPCs, various instrumentation techniques, and the K42 operating system. The next chapter will describe KOV's design and implementation details.

# Chapter 3

# System Design and Implementation

In this chapter we present the design and implementation of the Kernel Object Viewer (KOV), a tool designed to aid programmers and operating systems designers in analyzing performance. As previously mentioned, computer systems are becoming more complex every year. This increased complexity makes it exceedingly difficult to qualitatively and quantitatively understand how well a running system is performing. Moreover, for performance-critical applications it is equally challenging to deduce the effects of code (or design) modifications on performance. We have designed KOV to aid programmers in the task of identifying performance bottlenecks and their precise causes, as well as to aid operating system designers in identifying performance bottlenecks within the operating system under different workloads.

## 3.1 Overview

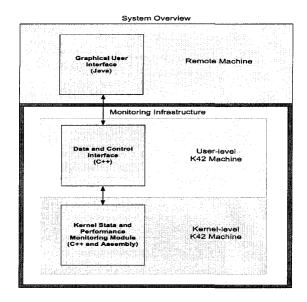

Conceptually, the KOV performance monitoring tool is composed of two distinct parts: a monitoring infrastructure and a graphical user interface (GUI). The monitoring infrastructure obtains a list of all live processes and their objects and gathers performance data, whereas the GUI displays this data to the user.

A user interacts with KOV via the GUI. A user can issue commands in the GUI to

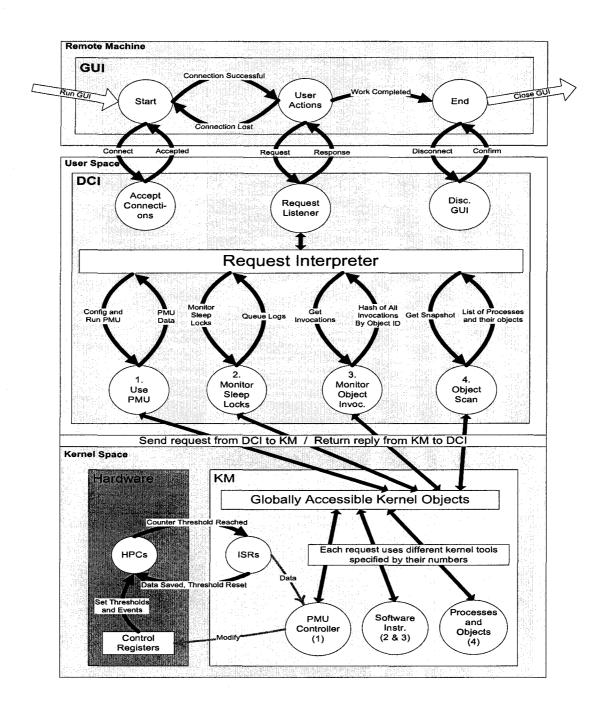

Figure 3.1: A high-level view of the system's architecture. Two of the bottom elements have to be on the same machine, whereas the GUI can run remotely.

obtain a list of all live processes and their objects and monitor performance. The GUI sends these commands to the monitoring infrastructure to perform the desired tasks. The monitoring infrastructure receives these commands and subsequently starts gathering data from the system. This data is stored internally in the monitoring infrastructure. The GUI periodically polls the monitoring infrastructure for this data and subsequently displays it to the user.

An overview of KOV's design is shown in Figure 3.1. The figure shows the GUI, and the two components that implement the monitoring infrastructure. The following sections describe these two components and the GUI in more detail.

# 3.2 Monitoring Infrastructure

The monitoring infrastructure of KOV is comprised of two components, a data gathering component which resides in the kernel, and a communication interface component which resides in user-space. Both of these components must run on the machine being monitored. The aforementioned components will be referred to as:

- 1. the Kernel State and Performance Monitoring Module (KM), and

- 2. the Data and Control Interface (DCI),

respectively, in the remainder of this dissertation.

The KM is a kernel module which maintains a list of all objects in the system and monitors the performance of the system. Objects are identified by obtaining a list of all live processes from the kernel and scanning the list of all instantiated objects within each process. The KM monitors performance by using the processor's Performance Monitoring Unit (PMU) (please refer to Section 3.2.1) and by using software instrumentation. A kernel module is necessary to perform these tasks because only the kernel process, which is privileged, is able to access the PMU. All the information gathered by the KM is stored internally in a set of data buffers. These buffers are subsequently read by the DCI.

The DCI is the link between the KM and the outside world. The DCI communicates with the KM by issuing system calls. Communication with the KM is comprised of passing control parameters to the KM, and retrieving the list of all live processes and their objects, and performance data from the KM's data buffers. Communication with the outside world starts when a GUI connects to the DCI.

The DCI uses the network for communication with the outside world by listening for connections on a specific network port. This allows the DCI to facilitate performance monitoring from remote workstations. It is preferable to have the ability to monitor a system's performance remotely because such a setup enables the user to monitor many machines, located at varying geographical locations, from a single machine.

The following subsections describe the KM and DCI in greater detail.

### 3.2.1 Kernel State and Performance Monitoring Module

The KM is solely responsible for obtaining object information and performance data from the system being monitored. It is designed to work with K42, an object-oriented operating system. Therefore information about the system can be extracted by obtaining a list of all live processes, and scanning all instantiated objects within each process. Performance monitoring data is gathered with the use of the architecture's PMU and software instrumentation. Consequently, the KM can perform the following tasks:

- 1. perform a system scan by obtaining a list of all live processes and scanning their objects,

- 2. configure and extract data from the PMU, and

- 3. obtain information through software instrumentation.

### Object Scan

The list of objects is constructed by obtaining a list of all live processes and subsequently scanning all instantiated objects within each process. The KM obtains a list of all live processes by accessing K42's ProcessAnnex object. The ProcessAnnex object resides in the kernel and keeps track of all live processes by maintaining a list of Process objects. A Process object is the kernel's representation of a process and contains information ranging from the process' identification number (PID), memory regions assigned to the process, and other information.

Using the Processes' PIDs, the KM is able to scan for all instantiated objects within each process. The object scan obtains two pieces of information. The first is a list of all instantiated objects within a particular process, and the second is the object's state (specifically, references to other objects). The first piece of information lets the user know what objects a particular process has instantiated (for example, one Process object, five Region objects, and five File objects), whereas the second piece of information lets the

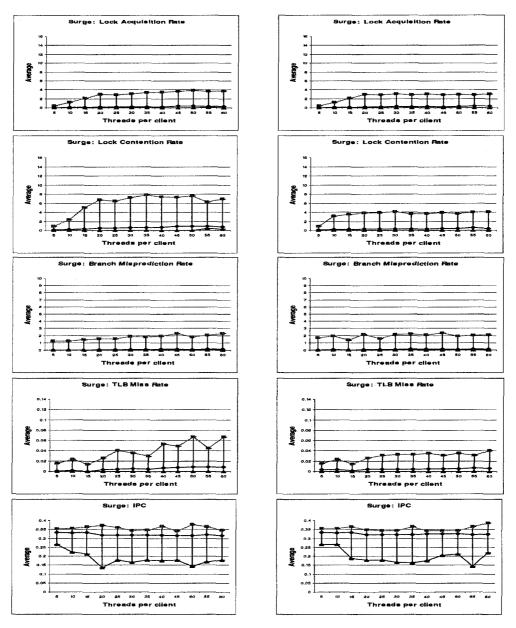

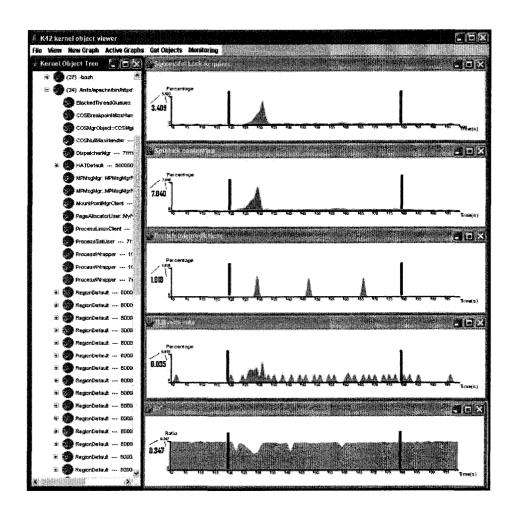

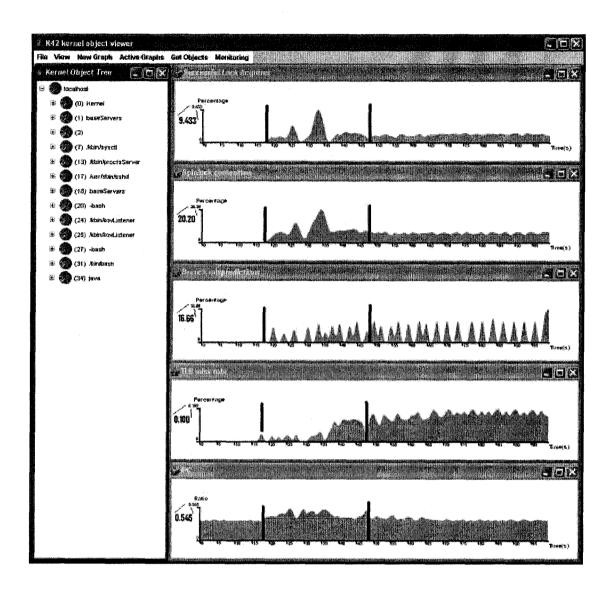

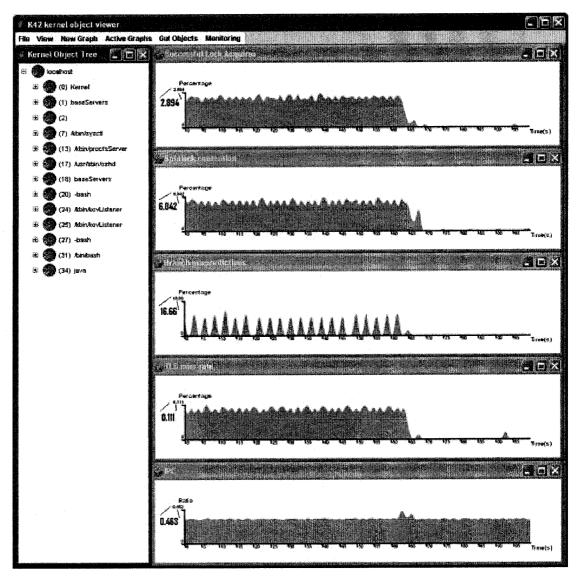

user know how these objects relate to each other (for example, the Process object has a list of references to all five Region objects, and each Region object has a reference to one File object). These two pieces of information allow an object hierarchy of the system to be constructed. Before we explain in detail how the object scan is performed, a brief overview of K42's design is necessary.