## METHODS FOR GPU ACCELERATION OF BIG DATA APPLICATIONS

by

Reza Mokhtari

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Graduate Department of Electrical and Computer Engineering University of Toronto

© Copyright 2017 by Reza Mokhtari

#### Abstract

Methods for GPU acceleration of Big Data applications

Reza Mokhari Doctor of Philosophy Graduate Department of Electrical and Computer Engineering University of Toronto 2017

Big Data applications are trivially parallelizable because they typically consist of simple and straightforward operations performed on a large number of independent input records. GPUs appear to be particularly well suited for this class of applications given their high degree of parallelism and high memory bandwidth. However, a number of issues severely complicate matters when trying to exploit GPUs to accelerate these applications. First, Big Data is often too large to fit in the GPU's separate, limited-sized memory. Second, data transfers to and from GPUs are expensive because the bus that connects CPUs and GPUs has limited bandwidth and high latency; in practice, this often results in data-starved GPU cores. Third, GPU memory bandwidth is high only if data is layed out in memory such that the GPU threads accessing memory at the same time access adjacent memory; unfortunately this is not how Big Data is layed out in practice.

This dissertation presents three solutions that help mitigate the above issues and enable GPU-acceleration of Big Data applications, namely **BigKernel**, a system that automates and optimizes CPU-GPU communication and GPU memory accesses, **S-L1**, a caching subsystem implemented in software, and a **hash table** designed for GPUs. Our key contributions include: (i) the first automatic CPU-GPU data management system that improves on the performance of state-of-the-art double-buffering scheme (a scheme that overlaps communication with computation to improve the GPU performance), (ii) a GPU level 1 cache implemented entirely in the software that outperforms hardware L1 when used by Big Data applications and, (iii) a GPU-based hash table (for storing key-value pairs popular in Big Data applications) that can grow beyond the available GPU memory yet retain reasonable performance. These solutions allow many existing Big Data applications to be ported to GPUs in a straightforward way and achieve performance gains of between 1.04X and 7.2X over the fastest CPU-based multi-threaded implementations.

#### Acknowledgements

I consider myself the luckiest among all versions of me in all parallel universes, because I was fortunate enough to get research and life advice from my advisor, Professor Michael Stumm. I truly believe he has a very special blend of wisdom, open-mindedness, perfectionism, and kindness. He looks at the world uniquely in that he has a talent in easily dissecting complex concepts and getting to their basic elements. He then rebuilds his own version of the concept from ground up using those elements. He has frequently amazed me with this talent, which is also very helpful in doing advanced research.

During my PhD years, I have often been asked by people around me whether if I would choose to go for a PhD again if I were given the chance to go back five years; it gives me a great deal of comfort in thinking and saying "I would do it in a heartbeat, if I'm given the opportunity to do it under the advice of Michael." Indeed, I am deeply indebted to him, beyond what words can describe, and will always be sincerely grateful for his contribution to my development, both as a researcher and as a person.

I would also like to address a special thought to my Masters thesis co-supervisor, Reza Azimi, without whom I would definitely not be where I am now. He guided me during my first steps in research and showed me how I can have fun doing it. I will always be grateful for his trust and thankful for his help.

Much gratitude goes to my thesis committee members and associated faculty, Andreas Moshovos, Ding Yuan, Ashvin Goel, and John Owens for their valuable feedback and support.

To all my friends, especially Roja, Sepehr(s), and Nass, your care and encouragement were always a source of joy and comfort. I am lucky to have in my life.

Finally, I would like to thank my parents and my sister, who, despite being far from me, have been a constant source of love, support, approval, and strength. I feel fortunate to have been raised in such a house that enabled me to reach this point of my life.

# Contents

| 1 | Intr | oduction                                                   | 1  |

|---|------|------------------------------------------------------------|----|

|   | 1.1  | Contributions                                              | 4  |

|   | 1.2  | Organization                                               | 5  |

| 2 | Bac  | kground                                                    | 6  |

|   | 2.1  | GPGPU Overview                                             | 6  |

|   | 2.2  | GPU Overview                                               | 7  |

|   |      | 2.2.1 GPU Hardware                                         | 7  |

|   |      | 2.2.2 GPU Software                                         | 0  |

| 3 | Rela | ated Work 1                                                | 2  |

|   | 3.1  | GPU accelerated applications                               | 2  |

|   | 3.2  | Work on core data structures                               | 4  |

|   | 3.3  | Runtime and Compiler-assisted Systems                      | 6  |

|   |      | 3.3.1 CPU-GPU Communications Management Systems            | 7  |

|   |      | 3.3.2 GPU Memory Optimization Systems 1                    | 9  |

|   | 3.4  | GPU Performance Characterization                           | .0 |

| 4 | BigH | Kernel 2                                                   | 2  |

|   | 4.1  | Overview                                                   | .2 |

|   | 4.2  | Design and Implementation                                  | 3  |

|   |      | 4.2.1 A simple motivating example                          | 25 |

|   | 4.3  | Optimizations                                              | 0  |

|   |      | 4.3.1 Pattern recognition                                  | 1  |

|   |      | 4.3.2 Data locality in assembling data                     | 1  |

|   |      | 4.3.3 Synchronization                                      | 2  |

|   |      | 4.3.4 Buffer allocation: active vs. inactive thread-blocks | 3  |

|   | 4.4  | Experimental Evaluation                                    | 3  |

|   |      | 4.4.1 Overall results                                      | 5  |

|   |      | 4.4.2 Performance breakdown                                | 7  |

|   |      | 4.4.3 Stage completion time breakdown                      | 8  |

|   |      | 4.4.4 Pattern recognition                                  | 9  |

| 5  | S-L1   | l              |                                                             | 41       |

|----|--------|----------------|-------------------------------------------------------------|----------|

|    | 5.1    | Motiva         | ntion                                                       | 41       |

|    |        | 5.1.1          | GPU Hardware L1 caches                                      | 42       |

|    |        | 5.1.2          | Historical Trends in GPU Compute Power and Memory Hierarchy | 43       |

|    |        | 5.1.3          | Behavior of GPU memory access performance                   | 44       |

|    | 5.2    | S-L1 D         | Design and Implementation                                   | 46       |

|    |        | 5.2.1          | Overview                                                    | 46       |

|    |        | 5.2.2          | Code Transformations                                        | 49       |

|    |        | 5.2.3          | S-L1 overheads                                              | 52       |

|    |        | 5.2.4          | Coherence considerations                                    | 53       |

|    | 5.3    | Experi         | mental Evaluation                                           | 53       |

|    |        | 5.3.1          | Experimental Setup                                          | 53       |

|    |        | 5.3.2          | S-L1 performance evaluation for GPU-local applications      | 54       |

|    |        | 5.3.3          | Evaluation of S-L1 for data residing in CPU memory          | 57       |

|    |        | 5.3.4          | S-L1 overheads                                              | 58       |

|    |        | 5.3.5          | Effect of S-L1 cache line size                              | 59       |

|    |        | 1 77 1         |                                                             | (1       |

| 6  |        |                | le for GPU-based Big Data Applications                      | 61       |

|    | 6.1    |                | m Statement                                                 | 61       |

|    | 6.2    |                | on Overview                                                 | 62       |

|    |        | 6.2.1<br>6.2.2 | SePo Overview                                               | 62<br>64 |

|    | 62     |                | Using SePo for larger-than-memory hash tables               |          |

|    | 6.3    | U              |                                                             | 66       |

|    |        | 6.3.1          | Dynamic Memory Allocator                                    | 66<br>67 |

|    |        | 6.3.2          | Bucket Organizations                                        | 67<br>70 |

|    | 6.4    | 6.3.3          | Applying the SePo model of computation                      | 70<br>72 |

|    | 6.4    |                |                                                             | 72       |

|    |        | 6.4.1          | Interoperability of pointers                                | 72       |

|    | 65     | 6.4.2          | Synchronization                                             | 73       |

|    | 6.5    |                | se: a simple MapReduce runtime                              |          |

|    | 6.6    |                | mental Results                                              | 75<br>75 |

|    |        | 6.6.1          | Experimental Setup                                          | 75       |

|    |        | 6.6.2          | Overall results                                             | 77       |

|    |        | 6.6.3          | Comparing with MapCG                                        | 79       |

|    |        | 6.6.4          | Comparing with alternative approaches                       | 80       |

| 7  | Con    | cluding        | Remarks                                                     | 83       |

| Bi | bliogr | aphy           |                                                             | 86       |

# **List of Tables**

| 2.1 | Comparing recent GPUs key characteristics.                                                        | 7  |

|-----|---------------------------------------------------------------------------------------------------|----|

| 3.1 | Studies on porting applications to GPUs with the claimed speedup achieved                         | 13 |

| 3.2 | Several other studies that characterize the performance of GPUs.                                  | 21 |

| 4.1 | Application Mapped input data. (An application may also allocate and access other non-mapped      |    |

|     | data structures.)                                                                                 | 35 |

| 4.2 | Performance improvement due to the use of access patterns.                                        | 40 |

| 5.1 | Ten Big Data applications used in our experimental performance evaluation, their description, and |    |

|     | the number of data structures they use in their main loop. S-L1 determines the number of data     |    |

|     | structures to cache at runtime, which could vary from run to run depending on the available size  |    |

|     | of shared memory per thread                                                                       | 54 |

| 6.1 | Input dataset sizes used in our experiments.                                                      | 75 |

| 6.2 | Speedups over MapCG                                                                               | 80 |

| 6.3 | Calculated lower bound data transfer time if PVC was run on a demand paging-equipped hardware     |    |

|     | compared to the total execution time when PVC is run using our hash table.                        | 82 |

# **List of Figures**

| 1.1  | GPU and CPU computing power over the years.                                                          | 2  |

|------|------------------------------------------------------------------------------------------------------|----|

| 1.2  | GPU and CPU memory bandwidth over the years.                                                         | 2  |

| 2.1  | The internal structure a <i>streaming multiprocessor</i> (SMX).                                      | 7  |

| 2.2  | The connections between different components of the system.                                          | 9  |

| 2.3  | A trivial CUDA application that squares the elements of an array                                     | 11 |

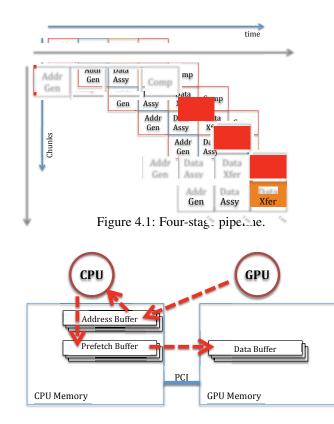

| 4.1  | Four-stage pipeline.                                                                                 | 24 |

| 4.2  | BigKernel buffers                                                                                    | 24 |

| 4.3  | K-means computation.                                                                                 | 25 |

| 4.4  | K-means GPU-side code.                                                                               | 25 |

| 4.5  | K-means CPU-side code.                                                                               | 26 |

| 4.6  | K-means CPU-side code when using BigKernel                                                           | 26 |

| 4.7  | GPU-side (transformed) code to generate prefetch addresses in BigKernel                              | 27 |

| 4.8  | GPU-side (transformed) code to use the prefetched data.                                              | 28 |

| 4.9  | Implementation of the four-stage pipeline.                                                           | 29 |

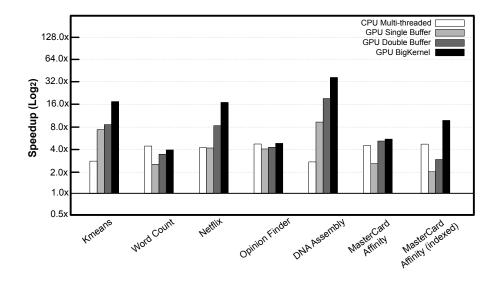

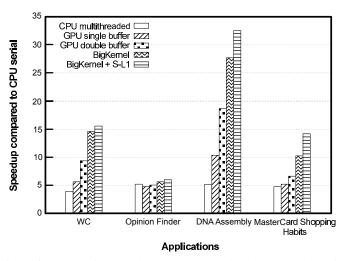

| 4.10 | Application speedup over serial CPU implementation.                                                  | 36 |

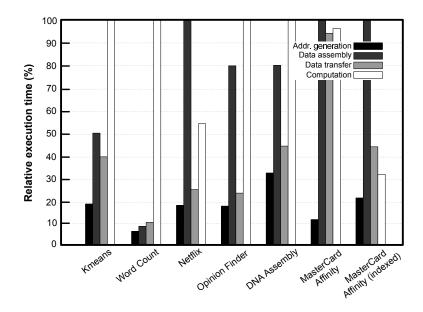

| 4.11 |                                                                                                      | 37 |

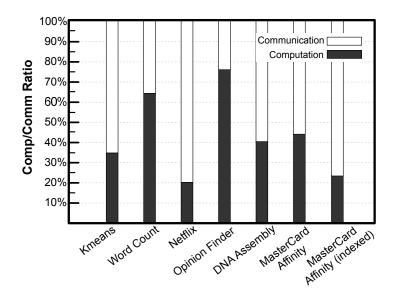

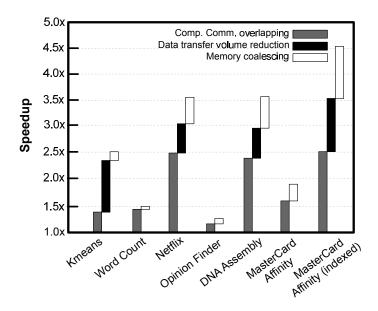

| 4.12 | The incremental benefit of (i) overlapping computation and communication, (ii) reducing the          |    |

|      | volume of data transferred due to prefetching, and (iii) laying out the data to increased coalesced  |    |

|      | accesses.                                                                                            | 38 |

| 4.13 | Relative completion time of each BigKernel stage.                                                    | 39 |

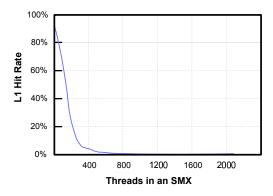

| 5.1  | L1 hit rate when running wc on Titan Black GPU with 192 cores. The target data is partitioned        |    |

|      | into $n$ chunks with each chunk assigned to a thread for processing. With effective caching, the     |    |

|      | first access of each thread results in a miss, but the subsequent 127 accesses result in cache hits. |    |

|      | Without effective caching, these accesses result in 128 misses.                                      | 42 |

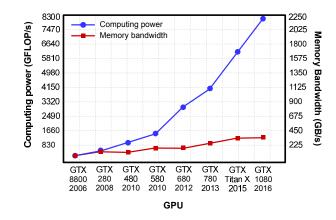

| 5.2  | Compute power and memory bandwidth over time/GPU generations, normalized to the values of            |    |

|      | GTX 8800                                                                                             | 43 |

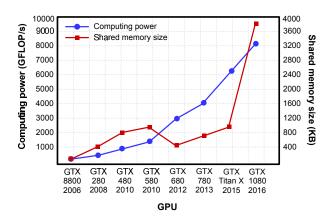

| 5.3  | Compute power and L1 / shared memory size over time/GPU generation, normalized to the values         |    |

|      | of GTX 8800 (the rate of growth of GPU register file size has also been similar to that of L1 /      |    |

|      | shared memory).                                                                                      | 43 |

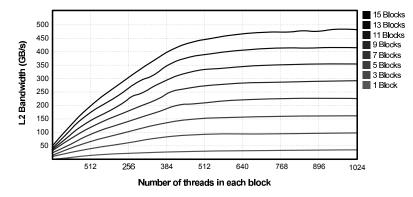

| 5.4  | L2 memory throughput as a function of number of threads in a thread block. Each curve represents     |    |

|      | the throughput for a different number of thread blocks (1 to 15) with each thread block running      |    |

|      | 1,024 threads                                                                                        | 45 |

|      |                                                                                                      |    |

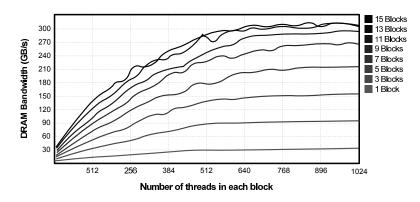

| 5.5  | DRAM memory throughput as a function of number of threads in a thread block. Each curve                          |     |

|------|------------------------------------------------------------------------------------------------------------------|-----|

|      | represents the throughput for a different number of thread blocks (1 to 15) with each thread block               |     |

|      |                                                                                                                  | 45  |

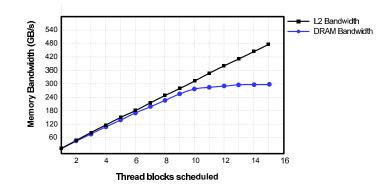

| 5.6  | L2 and DRAM memory bandwidth as a function of number of thread blocks where each thread                          |     |

|      |                                                                                                                  | 46  |

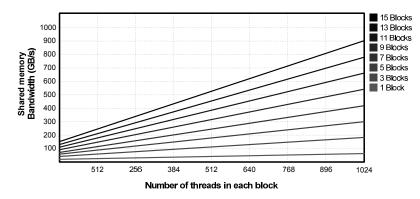

| 5.7  | Shared memory throughput as a function of number of threads in a thread block. Each curve                        |     |

|      | represents the throughput for a different number of thread blocks (1 to 15) with each thread block               |     |

|      |                                                                                                                  | 46  |

| 5.8  | 1                                                                                                                | 50  |

| 5.9  | 1                                                                                                                | 51  |

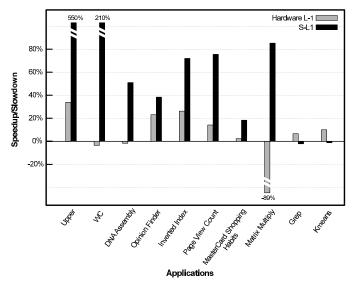

|      | Speedup when using S-L1 relative to no L1 caching.                                                               |     |

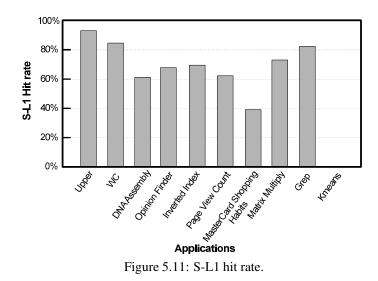

| 5.11 | S-L1 hit rate.                                                                                                   | 55  |

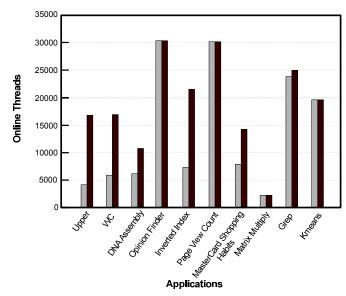

| 5.12 | The optimal number of online threads (that leads to the best execution times) with and without                   |     |

|      | S-L1 (hardware L1 is enabled).                                                                                   | 56  |

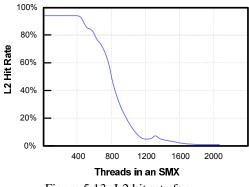

| 5.13 | L2 hit rate for wc                                                                                               | 56  |

| 5.14 | Speedup of our five scenarios relative to the CPU single core version for four GPU applications                  |     |

|      | processing large data sets located in CPU memory.                                                                | 57  |

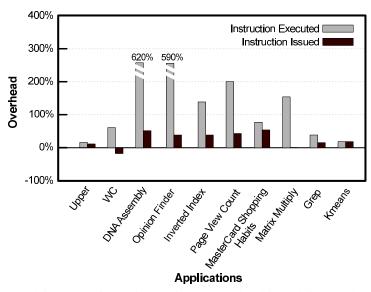

| 5.15 | S-L1 overhead, in terms of extra instruction executed and issued (in %) when using S-L1 relative                 |     |

|      | to when not using it                                                                                             | 58  |

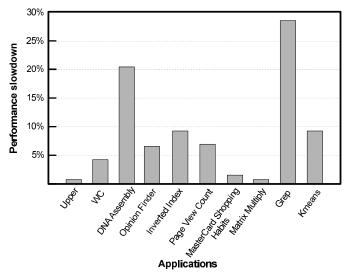

| 5.16 | Overhead of S-L1 when S-L1 is enabled but not used to cache any data.                                            | 59  |

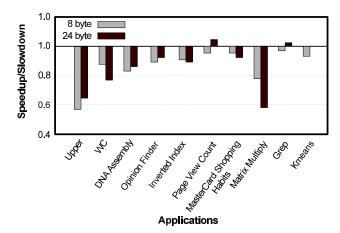

| 5.17 | Slowdown/speedup when using 8B and 24B cache lines over using 16B cache lines                                    | 59  |

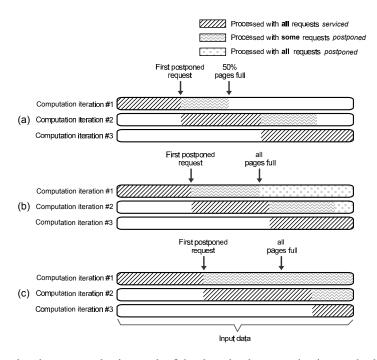

| 6.1  | How the SePo model can improve performance.                                                                      | 63  |

| 6.2  | A snapshot of a hash table during a subsequent iteration of computation (not all pointers are shown              |     |

|      |                                                                                                                  | 65  |

| 6.3  |                                                                                                                  | 68  |

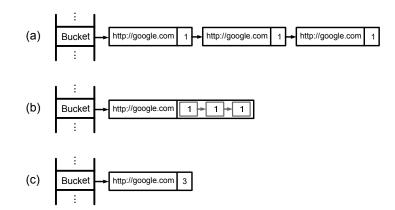

| 6.4  |                                                                                                                  | 69  |

| 6.5  | A snapshot of the hash table when filled by PVC data under three bucket organizations: (a) <i>basic</i> ,        |     |

| 0.0  |                                                                                                                  | 70  |

| 6.6  | How input data is processed using each of the three bucket organization methods: (a) <i>basic</i> ,              | , 0 |

| 0.0  | (b) <i>multi-valued</i> , and (c) <i>combining</i> . Note that in (c), even after all pages get full, pairs with |     |

|      |                                                                                                                  | 71  |

| 6.7  | Pseudo code to insert the $toBeInserted$ element between two existing elements (i.e. $prev$ and                  | /1  |

| 0.7  |                                                                                                                  | 73  |

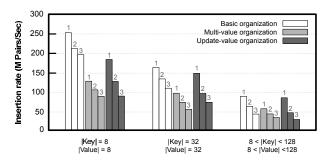

| 6.8  | KV pair insert rate when using different key and value sizes, different bucket organization meth-                | 15  |

| 0.8  |                                                                                                                  | 77  |

| 6.0  |                                                                                                                  | //  |

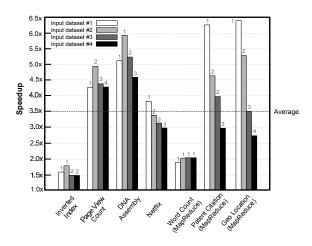

| 6.9  | Application speedup over CPU multi-threaded implementation. For the last three, the baseline is                  | 70  |

| 6 10 |                                                                                                                  | 78  |

|      |                                                                                                                  | 79  |

| 6.11 | Speedups compared to the pinned version.                                                                         | 81  |

## Chapter 1

## Introduction

An important class of computations operate on voluminous datasets in ways similar to what is sometimes referred to as "Big Data" computations and other times (in the GPU community) referred to as streaming computations. These computations perform simple, straightforward, and independent operations on a large number of input data records. They are trivially parallelizable, and the input data exhibits no (or very low) reuse. This class of computation is large and includes computations that filter, transform, aggregate or partition large data sets.

As an example application, consider Page View Count, which counts the number of occurrences of each URL in input web-log files. This application is easily parallelized by partitioning the input data into smaller chunks, having different worker threads count the URLs in different chunks, and then, at the end, aggregate the results.

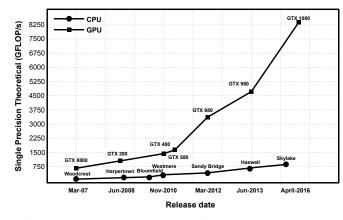

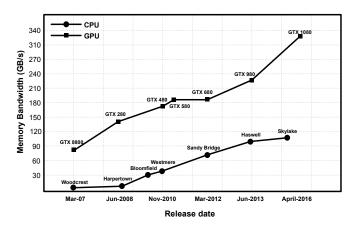

GPUs appear to be well suited for accelerating Big Data applications. The many GPU cores allow for highly parallelized computing. A GPU offers aggregate compute power an order of magnitude larger than what a CPU can; e.g., 8.3 TFLOPS vs. 1.5 TFLOPS (Nvidia GTX 1080 vs. an Intel Skylake CPU with 20 cores). And GPU memory has significantly higher theoretical bandwidth than CPU memory, since they were designed for graphics processing; e.g., 320 GB/s vs. 115 GB/s. Figures 1.1 and 1.2 depict the improvements in computing power and memory bandwidth of modern GPUs and CPUs. As shown, GPUs computational power and memory bandwidth are reaching levels previously expected only from small supercomputers.

While GPUs appear to be attractive for Big Data applications, a number of issues complicate their efficient use. First is the issue of managing the data that does not fit in GPU memory. The CPU and GPU have separate memories, requiring explicit data transfers between CPU and GPU memory, and GPU memory is limited in size (currently up to at most 16GB). As a result, substantial non-trivial effort has to go into managing data that does not fit in GPU memory. For the typical input data of Big Data applications, this means that the data needs to be explicitly partitioned into chucks and iteratively copied into GPU memory for processing there, which makes

Figure 1.1: GPU and CPU computing power over the years.

Figure 1.2: GPU and CPU memory bandwidth over the years.

GPU programming more difficult and error-prone. Further, the PCIe link that connects the two memories has limited bandwidth and, for the computations we are considering, can often be a bottleneck starving GPU cores from their data. For example, PCIe Gen 3 has a theoretical maximum throughput of 15.75 GB/s, far lower than the memory bandwidth GPU-side, and this bandwidth is difficult to exploit in practice. Indeed, while impressive speedups have been reported for many GPU applications, the speedups were often calculated without taking into account the overhead of transferring the input data to GPU memory [32].

A second issue is the fact that the high bandwidth of GPU memory can be exploited only when GPU threads executing at the same time access memory in a coalesced fashion; i.e., where the threads simultaneously access adjacent memory locations. If not coalesced, memory accesses may become serialized, resulting in significantly lower memory throughput and high access latencies. Because the applications we are targeting are not a priori structured to operate on data in a coalesced fashion, the data has to be reorganized to support coalesced accesses on the GPU, which is non-trivial.

A third issue is the fact that the GPU L1 caches are entirely ineffective [43]. For the typical number of cores

in modern GPUs, the L1 caches are too small and their cache line sizes are disproportionally large given the small cache size. For example, the Nvidia GTX 1080 has 128 cores per SMX, each of which can have multiple outstanding memory accesses at any time. Yet the maximum L1 cache size is 64KB and the cache line size is 128 bytes (for a total of 512 cache lines). Thus, cache lines are typically evicted before there is any reuse, causing a high degree of cache thrashing and an attendantly low L1 hit rate given the large number of threads executing on GPU cores, each issuing multiple memory accesses (typically to independent memory locations in our target applications).

Finally, a forth issue is that traditional data structures typically perform poorly when naïvely ported to the GPU. For example, traversing linked lists can result in low GPU core utilization because groups of GPU cores execute in SIMD fashion and all the cores in the group will have to wait for the slowest core that had to traverse the longest list. To prevent such performance degradations, data structures and their associated operations often have to be restructured to take into account the micro-architectural characteristics of the GPU. Hash table is one of those data structures that is particularly important to us because it can efficiently store key-value pairs that are widely used in Big Data applications. Hash tables that do not fit in GPU memory are particularly challenging to implement on GPUs without excessive CPU-GPU communication because there is, by design, little locality in accessing the table.

In this dissertation, we present a set of runtime/compile-time systems and libraries to address the issues mentioned above. First, we present a scheme, called BigKernel, that automates and optimizes CPU-GPU communication and GPU memory accesses. Second, we present S-L1, a level-1 (L1) cache for GPUs implemented entirely in software to address the ineffectiveness of hardware L1 caches. Finally, we present a hash table design that allows the hash table to grow beyond the size of GPU memory, and yet stay reasonably efficient. The code required for BigKernel, S-L1, and our hash table can be applied to existing Big Data applications using straightforward compiler transformations and/or by using runtime libraries.

BigKernel provides pseudo-virtual memory to Big Data GPU applications that operate on streaming data. It uses a four -stage pipeline with automated prefetching to (i) optimize CPU-GPU communication and (ii) optimize GPU memory accesses. BigKernel optimizes CPU-GPU communication by only transferring the data that will be accessed GPU-side, and it optimizes GPU memory accesses by rearranging the data in a way that coalescing is increased significantly when the GPU accesses the data. It also simplifies the programming model by allowing programmers to write kernels using arbitrarily large data structures when the data records can be operated on independently, thus relieving the programmer from having to partition the data into segments, manage buffers, transfer data between CPU and GPU, and having to invoke GPU kernels multiple times. Applying BigKernel on a set of Big Data applications shows that it outperforms both the CPU-based multi-threaded implementations (on average by 3.0X) and the GPU-based implementation of the applications that use the state-of-the-art double-

buffering scheme to transfer their data (on average by 1.7X).

S-L1 uses GPU's shared memory to provide an L1 cache implemented entirely in software. The GPU shared memory is a small software-managed memory, which is positioned at the same level as the GPU's L1 cache, and has the same access latency as the hardware L1. S-L1 determines, at run time, the proper size of cache, samples the effectiveness of caching the data of different data structures, and based on that information, decides what data to cache. On a set of Big Data GPU applications, S-L1 achieves an average speedup of 1.9 over hardware L1 and 2.1 over no L1 caching. Combining S-L1 with BigKernel leads to an average speedup of 1.19 over BigKernel alone.

Finally, our hash table is intended to be used as a key-value store for GPU-based Big Data applications. It (i) supports variable-length keys and values, (ii) can perform on-the-fly grouping of key-value pairs with the same key and, (iii) uses a model of computation we developed, called SePo, to be able to obtain reasonable performance even when the table and its data grow larger than available GPU memory. Comparing a set of GPU-based Big Data applications that use our hash table with the corresponding CPU-based multi-threaded implementations shows an average speedup of 3.5, despite having the hash table grow to up to four times larger than the space available in GPU memory.

#### **1.1 Contributions**

This dissertation makes the following five specific contributions:

- The first system to automate CPU-GPU data transfers for large datasets without requiring the programmer to split the data or annotate the code (BigKernel).

- The first scheme to improve on the performance of state-of-the-art double-buffering scheme for GPUs (BigKernel).

- A software L1 cache implemented entirely in software with several novel features including a run-time scheme to automatically determine the parameters to configure the cache (S-L1).

- A GPU-based hash table to store key-values which can grow beyond the available GPU memory and retain reasonable performance.

- A model of computation that allows certain types of applications (including Big Data applications) to run more efficiently (SePo).

### 1.2 Organization

The rest of this dissertation is organized as follows. We start by presenting, in chapter 2, background information on general purpose computing on graphics hardware (GPGPU) and go over some of the key challenges in achieving good performance on GPUs. This is followed in chapter 3 with a description of work related to ours. We focus specifically on existing runtime/compile-time systems that improve the performance of GPU applications and on existing core data structures used in GPU applications. This dissertation then describes the three systems we designed and implemented. BigKernel, S-L1, and our hash table design are presented in chapter 4, 5, and 6, respectively. We close with concluding remarks and possible directions for future work in chapter 7.

We would like to point out that the work we describe in chapters 4 and 5 were published in May, 2014 [73] and August, 2015 [74], respectively. The work we describe in chapter 6 is ready to be published.

## Chapter 2

## Background

In this chapter we provide an overview of GPGPU and then present background information on the hardware and software sides of GPU programming to help the reader better understand the key factors involved in the performance and programmability of GPUs. This chapter can be skipped by readers already familiar with GPUs.

### 2.1 GPGPU Overview

The term GPU was first popularized by Nvidia in 1999 when it called its Geforce 256 "the world's first 'GPU', or Graphics Processing Unit". It took less than a year for programmers to use this GPU for non-graphical applications, coining the term General Purpose GPU (GPGPU). However, to program a GPU, one had to use the graphics library interfaces, which was rather tedious. GPU Programming later became easier with the introduction of GPU software development tools tailored specifically for developing computing applications.

In 2007, Nvidia introduced a GPGPU software platform for its own line of GPU devices, which it called *Compute Unified Device Architecture* (CUDA) [77]. Geforce GTX 8800 was the first CUDA-enabled consumer GPU, offering 518 GigaFLOPs of theoretical performance [78], compared to less than 6 GigaFLOPs theoretical performance of the, at the time, state-of-the-art Intel Core 2 processor running at 3.0 GHz. This created some excitement, especially when impressive speedups of applications ported to GPU platforms, sometimes in excess of 100, were reported (see Section 3.1). The rapid improvements of raw GPU performance over the last several years has given GPUs a performance advantage over CPUs for many compute intensive applications.

In the following section, we briefly give an overview of GPU hardware and software. For the hardware overview, we often use the specifications of Nvidia GTX 680 which implements the Kepler architecture [81]. We describe GTX 680 because it is the GPU we used to evaluated BigKernel and S-L1, presented in chapters 4 and 5. Although other GPU architectures will differ in some specifications, they share many general characteristics.

| GPU model       | GPU Family and<br>year | Number of cores#2 | memory bandwidth | Size of memory | Size of L2 cache | Size of onchip memory |

|-----------------|------------------------|-------------------|------------------|----------------|------------------|-----------------------|

| GTX 680         | Kepler (2012)          | 1536              | 192GB/s          | 2GB            | 1.5MB            | 64KB                  |

| GTX 780         | Kepler (2013)          | 2304              | 288GB/s          | 3GB            | 1.5MB            | 64KB                  |

| GTX Titan Black | Kepler (2014)          | 2880              | 336GB/s          | 6GB            | 1.5MB            | 64KB                  |

| GTX 980         | Maxwell (2015)         | 2048              | 192GB/s          | 8GB            | 2MB              | 128KB                 |

| GTX 1080        | Pascal (2016)          | 2560              | 320GB/s          | 8GB            | 4MB              | 128KB                 |

| Table 2.1: | Comparing | recent GPUs | key c | characteristics. |

|------------|-----------|-------------|-------|------------------|

|            |           |             |       |                  |

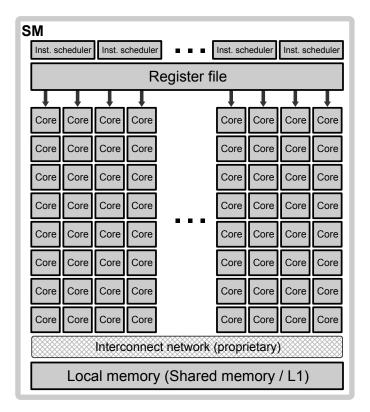

Figure 2.1: The internal structure a streaming multiprocessor (SMX).

Since GTX 680, Nvidia has released four newer series of GPUs, with the latest being GTX 1080. A comparison of the key characteristics of several recent GPUs is provided in Table 2.1.

In the following sections, we primarily use the terminology of Nvidia to describe the hardware and software aspects of GPUs, however we provide AMD/OpenCL's equivalent terms in footnotes as well.

### 2.2 GPU Overview

#### 2.2.1 GPU Hardware

GPU compute unit consists of several streaming multiprocessors (SMX)<sup>1</sup>, each of which contains multiple computing cores, tens of thousands of 4-byte registers, and a small (e.g. 64KB) but fast on-chip memory. Figure 2.1

<sup>&</sup>lt;sup>1</sup>SMXs are called *compute units* in AMD/OpenCL's terminology.

depicts the internal structure of an SMX.

Compared to a traditional multi-core CPU, a GPU has a far higher number of cores, but each core is simpler than a conventional CPU core. GPU cores are simpler, in part because they do not have an integrated instruction scheduler. Instead, a single instruction scheduler is shared between multiple GPU cores in an SMX. For example, in Kepler architecture, every 16 cores share the same instruction scheduler. As a result, groups of threads executed by the cores that share the same instruction scheduler run in lockstep, implementing Single Instruction Multiple Data (SIMD) type execution. *Thread divergence* will occur if, on a conditional branch, threads that run in lockstep take different paths, causing the threads to serialize the execution of different paths.

The small on-chip memory in each SMX is partitioned between a hardware-managed L1 cache and a programmer-managed *shared memory*<sup>2</sup>. In many GPUs, the programmer can configure how the SMX on-chip memory is to be partitioned between L1 and shared memory. GTX 680, with 64KB of on-chip memory per SMX, can be configured to assign 16KB-48KB or 48KB-16KB to L1 cache and shared memory, respectively. L1 cache is used to cache register spills and stack data (and not application data) [80]. Shared memory is programmer managed memory and allows threads running on the same SMX to efficiently share data.<sup>3</sup>

A larger L2 cache is shared by all SMXs of the compute unit and is connected to off-chip DRAM called *global memory*. We refer to this global memory as GPU memory in this document to differentiate it from CPU main memory.

For the Nvidia GTX 680, which is considered to be a reasonably modern GPU, access latency to registers, L1, shared memory, L2 and DRAM is 10, 80, 80,210, and 340 cycles, respectively. Moreover, the theoretically maximum bandwidth from L1, shared memory, L2 and DRAM have been reported to be 190.7GB/s, 190.7GB/s, 512GB/s, and 192GB/s, respectively [81].

GPU hardware uses two strategies to hide the latency of accesses to GPU memory: (i) fast context switch to another threads on a memory access<sup>4</sup> and (ii) wide memory buses that enable accesses to several data elements in a single memory transaction. To exploit that latter, however, GPU programs should be optimized to access memory in a coalesced fashion.

Coalesced memory accesses are those that are simultaneously issued by concurrent threads and fall within the same aligned 128-byte region. These memory accesses are coalesced into a single memory access by a hardware *coalescing unit* before being sent to memory, resulting in only one 128-byte memory transaction. Parallel memory accesses from concurrent threads to data are defined as n-way coalesced if n of the accesses fall within the same aligned 128-byte region.

<sup>&</sup>lt;sup>2</sup>Shared memory is called *local memory* in AMD/OpenCL's terminology.

$<sup>^{3}</sup>$ For threads to shared data, they not only need to run on the same SMX, but they have to be in the same *thread block*, which we describe later.

<sup>&</sup>lt;sup>4</sup>The context switch between GPU threads is fast because everything is stored in registers and thus there is almost no data movement on a context switch.

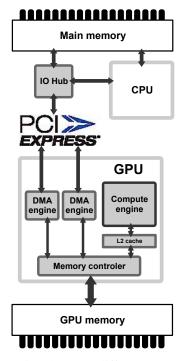

Figure 2.2: The connections between different components of the system.

Figure 2.2 illustrates the GPU compute unit, L2 cache, and DMA engines are connected to other parts of a computer system. GPUs use a PCI Express link (PCIe) to connect to CPU and CPU memory. One end of this link is connected to the IO hub located on the motherboard/CPU chip, and the other end is connected to one or two DMA engine(s) located on the GPU. The link is formed by a group of up to 16 *lanes*, each with enough wiring to support bidirectional data transfers at the same time. The latest generation of PCIe, PCIe revision 3.0, can transfer data at a theoretical speed of 15.75 GB/s in each direction if all 16 lanes are utilized.

Although GPU programs are supposed to transfer data in bulk to GPU memory before operating on it, a feature introduced in later versions of CUDA, called *zero copy*, enables GPU threads to directly access (the remote) CPU memory [77]. However, to enable zero copy, the to-be-access locations of CPU memory must be pinned so that they are not paged out by the operating system.

Finally, the latest family of CUDA-enabled GPUs (i.e., Pascal) offers hardware demand-paging support which provides a programming convenience referred to as "unified memory", in which the address space of GPU is merged with that of the CPU to create a single virtual address space. This way, GPU programs are allowed to access data located in CPU memory without first copying them to GPU memory; underneath, the demand-paging hardware pauses the execution and waits for the GPU driver to copy the required data to GPU memory before resuming execution.

#### 2.2.2 GPU Software

A typical CUDA program consists of two parts: the main part of the program, which is executed on the host (the CPU), and the *kernel*<sup>5</sup>, called by the main program, which is executed on the GPU by a collection of *GPU threads*<sup>6</sup> in parallel. The host part uses CUDA API calls to send different commands to the GPU. These commands include kernel execution control (e.g. kernel launch), memory management (e.g. memory copy to/from GPU memory), error handling (e.g. querying the GPU to check whether the kernel has terminated with an error), etc.

The programmer configures the kernel to be executed by a given number of GPU threads. A maximum of 1,024 threads are grouped into *thread blocks*<sup>7</sup> as configured by the programmer. Each thread block is assigned to an SMX by a hardware scheduler. Threads within a thread block can synchronize using barriers provided by the GPU hardware. However, there exists no explicit support for inter-block synchronization.

Threads of a thread block are further divided into groups of 32, called *warps*. The threads in a warp execute in lock-step because the cores share the same instruction scheduler. As described earlier, thread divergence will occur if, on a conditional branch, threads of the same warp take different paths, which can lead to serious performance degradations. Inter-warp divergence does not negatively impact performance.

A limited number of thread blocks can be scheduled on the same SMX at each time. The thread blocks currently executing on an SMX are called *online* thread blocks. The *offline* thread blocks are put in a queue and scheduled on the SMXs only after the online blocks complete their execution. The number of online blocks on each SMX depends on the available resources of the SMX and the total resource requirements of the thread blocks. Assuming that an SMX has 64K registers, for instance, no more than 4 thread blocks can be scheduled on the same SMX at a time if the size of the thread block is 256 and each thread requires 60 registers.<sup>8</sup>

Figure 2.3 lists a trivial CUDA program that squares the values of an array. Lines 2-6 define the kernel, which is executed on the GPU; each thread squares the value of a single array element. Lines 9-26 are the code executed on the CPU. Line 14 allocates an array in GPU memory, and data is copied into the array at line 18. Line 19 launches the kernel to be executed by 32 GPU threads. An explicit synchronization function is called at line 20 which blocks host execution until the GPU kernel finishes. After the kernel terminates, the array is copied back to main memory at line 21, and the allocated space on the GPU is freed at line 25.

<sup>&</sup>lt;sup>5</sup>Kernel is called *program* in AMD/OpenCL's terminology.

<sup>&</sup>lt;sup>6</sup>GPU threads are called *work-items* in AMD/OpenCL's terminology.

<sup>&</sup>lt;sup>7</sup>Thread blocks are called *work-groups* in AMD/OpenCL's terminology.

<sup>&</sup>lt;sup>8</sup>4 thread blocks would require  $4 \times 256 \times 60 = 60K$  registers which is available in the SMX. 5 thread blocks, however, would require  $5 \times 256 \times 60 = 75K$  registers which is more than 64K registers available in the SMX.

```

1: //GPU part

2: __global__ void squareArray (float *a)

3: {

4:

int idx = threadIdx .x;

5:

a[idx] = a[idx] * a[idx];

6: }

7:

8: //Host part

9: int main(void)

10: {

float *a_h, *a_d;

11:

12:

int size = 32 * sizeof (float);

13:

a_h = (float *) malloc (size);

14:

cudaMalloc((void **) &a_d, size);

15:

16:

// Initialize host array ...

17:

18:

cudaMemcpy (a_d, a_h, size, cudaMemcpyHostToDevice);

19:

squareArray <<<1, 32>>> (a_d);

20:

cudaThreadSynchronize();

cudaMemcpy (a_h, a_d, size, cudaMemcpyDeviceToHost);

21:

22:

// Use the results ...

23:

24:

free(a_h);

25:

cudaFree (a_d);

26: }

```

Figure 2.3: A trivial CUDA application that squares the elements of an array

## Chapter 3

## **Related Work**

In this chapter, we present prior work related to our research. We focus on four different subareas:

- 1. GPU accelerated applications

- 2. Core data structures developed for GPU applications

- Compile-time or runtime systems that improve the performance of existing GPU applications through various optimizations techniques

- 4. GPU performance models and studies that characterize GPU performance

### 3.1 GPU accelerated applications

Many studies have reported significant speedups when porting CPU applications to GPUs. These applications stem from a wide array of areas, including: bioinformatics [62], computational finance [15], computational fluid dynamics [93], data mining [20], defence and intelligence [19], electronic design automation [98], imaging and computer vision [25], material science [18], medical imaging [94], molecular dynamics [110], numerical analysis [7], physics [36], quantum chemistry [102], oil and gas/seismic [1], structural mechanics [84], visualization and docking [57], and weather and climate [57]. Table 3.1 summarizes a number of applications from these areas along with their achieved speedups over the corresponding CPU implementations.

In addition to algorithm changes that are required to make an application massively parallel, programmers also need to fine-tune the applications to take into account the underlying micro-architectural characteristics of the GPU in order to be able to achieve good performance. For example, Kumar et al. needed to coalesce accesses to GPU memory to improve the performance of the Expectation Maximization (EM) algorithm [52]. They observed that coalescing memory requests enabled the EM algorithm to exhibit higher computational throughput.

| Application and Organization                                 | Speed-up | Software env.  | Testbed Hardware environment            |

|--------------------------------------------------------------|----------|----------------|-----------------------------------------|

| Fast Seismic Modeling [1]                                    | 10X      | CUDA           | GPU: NVIDIA Tesla S1070                 |

| TOTAL, avenue Larribau                                       |          |                | CPU: Ten Intel Xeon quad-core 2.0GHz    |

| Visualization of ISO-surface Extraction [8]                  | 2X       | OpenGL         | GPU: NVIDIA QuadroFX Go 1400            |

| Nancy Universite                                             |          |                | CPU: Intel Centrino 2GHz                |

| Support Vector Machine [16]                                  | 70X      | CUDA           | GPU: NVIDIA Geforce 8800 GTX            |

| Can Tho University                                           |          |                | CPU: Intel Core 2 2.6 GHz               |

| Decision Trees and Forests [89]                              | 100X     | CUDA           | GPU: NVIDIA GTX 280                     |

| Microsoft Research, UK                                       |          |                | CPU: Intel Core 2 Duo 2.66 GHz          |

| Particle Swarm Optimization [121]                            | 11X      | CUDA           | GPU: NVIDIA GTX 8600                    |

| Peking University                                            |          |                | CPU: Intel Core 2 Duo 2.2GHz            |

| Genetic Programming [87]                                     | 13X      | CUDA           | GPU: NVIDIA GTX 8800                    |

| Universit Lille Nord de France                               |          |                | CPU: Intel Core 2 Duo 2.6 GHz           |

| Genetic Programming for Bioinformatics [54]                  | 7.6X     | RapidMind [70] | GPU: NVIDIA GTX 8800                    |

| University of Essex                                          |          | of a strait    | CPU: Intel 6600 2.40 GHz                |

| Data Mining High-throughput Screening Data [58]              | 43X-212X | CUDA           | GPU: NVIDIA GTX 280                     |

| ChemExplorer Co. Ltd                                         | -        |                | CPU: 4 Intel Xeon 5120 1.86 GHz         |

| K-Means [114]                                                | 14X      | CUDA           | GPU: NVIDIA GTX 9600                    |

| Know-Center, Graz                                            |          |                | CPU: Intel Core 2 Duo E8400 CPU         |

| Digital Forensics [69]                                       | 4.6X     | CUDA           | GPU: NVIDIA GTX 8800                    |

| University of New Orleans                                    |          |                | CPU: Two AMD Opteron 2218 2.6GHz        |

| Back-Propagation Neural Network [90]                         | 63X      | CUDA           | GPU: NVIDIA Tesla C1060                 |

| University of Tecnolgica Metropolitana                       | 0011     | CODIT          | CPU: Intel Core2 Duo E6750 2.66GHz      |

| Molecular Dynamics Simulations [60]                          | 19X      | CUDA           | GPU: NVIDIA GTX 8800                    |

| Nanyang Technological University                             | 1771     | CODIT          | CPU: AMD Opteron 2210 1.8 GHz           |

| K-Means [38]                                                 | 40X      | CUDA           | GPU: NVIDIA GTX 8800                    |

| Jilin University                                             | 4028     | CODIT          | CPU: Intel Pentium D 965 3.7 GHz        |

| Molecular Dynamic Simulation [24]                            | 700X     | CUDA           | GPU: NVIDIA GTX 280                     |

| Stanford University                                          | /00/1    | CODIT          | CPU: Intel Core 2 Duo 2.66 GHz          |

| Earthquake Modeling [49]                                     | 25X      | CUDA           | GPU: NVIDIA GTX 8800                    |

| Universite de Pau et des Payse de l'Adour                    | 2371     | CODIT          | CPU: Intel Xeon E5345 2.33 GHz          |

| Quantum Monte Carlo [4]                                      | 6X       | CUDA           | GPU: NVIDIA GTX 7600                    |

| California Institute of Technology                           | 011      | CODIT          | CPU: Intel Pentium 4 3GHz               |

| Smith Waterman for Scanning of Sequence Databases [59]       | 3.5X     | CUDA           | GPU: NVIDIA GTX 9800                    |

| University of Warsaw                                         | 5.571    | CODIT          | CPU: Conventional CPU                   |

| Ultra-fast FFT Protein Docking [86]                          | 45X      | CUDA           | GPU: NVIDIA GTX 285                     |

| INRIA Nancy                                                  |          | CODIT          | CPU: Intel Xeon quad-core 2.3 GHz       |

| Density Functional Calculations [112]                        | 10X      | CUDA           | GPU: NVIDIA GTX 8800                    |

| Nagoya University                                            | 1024     | CODIT          | CPU: Intel Core2 Duo 3.0 GHz            |

| QM/MM-QMC Simulation [100]                                   | 23.6X    | CUDA           | GPU: NVIDIA GTX 275                     |

| Japan Advanced Institute of Sci. and Tech.                   | 25.01    | CODA           | CPU: Intel Core i7 920 2.66 GHz         |

| Biomolecular Simulations in the Centisecond                  | 90X      | CUDA           | GPU: NVIDIA GTX 295                     |

| Timescale [120]                                              | JUA      | CODA           | CPU: Two Intel Xeon quad-core 2.83 GHz  |

| University of Massachusetts                                  |          |                | CI C. Two Intel Acon quad core 2.05 OIL |

| Single-cluster Algorithm for the Simulation of the Ising     | 7.9X     | CUDA           | GPU: NVIDIA GTX 285                     |

| Model [51]                                                   | 1.92     | CODI           | CPU: Intel Xeon W3520 2.67GHz           |

| Tokyo Metropolitan University                                |          |                | CI C. Intel Acon (05520 2.070112        |

| Numerical Solution of Stochastic Differential Equations [42] | 675X     | CUDA           | GPU: NVIDIA Tesla C1060                 |

| University of Silesia                                        | 5,51     |                | CPU: Intel Core2 Duo E6750              |

| Fast FEM Deformation Simulation [61]                         | 4X       | CUDA           | GPU: NVIDIA GTX 8800                    |

| University of Macau                                          | 723      | CODI           | CPU: Intel Core2 Quad 2.0GHz            |

| Nonequispaced Fast Fourier Transform [92]                    | 85X      | CUDA           | GPU: NVIDIA GTX 8800                    |

| King's Coll. London                                          | 0.57     | CODA           | CPU: Intel Xeon dual-core 2.33 GHz      |

| King s Coll. Lolidoli                                        | L        | 1              |                                         |

Table 3.1: Studies on porting applications to GPUs with the claimed speedup achieved.

In the process of developing a data mining translation system on GPUs, Ma et al. used GPU shared memory spaces to dramatically improve the application's overall performance [67]. They found, however, that since the shared memory is small, using it can be challenging.

Govindaraju et al. focused on the use of GPUs caches in a sorting algorithm [31]. They realized that by tiling the application's memory access pattern, the small GPU caches could be utilized more efficiently. This technique significantly reduces the number of GPU memory accesses and improves the performance of the sort algorithm by 2-30x and 6-25x over prior GPU-based and CPU-based sorting algorithms, respectively.

Yudanov et al. observed that the serialization effect of thread divergence hurts the performance of GPU applications noticeably [113]. The authors tracked down and resolved the source of branch divergence in a Simulation of Neural Networks application and achieved 9X speedup compared to a baseline CPU implementation.

Yang et al. designed and implemented a Linpack benchmark on a petascale CPU/GPU supercomputer system [109]. They observed that one of the primary bottlenecks was the bandwidth limitation of the CPU-GPU link. A simple software pipelining technique was used to overlap execution with host-GPU data transfers so as to better distribute data transfers over time and reduce the time the kernel spent waiting for the data. Moreover, they realized that finding the optimal configuration regarding the distribution and size of each task/data-transfer was challenging and could have benefited from an adaptive framework that does this automatically.

#### **3.2** Work on core data structures

Performance of GPU applications often depends critically on the choice of data structure used to store data. A key challenge is that data structures used in GPU applications are typically accessed by 1000's of active GPU threads; even minor access inefficiencies thus translate into substantial performance degradation.

Regular data structures like arrays and matrices are the data structures of choice when the objective is to exploit as much of the computation power and memory bandwidth of GPUs as possible: accesses to these data structures (i) can often be coalesced into fewer (physical) memory transactions, (ii) seldomly cause thread divergence, and (iii) often do not require synchronization.

A large body of work has presented GPU-based applications that use arrays and matrices in their implementations (e.g., [7, 12, 21]). Because matrix multiplication is one of the more important operations in scientific computing, various studies have looked at ways to improve the way matrices are stored and operated on. Hall et al. looked at how matrices can be stored and accessed so as to have a high cache hit rate [33]. Dziekonski proposed a novel way to store sparse matrices on GPUs to achieve high bandwidth memory accesses [17].

Irregular data structures<sup>1</sup>, like trees and hash tables, on the other hand, are often avoided by the GPU commu-

<sup>&</sup>lt;sup>1</sup>Irregular data structures are data structures that their access pattern is data-dependent, and statistically unpredictable.

nity because (i) it is significantly harder to coalesce accesses to these data structures, (ii) costly synchronization is often required for shared accesses and, (iii) thread divergence is more likely (imagine two neighbor GPU threads traversing a tree to find two different elements at different heights). Despite these potential issues, there are cases where such irregular data structures nevertheless improve application performance, primarily because they are a great fit for the application's needs.

Irregular data structures that have been designed for GPUs can be grouped into one of the three categories: (*i*) *mutable GPU-based structures*, those that are kept in GPU memory and can be accessed and updated incrementally, (*ii*) *immutable GPU-based structures*, those that are kept in GPU memory but cannot be updated incrementally but are bulk-built and need a full rebuild to be updated, and (*iii*) *CPU-based structures*, those that are kept in CPU memory but are accessed by GPU cores remotely over the PCIe bus (mostly read-only accesses).

**Mutable GPU-based structures:** only few existing designs fall into this category. MapCG is a GPU-based MapReduce runtime system that uses a hash table to store key-value pairs [37].

MapCG has been shown to achieve 1.6-2.5X performance speedup compared to earlier implementations that used arrays to store the key-value pairs, which is perhaps surprising given the fact that a MapReduce application can generate many key-value pairs with duplicate keys and thus face a highly contended access pattern to the hash table.

In chapter 6, we present our own design of a hash table which also falls into this category. This hash table was designed primarily for key-value pairs. It (i) accepts variable-length key-value pairs, (ii) groups pairs with duplicate keys on-the-fly and, (iii) keeps the hash table in GPU memory, and while doing that stays operational (and with retained efficiency) even when the hash table contents grow larger than GPU memory.

**Immutable GPU-based structures:** several hash table and most tree designs fall into this category[22, 39, 45, 76, 103, 34, 83, 99, 118]. Pan et al. use a hash table for a k-nearest neighbor computation [83]. The hash table uses locality sensitive hashing (that hashes similar items to similar buckets) to cluster items that are similar to each other. Their implementation achieves more than 40X speedup over a single-core CPU based implementation.

Alcantra et al. [3] described various techniques to make the hash table more efficient on GPUs. They describe various potential structures for a hash table and analyze insert and lookup operations on each. As part of their evaluation, they reported that the hash table they built offers random access at a higher rate than binary searches through sorted arrays, despite the uncoalesced accesses inherent to hashing.

Foley et al. used a KD-tree to improve the performance of the Raytracer application [23]. They describe that even though the matrix-like grid is more "GPU-friendly", it is a suboptimal data structure for this application when rays have certain attributes. Foley claimed that using a KD-tree provided a speedup of 8 over previous implementations using the grid data structure.

Sharp described a way to implement a decision tree on GPUs, and showed how it can accelerate an object recognition algorithm [89]. Their implementation achieved 100X speedup over the corresponding CPU implementation.

Luo et al. presented a highly parallel GPU-based implementation of R-trees [64]. R-tree is an index data structure for the efficient management of spatial data. They reported an average speedup of 25 over a CPU-based implementation of the same application.

**CPU-based structures:** More recent scalable hash table designs fall into this category. Stadium hashing proposes a hash table design where the hash table itself is located in a pinned portion of CPU memory, where it is directly accessed by GPU threads [47]. However, a compact indexing data structure is stored in GPU memory which is used to minimize the number of accesses to CPU memory by having one fingerprint hash token for each item stored in the hash table and having every operation on the hash table first consult the index data structure before accessing the hash table. For instance, on an insert, the GPU thread first uses the index data structure to find an empty bucket, and only then will it access CPU memory to store the data. Stadium hashing reports 2-3 times faster operations over an existing GPU parallel hashing.

Mega-KV is a CPU-based in-memory key-value store for distributed systems that uses a hash table to store the key-value pairs [116]. Mega-KV runs on a single node and stores key-value pairs that are sent to it from other nodes. The hash table is accelerated by a GPU-based index table. Similar to the Stadium hashing's approach, Mega-KV uses the GPU only for the heavy-lifting part of the operations (e.g., scanning the hash table for an empty bucket during an insert, or finding a bucket item during a lookup). However, the actual data is kept on and accessed in CPU memory.

Unlike the solution we present in chapter 6, neither Stadium hashing nor Mega-KV handle key-value pairs with duplicate keys even though they are common in Big Data analytics applications. They both store pairs with duplicate keys as if they are pairs with different keys that happen to map to the same buckets.

### 3.3 Runtime and Compiler-assisted Systems

A number of runtime and compiler-assisted systems have been designed for GPUs with the goal of improving the performance of existing applications. Two classes of these systems that are of particular interest to us are (i) CPU-GPU communication management systems with the objective of automating and/or optimizing CPU-GPU data communication and (ii) GPU memory optimization systems with the objective of optimizing the memory accesses of existing applications (e.g. by coalescing memory accesses or by exploiting GPU's fast shared memory).

We present two systems in chapters 4 and 5 that fall under this category. The first system, BigKernel, (i) automates and optimizes CPU-GPU communications and (ii) optimizes GPU memory accesses. The second system, S-L1, implements a level-1 cache system entirely in software to improve the performance of GPU memory subsystem.

#### 3.3.1 CPU-GPU Communications Management Systems

Managing CPU-GPU data communications is a well-known challenge both from a programmability and from a performance point of view. Most prior work addresses this challenge only from a programmability point of view [27, 56, 108], but some also consider performance, which is more closely related to our research goals [55, 119].

Jablin et al. automates CPU-GPU communication to increase GPU programming convenience, however without having the objective of improving the performance [41]. They used compiler technology to statically analyze the code of an application and insert appropriate runtime library functions into its code to transfer data to/from GPU memory. To do this, the data structures being used by the kernel are determined based on the kernel's arguments. Next, type-inference is used on each data structure to statically determine if the data structure contains pointers or non-pointer data. If it contains non-pointer data, it is simply transferred to GPU memory before the corresponding kernel is invoked. If the data structure contains pointers, however, not only it will be transferred to GPU memory, but the data structure being pointed to by those pointers will also be transferred to GPU memory.

The static type-inference scheme the authors use makes the scheme inapplicable for applications with recursive data structures. Furthermore, this work does not address the difficulty in executing kernels that process datasets larger than the size of GPU memory. In other words, the programmer herself needs to split the input data into smaller chunks – and call the kernel function multiple times, each time to process a different chunk of data – and make sure that the total size of data required by each kernel invocation does not exceed the size of GPU memory.

In a more recent work by the same group, Jablin et al. designed another system to automatically manage recursive data structures without static analysis [40]. They realized that moving toward a runtime approach (as opposed to the static type-inference method they used in their previous work) improves the applicability of the data management system for a wider range of GPU applications. Similar to the previous work, this new system determines the data structures used based on the kernel arguments. These data structures are scanned before kernel invocation to find potential pointers. For each potential pointer found, the pointee data structure is added to the list of data structures that should be transferred to GPU memory and also scanned for potential pointers as well (to identify recursive data structures).

The new system also does not handle datasets larger than the size of GPU memory and puts the burden of

splitting and size-checking the data structures on the programmer. Additionally, it is assumed that the pointers used by an application are always stored as direct pointers (i.e., immediate address) and are not displacements (e.g. basePtr + displacement) or indexes (e.g. basePtr[index]). These limitations, for example, make the system incapable of handling applications that access a hash table since hash tables are typically indexed into using hashes of other data values.

VAST is another CPU-GPU communication management system that provides OpenCL programs the illusion of having a larger GPU memory space [55]. Based on the available GPU memory, VAST partitions the data parallel workload into chunks and extracts the working set required for the computation by first running a variation of the kernel code, called *inspector*, that compiles a list of those pages of memory being accessed by GPU threads during the computation and sends the list to the CPU. The CPU then transfers those pages to GPU memory where the data is accessed through a page table. A downside of this approach is that each data access is transformed to go through the page table before accessing the actual data, which incurs extra memory accesses. Nevertheless, the authors report an average speedup of 2.6 over the baseline CPU implementations of benchmark applications.

Komoda et al. proposed a library for OpenCL that automatically overlaps computation with data communication [50]. Using this library, programmers describe the memory usage pattern of their applications in the form of a graph abstraction called Stream Graph [96]. In this abstraction, kernel(s) and I/O streams (e.g. a stream of data in CPU memory) are nodes of the graph and communication paths amongst the nodes are the edges. When applied to four benchmark applications, the overlapped computation and communication improves the performance of the applications by an average of 58%. However, the programmer is still required for splitting the data into smaller chunks and also is required to provide information such as the size of the data structures being transferred.

Pai et al. propose a system that automates CPU-GPU memory management and also improves the performance of CPU-GPU communication by not transferring redundant data between CPU and GPU [82]. The authors observed that other systems that automate CPU-GPU data transfers often transfer data that is not used at all or transfer a data item multiple times. To reduce the volume of data transfers to what is actually necessary, this system uses a coherence model approach where data is transferred – from CPU to GPU or from GPU to CPU – only if it is does not exist at the destination or if its available version is stale. Using this system, a set of benchmark applications exhibit an average speedup of 1.29 over the system proposed by Jablin et al., described above [41]. The system proposed by Pai et al. does not overlap computation and data communication.

Finally, Nvidia recently equipped its GPUs with a demand-paging hardware mechanism, enabling a single virtual space across CPU and GPU memories [79]. This single address space allows a GPU program to access data located in CPU memory without first having to explicitly copy it to GPU memory; the demand-paging hardware will pause the execution if the accessed data is in CPU memory and transparently copy it to GPU memory before resuming the execution. A preliminary study on this demand-paging support, however, report on

noticeable performance inefficiencies, suggesting that some optimizations are still needed before the mechanism will perform reasonably well for different types of applications [119].

#### **3.3.2 GPU Memory Optimization Systems**

Despite having high theoretical memory bandwidth, GPU memory is often unable to efficiently satisfy the high number of concurrent memory requests made by running GPU threads. Two ways this issue has been addressed are (i) coalescing memory accesses to GPU memory and (ii) using GPU shared memory or L1 caches to cache the data and, consequently, reduce the number of memory accesses that need to be serviced by GPU memory.

CUDA-lite is an enhancement to CUDA developed by Ueng et al. that uses shared memory as a fast scratchpad to reduce the number of accesses to GPU memory [101]. In CUDA-lite, a source-to-source translator is used to transform the code of a loop-based kernel<sup>2</sup> so it can achieve optimized tiling of GPU memory data. More precisely, a tile of data, which is predicted to be used in future iterations of the kernel's loop, is read in a coalesced fashion, from GPU memory using a single memory transaction and stored in the shared memory from where it is then accessed more efficiently. To predict which data is used in future iterations of the kernel's loop, the programmer has to annotate the source code to specify the loop configuration (e.g. start and end iterations) and the location of the data item. They were able to obtain 2-17X speedup over applications with non-coalesced memory accesses [101].

Yang et al. proposed a number of compiler optimizations to increase the effective utilization of GPU memory bandwidth and improve the efficiency of thread parallelism on the GPU devices [111]. Similar to CUDA-lite, they load data tiles (that are going to be used in future loop iterations) from GPU memory in a coalesced fashion and store them in the shared memory for later use. Additionally, to improve thread parallelism efficiency, threads in different thread blocks are analyzed for their memory access patterns (at compile-time) and those with sharing locality are merged into one thread, enabling data reuse through registers and shared memory.

Zhang et al. conducted a comprehensive study on the difficulties and benefits of removing irregularity from memory accesses [115]. The authors noted that since irregular memory accesses by the threads of a warp are often to disjoint locations of memory, their performance is significantly lower than for coalesced memory accesses. To address this, the authors proposed a software-based system in which, at runtime, the CPU reorders the data of irregular data structures before sending them to the GPU to co-locate the data items that will be accesses at the same time by the threads of a warp, causing the accesses to GPU memory to be coalesced. The downside of this work is that the CPU (which is often less efficient for parallel workloads) is required to partially run the kernel code to extract the irregular addresses the GPU threads will access, thus limiting the performance gains.

<sup>&</sup>lt;sup>2</sup>A kernel that does the core of the computation inside a loop.

Nevertheless, applying their system on a variety of applications, speedups between 1.07 and 2.5 were reported.

Finally, CudaDMA provides a library that allows the programmer to copy data to shared memory and use the data from there [6]. They adopt a *producer-consumer* approach in which threads executing a kernel are divided into two groups: (i) *producer threads* whose only job is to load the data from GPU memory into shared memory and (ii) *consumer threads* that will do the computation using the data in shared memory. Producer and consumer threads are put in different warps so as to avoid thread divergence. To employ CudaDMA, the programmer uses the provided APIs to determine producer and consumer threads and also to register the data that needs to be loaded to shared memory. The downside of this work is that the programmer is responsible for setting the number of producer and consumer threads, and assigning the proper size of shared memory to different threads which is a non-trivial task. Speedups of between 1.15 and 3.2 were reported when applying CudaDMA on several kernels from scientific applications.

### 3.4 GPU Performance Characterization

GPU performance models and other studies that characterize GPU performance are often used to help GPU programmers predict and optimize their applications. These studies often analyze many of the micro-architectural characteristics of a GPU (sometimes obtained through reverse-engineering efforts) and provide an in-depth understanding as how each component of a GPU can become performance-limiting. This section describes some of the more important studies that characterize and predict GPU performance.

Wong et al. used micro-benchmarking to understand the architectural characteristics of a modern GPU [106]. The collected measurements are useful to those wishing to model GPU performance, since most of the GPU micro-architectural characteristics are not publicly disclosed by the GPU vendors. For example, while there is no information on the existence of TLBs for GPU memory in GPU documentation, this work reports on the measured effect of two TLB levels for GPU memory.

One of the more interesting (and for us relevant) performance modeling efforts is the one by Gomez et al., who modelled asynchronous data transfers between host and GPU memory [30]. Based on the execution time of the applications and the time it takes to transfer data between host and GPU memory, their model estimates the potential performance improvement that would be obtained from overlapping computation and data communication. In addition, the model enables programmers to determine how best to partition the application's computation.<sup>3</sup>

Baghsorkhi et al. propose an analytical model to predict the performance of a GPU kernel executing on a generic GPU architecture based on its (a) compute-to-memory-access ratio, (b) coalesced memory accesses,

<sup>&</sup>lt;sup>3</sup>Given an application which processes D data records that can be processed independently, a programmer could decide to cluster them into n segments. Thus, each of the segments will contain  $\frac{D}{n}$  of the data records.

(c) thread divergence ratio, and (d) shared memory usage of each thread block [5]. These four criteria are sufficient to determine the performance of a GPU application when its memory footprint is smaller than GPU memory size.

Others have also studied the characteristics of GPU memory and GPU caches [26, 106]. Jia et al. characterized GPU L1 cache locality and provided a taxonomy for reasoning about different types of access patterns and how they might benefit from L1 caches [43]. Tore et al. provided insights into how to tune the configuration of GPU threads to achieve higher cache hit rates. They also showed how the L1 impacts the performance of a handful of simple kernels [97].

Table 3.2 lists other studies that characterize GPU performance.

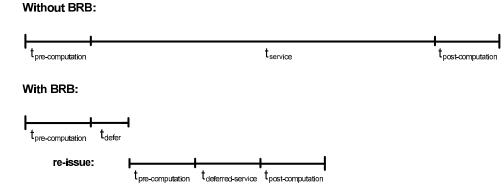

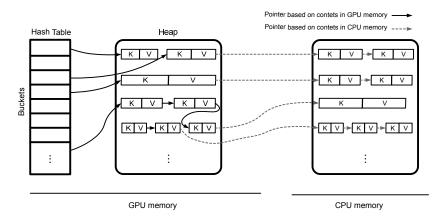

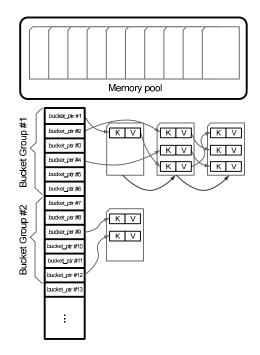

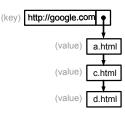

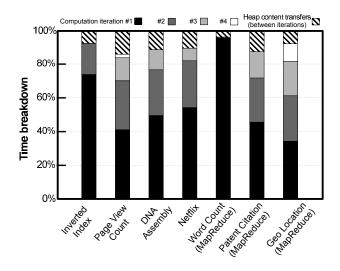

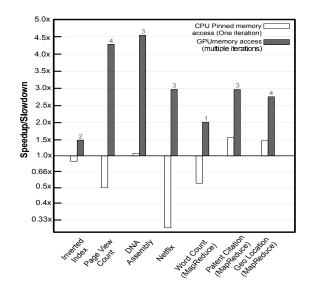

| Description                                                            | Organization                         |